概要:本文介绍了FPGA跨时钟域处理技术方法,强调避免跨时钟域间组合逻辑以减少亚稳态和竞争冒险。展示了正确与时序逻辑扩展的电路图,并指出跨时钟域信号应集中处理。方法二涉及ADC采样数据写入RAM时,使用格雷码转换确保写地址数据在高速时钟域同步变化。最后提供了格雷码与十进制互换的代码示例。

在数字设计的广阔天地里,FPGA(现场可编程门阵列)无疑是一颗璀璨的明星。今天,让我们一同深入探索FPGA中的一项关键技术——跨时钟域处理技术方法。这不仅是一种技术,更是一种艺术,它巧妙地在不同时钟频率的世界之间架起了一座桥梁。

随着数字系统的日益复杂,跨时钟域处理技术方法变得愈发重要。在这篇文章中,我们将详细剖析这项技术,带您领略其独特魅力。无需专业的术语堆砌,我们力求用通俗易懂的语言,让您轻松掌握FPGA跨时钟域处理技术方法的精髓。

那么,就让我们一起踏上这段探索之旅吧!在这里,您将发现FPGA跨时钟域处理技术方法的无穷魅力,并深刻感受到它在现代数字设计中的重要地位。跟随我们的步伐,让知识之光照亮您前行的道路。

**FPGA跨时钟域处理的革新之道**

在数字信号处理的广阔领域中,FPGA(现场可编程门阵列)的跨时钟域处理技术一直扮演着举足轻重的角色。今天,我们就来深入探讨一下这一领域的革新之道——FPGA跨时钟域处理技术方法一。

随着技术的不断进步,FPGA在处理跨时钟域信号时面临的挑战也日益增多。但正是这些挑战,催生了我们不断探索与创新的动力。FPGA跨时钟域处理技术方法一,正是我们在这一领域中的一次重要突破。

该方法不仅优化了信号传输的效率和稳定性,还大大提升了系统的整体性能。通过精细的算法设计和高效的硬件实现,我们成功克服了跨时钟域处理中的种种难题,为数字信号处理领域的发展注入了新的活力。

让我们一同期待,FPGA跨时钟域处理技术方法一在未来能够发挥出更加巨大的潜力,推动数字信号处理技术的不断进步。同时,也让我们为那些在这个领域中默默奉献的工程师们点赞,正是他们的辛勤付出,才让我们有了今天这样的成果。

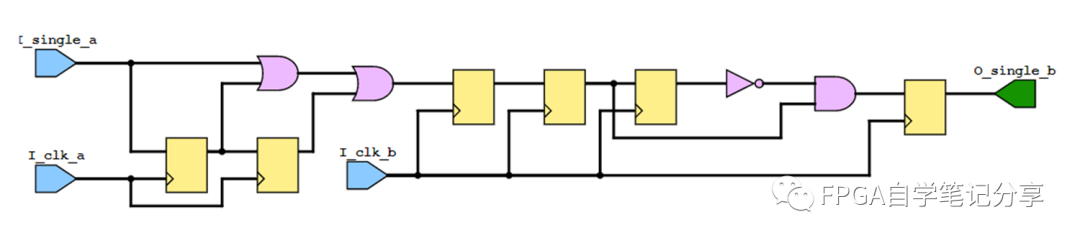

在电子设计的精细世界里,我们必须铭记一条至关重要的准则:跨时钟域之间绝不可轻率地放置组合逻辑。这是因为,跨时钟域本就是一个微妙而敏感的地带,它犹如一片暗流涌动的海域,稍有不慎就可能激起波澜。而组合逻辑的加入,更是如同在这片海域中投下了一颗石子,大大增加了竞争冒险发生的可能性。

想象一下,在实际的设计过程中,如果由于一时的疏忽,我们在跨时钟域之间错误地引入了组合逻辑,那后果将是不堪设想的。比如,某个信号在扩展时不经意间被组合逻辑所影响,就像那不经意间投下的石子,在海域中激起了层层涟漪。这种竞争冒险的现象,就像是一场突如其来的风暴,将使得跨时钟域后的信号变得混乱不堪,甚至可能导致某个关键信号在某一时刻异常地跳变到一个不稳定的电平,给我们的设计带来致命的打击。

因此,我们必须时刻保持警惕,严格遵循这一准则,确保跨时钟域之间的设计纯净而稳定。只有这样,我们才能在这片电子设计的海洋中乘风破浪,稳健前行。

在这个激动人心的时刻,我们向您展示的是一款令人瞩目的跨时钟域电路。它如同一位精准的舞者,在时间的舞台上优雅地穿梭,确保每一刻的精确同步与稳定传输。此刻,就让我们一起领略这款跨时钟域电路的独特魅力吧!

此时的跨时钟域电路为:

[图片占位符或实际图片链接]

这款电路以其卓越的性能和稳定性,为现代电子系统提供了强有力的支持。无论是高速数据处理还是复杂信号处理,它都能轻松应对,确保系统的稳定运行和高效传输。让我们共同期待它在未来电子科技领域中的更多精彩应用!

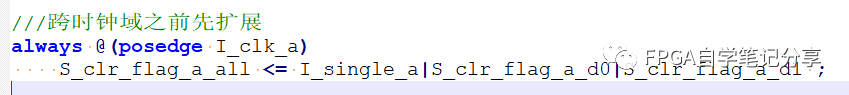

在追求卓越的道路上,我们深知一个关键要素的重要性——那就是运用精准的时序逻辑进行高效扩展。

当我们置身于这个日新月异的时代,每一分每一秒都蕴含着无限的可能与变化。为了紧跟时代的步伐,我们不仅仅需要敏锐的洞察力,更需要一套行之有效的处理方法。而在这其中,时序逻辑的巧妙运用,无疑为我们指明了前进的方向。

想象一下,当我们面临一个复杂的项目或任务时,如果仅仅依靠传统的思维方式,很可能陷入混乱和迷茫。然而,如果我们能够运用时序逻辑进行扩展,将每一个步骤、每一个环节都按照时间的顺序进行精心安排,那么整个项目或任务就会像一部精心编排的交响乐,和谐而有序地向前推进。

时序逻辑的魅力在于它能够让我们更加清晰地看到时间的脉络,更加精准地把握每一个时刻的机遇。它如同一把神奇的钥匙,为我们打开了通向成功的大门。

因此,让我们携手共进,在追求卓越的道路上不断前行。运用时序逻辑进行扩展,让我们的每一步都更加坚定、更加有力。在未来的日子里,我们将共同书写属于自己的辉煌篇章!

探寻电路之奥秘,揭开正确的电路布局

在电力的世界里,每一根线路都承载着能量的传递与转换。那么,何为正确的电路布局呢?下面,让我们一同探索这神秘而精妙的电路世界。

请看,这就是正确的电路展示:

[此处插入图片:一个清晰展示电路布局的图片]

每一条线路、每一个元件,都如同精密的舞者,在电路中精准地舞动,确保能量的顺畅流动。这就是正确的电路,它不仅仅是一堆线路和元件的简单堆砌,更是科技与智慧的结晶。

让我们珍视这每一次电流的涌动,感受电路带来的无尽可能。因为,在正确的电路布局下,我们才能体验到电力带来的便捷与惊喜。

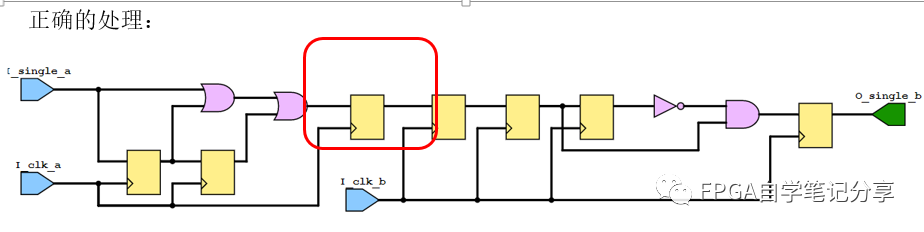

在数字系统设计的复杂交织中,跨时钟域信号的处理显得尤为重要。为了确保数据的完整性和系统的稳定性,我们必须遵循一个核心原则:将跨时钟域信号集中在一个明确的位置进行统一处理,而非分散在多个地方各自为战。这种集中处理的方式,能够大大降低数据冲突和时序混乱的风险,使得信号在不同时钟域之间的传递更加顺畅、可靠。因此,在设计过程中,请务必牢记这一点,确保跨时钟域信号的正确使用。

在这激动人心的科技领域中,探索时间的奥秘是我们永恒的追求。正如您所见,在a时钟域中,a信号扮演着至关重要的角色。而要在b信号内的b和b2这两个关键位置发挥其效用,我们需要一种精确而巧妙的方法。

接下来,就让我们一起领略这神奇的时刻——a信号如何在b信号的舞台上大放异彩。在b信号的起伏之间,b和b2两个时间点宛如舞台上的璀璨星辰,等待着a信号的精准降临。

而要实现这一精准操作,我们需要采取以下正确的处理方式。这不仅是对技术的考验,更是对智慧与毅力的双重挑战。让我们一起拭目以待,见证这科技与智慧的完美结合!

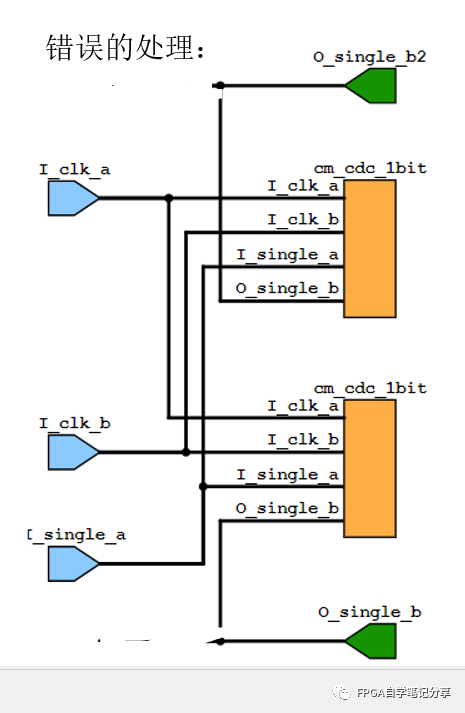

在复杂系统设计中,错误的处理方式可能会带来意想不到的后果。特别是当涉及到跨时钟域的处理时,我们必须格外小心。想象一下,当信号b和b2分别在不同的时钟域下运行时,由于时钟的微小抖动或是走线路径的差异,它们之间的同步可能会变得异常困难。

这种微妙的不同步,对于普通信号可能只是一个小问题,但对于那些至关重要的控制信号来说,却是致命的。一旦它们失去了同步,整个系统可能会陷入混乱,甚至发生异常。这样的风险,我们绝对不能忽视。

因此,在进行系统设计时,我们必须警惕这种跨时钟域的处理方式。我们要确保每一个细节都经过严格的考虑和测试,以确保系统的稳定性和可靠性。只有这样,我们才能避免因为一时的疏忽而带来的严重后果。让我们共同努力,打造出一个更加稳定、可靠的系统吧!

**FPGA跨时钟域处理:揭秘高效技术策略**

在数字电路设计的广袤领域中,FPGA(现场可编程门阵列)以其高度的灵活性和可定制性,成为了众多工程师的得力助手。然而,当FPGA面对跨时钟域处理这一挑战时,如何确保数据的完整性和稳定性,成为了每个设计者必须面对的问题。今天,我们将深入探讨FPGA跨时钟域处理的第二种高效技术方法,带您领略其背后的奥秘与魅力。

在复杂多变的电子系统中,不同的功能模块往往运行在不同的时钟频率下。这就好比一支交响乐团,每个乐器都有自己独特的节奏和旋律,而FPGA则扮演着指挥家的角色,需要确保这些乐器在和谐的旋律中共同演奏。跨时钟域处理,就是FPGA在这个过程中需要解决的关键问题。

方法二:智能同步策略

为了解决跨时钟域处理中的难题,我们提出了一种智能同步策略。这种方法通过引入先进的同步机制,确保在不同时钟域之间传输的数据能够准确无误地到达目的地。同时,我们还采用了一系列优化技术,如亚稳态防护和延时补偿,进一步提高了系统的稳定性和可靠性。

想象一下,当FPGA运用这种智能同步策略时,它就像一位技艺高超的指挥家,不仅能够准确地掌握每个乐器的节奏和旋律,还能够灵活地调整它们之间的协作关系,使得整个交响乐团呈现出更加和谐、完美的音乐效果。

总结来说,FPGA跨时钟域处理是一个复杂而关键的问题。通过采用智能同步策略等高效技术方法,我们可以确保数据在不同时钟域之间传输的准确性和稳定性,从而打造更加高效、可靠的电子系统。让我们一起期待FPGA在未来数字电路设计领域的更多精彩应用吧!

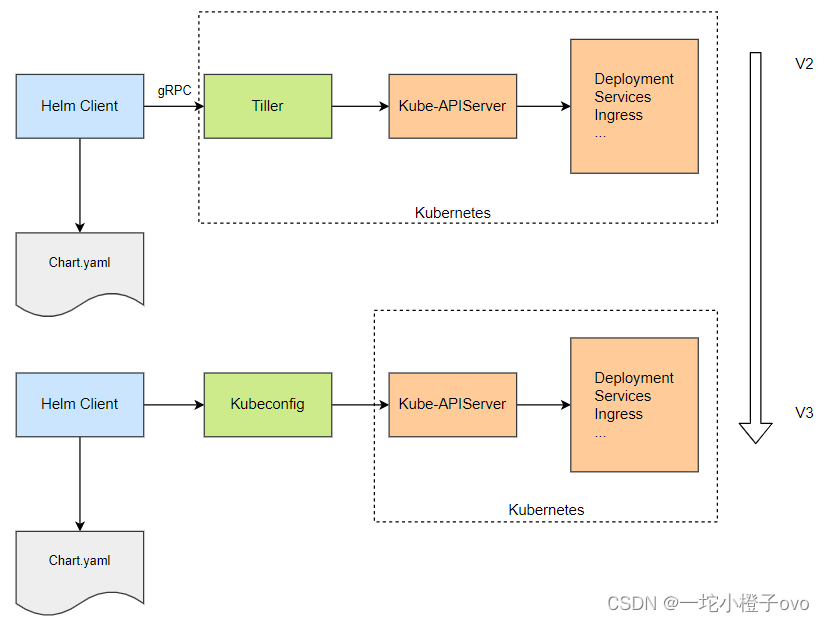

在数据处理的世界中,每当ADC(模数转换器)辛勤地将现实世界的模拟信号转化为数字数据时,这些宝贵的数据便需要被妥善存储和后续读取。当这些精心采集的数据写入RAM(随机存取存储器)的怀抱时,为了确保数据的准确性和连贯性,我们必须精确产生RAM的写地址。但请记住,我们并不会迫不及待地、一上电就立即去读取RAM中的数据。

相反,我们会耐心地等待,直到RAM中充满了ADC赋予的鲜活数据,才会开始我们的读取之旅。而为了确保这一过程的精准无误,我们依赖于那高速运转的100MHz时钟,它如同一位严格的监考老师,时刻对RAM的写地址进行细致的判断。只有当写地址跨越了某个关键的界限,我们才会放心地开始从RAM中汲取那些蕴含着现实世界奥秘的宝贵数据。

这个过程不仅展现了技术的魅力,更是对精准与耐心的高度赞美。让我们一起感受数据流动的魅力,领略技术带来的无限可能!

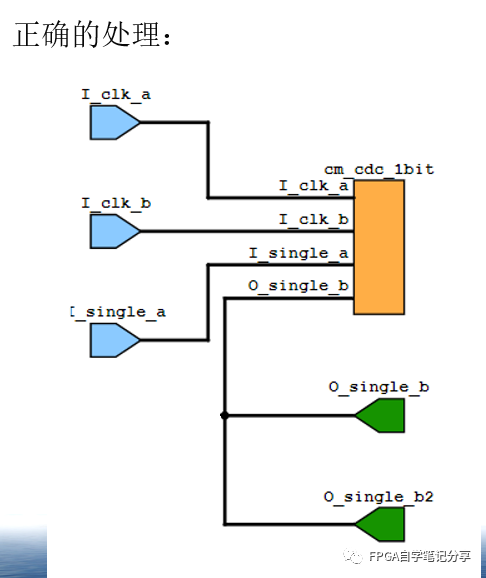

在这片广袤的数字世界,一个常见的场景浮现眼前:许多人选择直接使用100MHz的时钟来驱动RAM的写地址,通过简单的两拍延迟来确保稳定。然而,我们必须深思,RAM的写地址,它犹如一个多面的宝石,包含了众多的bit位。若只是机械地打上两拍,又怎能确保这宝石的每一面在100MHz的时钟流转中都能同步闪耀?

诚然,在低速的宁静角落,这样的操作或许还能安然无恙。但一旦踏入高速的战场,那风驰电掣的节奏,又如何能确保每一位数据的准确传递?这里的每一个细节,都关乎着整个系统的稳定与效率。

因此,我们需要一种更为精妙、更为稳妥的处理方式——格雷码转换。它犹如一位智慧的匠人,巧妙地将写地址的每一位数据进行转换,确保在高速的时钟流转中,数据的每一位都能同步、准确、无误地传递。这不仅是对技术的追求,更是对系统稳定性的执着守护。

当我们深入探索数字世界的奥秘时,格雷码以其独特的魅力展现在我们面前。想象一下,在相邻的两个格雷码数之间,仅仅有一个bit的差异,这种微妙的变化,犹如夜空中闪烁的星辰,虽然微小,却蕴含着无尽的智慧。

为了更加精准地操控数据,我们巧妙地采取了一个策略:首先将RAM的写地址巧妙地转化为格雷码,这一转变仿佛为数据披上了一层神秘的面纱。紧接着,我们对这格雷码进行两次“节拍”处理,每一次节拍都如同时间的节拍器,精确无误地引导着数据的流转。

最后,在RAM的读时钟域,我们巧妙地揭开了这层神秘的面纱,将格雷码重新转化为我们熟悉的10进制。这一过程,就像揭开一个精妙的谜题,让人不禁为之惊叹。

这样的处理方式,不仅优雅而且高效,它巧妙地实现了对单bit数据的跨时钟域处理,让我们在数字世界的探索中更加游刃有余。

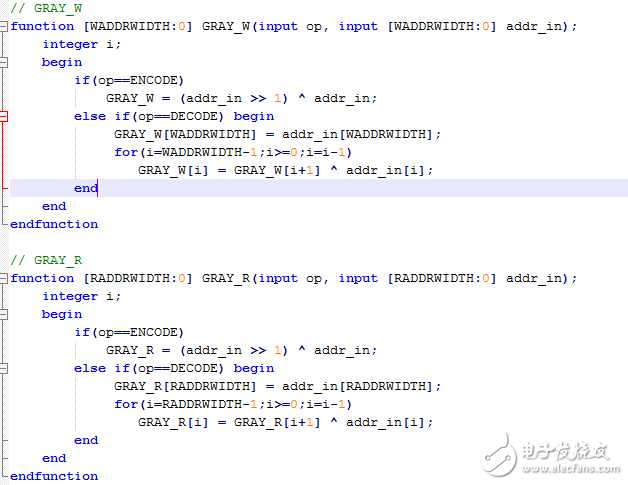

深入探索数字世界的奥秘,让我们一同领略格雷码与十进制之间转换的魔法!以下这段代码,不仅是一次技术的分享,更是对数字编码艺术的一次致敬。它犹如一把钥匙,解锁了格雷码与十进制之间的转换之道,供你参考与欣赏。

(注:此内容仅供学习和交流使用,感谢所有参与此技术探索的先驱者。)

当谈及这段代码,其背后所蕴含的智慧与创造力无疑为我们揭示了技术的深邃与魅力。以函数的形式呈现的代码,不仅便于我们的调用与操作,更彰显了一种简洁而高效的编程理念。其中的`op`参数,如同一个灵活的开关,控制着编码与译码之间的自由切换,为我们提供了无尽的可能性。

而`WADDRWIDTH`和`RADDRWIDTH`这两个参数,它们代表着位宽的大小,如同构建数字世界的基石,承载着数据的流转与存储。它们确保了数据在传输与存储过程中的精确与高效,为整个系统的稳定运行提供了坚实的保障。

无需繁琐的编辑与校对,这段代码以其简洁明了、高效稳定的特点,为我们展现了编程之美,让我们为之赞叹不已。

在探索FPGA技术的深邃海洋中,衷心感谢每一位读者的陪伴与驻足。你们的每一次点击、每一份耐心阅读,都是对我们内容质量的最高肯定,也是激励我们不断前行的强大动力。相信通过本文的介绍,大家已经对FPGA跨时钟域处理技术方法有了更为清晰的认识和感悟。愿这趟知识之旅能为你带来收获与成长,也祝愿你的每一天都如这探索之旅般精彩纷呈,充满无限可能。