概要:文章简述了Cortex R52内核Cache的操作,包括使缓存无效(invalidate)和清除(clean)等,并提供了操作指令和实例。介绍了Invalidate操作的两种方式:通过虚拟地址(VA to PoC)和通过集合/组(set/way),以及缓存行(Cache Line)的概念和作用,旨在指导优化缓存控制和程序性能。

在深入探索Cortex-R52内核的奥秘时,不得不提及其卓越的Cache管理功能。这里的Cache不仅仅是数据存储的仓库,更是提高处理速度和响应效率的关键。有时,为了确保系统的稳定性和数据的准确性,您可能会需要进行特定的Cache操作,比如使其失效(invalidate)或者彻底清除(clean)。

虽然Cortex-R52内核已经经过精心优化,大多数情况下无需直接操作Cache,但了解并掌握这些高级功能,无疑将为您在复杂的应用场景中提供更大的灵活性和掌控力。因此,本节内容将详细阐述这些操作的具体步骤和技巧,让您在面对未来可能的挑战时,能够游刃有余,轻松应对。

不论是invalidate还是clean操作,都将是您手中的得力工具,帮助您在系统性能与数据安全之间找到完美的平衡点。现在就跟随我们一起,深入了解这些精彩的功能吧!

掌控缓存之力:深入操作Cache的指令

在这个数字信息的海洋中,Cache(缓存)如同一位精明的领航员,默默引导着数据的流向,确保系统的高效运行。而掌握操作Cache的指令,就如同获得了与这位领航员直接对话的钥匙,让您能够精准地操控数据的流动,从而释放出系统的无限潜能。

当您掌握了这些指令,您将能够:

1. 精准控制缓存数据:不再让无关紧要的数据占用宝贵的缓存空间,让真正重要的数据得以快速加载,提升用户体验。

2. 优化系统性能:通过合理管理缓存,减少不必要的磁盘读写操作,降低系统负载,提升整体性能。

3. 实现高效的数据交换:Cache作为数据交换的桥梁,通过操作指令的精确控制,可以实现数据在不同层级之间的快速传输,提高数据处理效率。

在这个过程中,您不需要担心复杂的配置和繁琐的操作。我们的指令设计简洁明了,易于上手,让您能够轻松掌握Cache的奥秘,成为数字世界的掌控者。

所以,不要犹豫,快来掌握这些操作Cache的指令吧!让您的系统更加高效、稳定地运行,为您的业务发展提供强有力的支撑。

深度探索ARM Cortex-R52内核:掌握Cache操作的关键

在高性能计算的领域中,对缓存(Cache)的精细操作是确保系统流畅运行、提升数据处理效率的关键所在。特别是在ARM Cortex-R52这样的先进内核上,对Cache的管理与操作更是显得至关重要。

为了帮助您更好地掌握ARM Cortex-R52内核中Cache的操作技巧,我们强烈推荐您参考官方发布的ARM Cortex-R52内核技术手册。这本手册详细阐述了ARM Cortex-R52内核的架构特点、指令集、内存管理等方面,特别是针对Cache的管理与操作,给出了详尽的指导和建议。

无论是开发嵌入式系统、实时操作系统还是其他高性能计算应用,深入了解并正确操作ARM Cortex-R52内核的Cache,都将为您的项目带来显著的性能提升和稳定性保障。让我们一起翻开这本技术手册,共同探索ARM Cortex-R52内核的奥秘,掌握Cache操作的关键,迈向更高层次的技术巅峰!

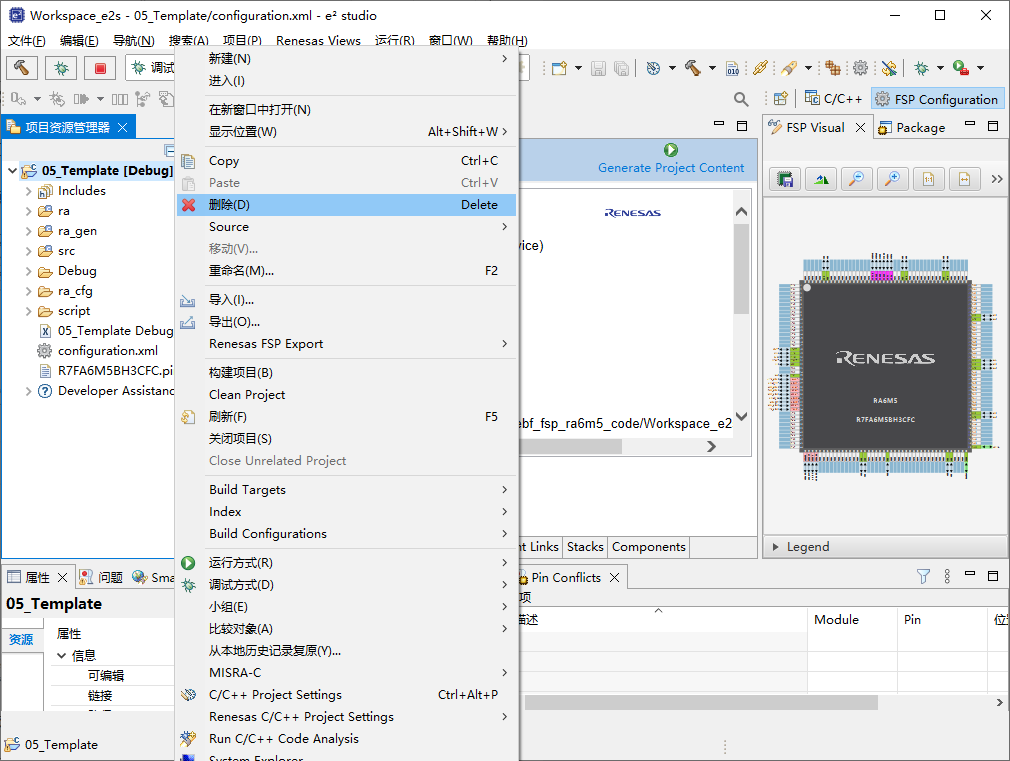

3.2.9 c7 系统操作:超越想象的体验

当我们深入探讨c7系统操作时,我们不仅仅是在谈论一套技术或工具。我们是在探索一种全新的、前沿的、引领行业变革的体验。c7系统操作,凭借其高效、稳定、智能的特性,为用户带来了前所未有的便捷与畅快。

想象一下,您只需轻轻一点,c7系统便能迅速响应,满足您的各种需求。无论是数据分析、项目管理,还是资源调度,c7系统都能游刃有余,让您的工作流程更加顺畅、高效。

c7系统操作的强大功能不仅体现在其高效性上,更体现在其智能性上。它能够根据您的使用习惯和需求,自动调整优化设置,让您的操作更加便捷、舒适。同时,c7系统还具备强大的自我修复和更新能力,确保您的系统始终保持最佳状态。

在这个信息化、数字化的时代,c7系统操作无疑是我们迈向未来、追求卓越的得力助手。让我们一起感受c7系统操作带来的超越想象的体验吧!

(图片保持不变,继续展现c7系统操作的精彩瞬间)

它定义了缓存中连续的一组数据块,这些数据块在缓存中的存储和管理都是以缓存行为单位进行的。正是有了这样的精细管理和高效传递,我们的计算机才能在海量的数据海洋中快速定位、迅速响应,为我们带来流畅无阻的使用体验。

因此,当我们谈论缓存行时,我们不仅仅是在讨论一种技术细节,更是在探讨如何提升计算机性能、优化用户体验的重要策略。让我们共同期待,在未来的计算机世界中,缓存行将发挥更加重要的作用,为我们的工作和生活带来更多便利和效率。

在当今的高速运算世界里,处理器内部的缓存系统扮演着至关重要的角色。想象一下,缓存就像是一个个精心设计的"快速通道",它们被精心组织成一系列的缓存行,每行都承载着一定数量的关键数据。每当CPU渴望获取内存中的数据时,它都会首先向这些缓存"快速通道"发出询问。

如果幸运地,所需的数据正静静地躺在某个缓存行中,那么这一刻就被我们称为“命中”的辉煌瞬间。此时,CPU如同得到了金手指,可以直接从这条"快速通道"中闪电般地获取数据,而无需踏入繁忙的主存区域。

然而,若是数据并不在缓存之中,CPU就不得不亲自踏入主存的广袤领域,去亲自寻找那份它渴望的数据。这一过程,我们称之为“缓存未命中”的遗憾时刻。虽然稍显繁琐,但正是这样的设计,使得我们的处理器能够在高效与灵活之间找到完美的平衡。

在探寻计算机性能的奥秘时,一个不容忽视的细节就是缓存行的大小。尽管它在不同的系统架构中可能有所差异,但一个常见的标准是64字节,甚至更大。想象一下,当CPU渴望从内存中汲取数据时,它并不是仅仅挑取一片孤叶,而是整个枝条——即整个缓存行。

这是因为缓存的效能,常常得益于一种被称为“数据局部性”的原则。简单来说,就是一旦某个数据点被CPU选中,它周围的“伙伴”们也极有可能成为下一个被点名的幸运儿。想象一下,这就像是在图书馆中查找一本关于物理学的书籍,当你找到它时,相邻的几本关于量子力学或相对论的书籍也很可能会在接下来的时间里吸引你的目光。

正是这种连续数据的紧密“拥抱”,让它们在同一个缓存行中相依为命。如此一来,不仅减少了CPU与内存之间频繁的数据交换,还极大地提高了缓存的命中率,进而让计算机的性能如同插上了腾飞的翅膀,疾驰在高效处理的蓝天之上。

在编程的浩瀚宇宙中,掌握缓存行的奥秘,就如同手握一把金钥匙,能为您的程序性能带来质的飞跃。作为一位深思熟虑的程序员,您是否曾想过,如何巧妙利用数据的局部性规律,如同掌握魔术师的法杖,巧妙规避那一次次潜在的缓存未命中陷阱?当您深谙此道,您的程序访存模式将如同行云流水般顺畅,整体性能也将因此焕发勃勃生机。

无需依赖外界的帮助,您便是自己程序性能的掌控者。让我们一同踏上这场优化之旅,用智慧与勇气,书写属于您的性能传奇!