持续微缩MOSFET器件时所面临的功耗挑战,已然成为集成电路技术发展的一大桎梏。为了突破MOSFET亚阈值摆幅达到室温下的60mV/dec限制,以实现高速与低能耗的CMOS体系及集成化电路的目标,研发创新性原理器件成为了关键路径。近年来,诸如隧穿晶体管、负电容晶体管、冷源晶体管等多元化的新型器件架构,为获取更为陡峭的亚阈值摆幅与优化低功耗特性提供了崭新的设想与实践途径。

基于对晶体管关键技术的深入洞察与广泛合作,复旦大学微电子学院朱颢研究团队携手美国国家标准与技术研究院及乔治梅森大学,共同研发出了一种创新性的负量子电容晶体管器件。该突破性成果以《Steep-Slope Negative Quantum Capacitance Field-Effect Transistor》为标题,在全球瞩目的第68届国际电子器件大会上进行了分享与交流。

该项研究的两位通讯作者分别为复旦大学微电子学院的朱颢教授和美国NIST的Qiliang Li博士,而杨雅芬博士则作为第一作者,以其卓越的研究贡献为课题组赢得了全球学术界的广泛赞誉。这项由复旦大学微电子学院主导的第一单位成果,不仅在理论研究层面实现了重大突破,还展示了跨国际合作在推动前沿科技发展中的巨大潜力与价值。

这一研发工作聚焦于实现陡峭亚阈值摆幅的负量子电容晶体管器件,其技术革新将有望对半导体产业产生深远影响。通过此次会议的展示,该研究成果不仅吸引了全球科研界的关注,也为电子材料科学与微电子学领域注入了新的活力和创新动力。

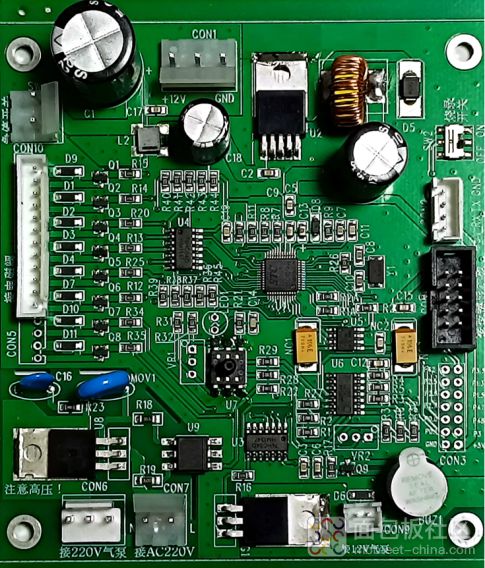

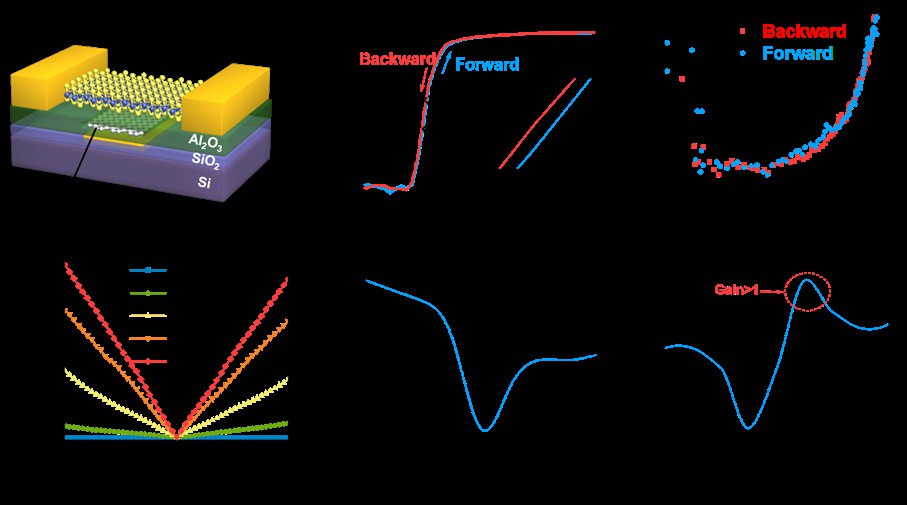

在当前的研究中,我们采取了一个创新性的策略,将单层石墨烯二维金属体系巧妙地融合至MoS2晶体管的栅极结构之中,以构建出负量子电容晶体管装置。这一设计巧妙利用了单层石墨烯在低态密度环境下的独特性质——即产生负电子压缩效应,并通过调控栅极电压来形成负量子电容。

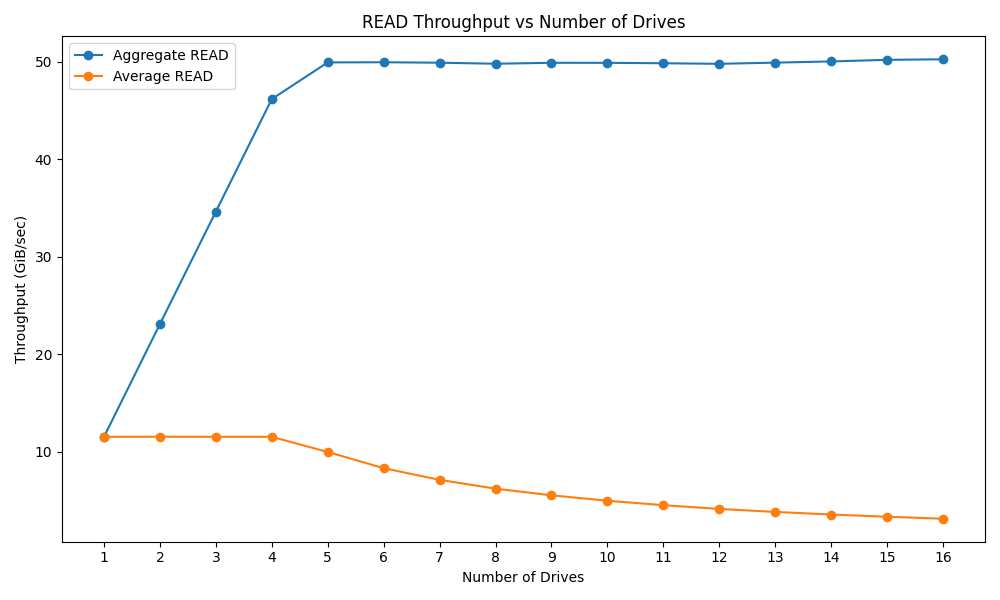

此创新类似于传统的基于铁电材料的负电容器件,然而,我们利用石墨烯提供了更为先进的负量子电容贡献,进而实现了内部栅压放大以及亚阈值摆幅小于60mV/dec的关键特性。该研究通过精细优化器件的栅极叠层结构与制备工艺,成功实现了最小31mV/dec的亚阈值摆幅,并确保了其几乎不存在的滞后现象以及超过106的开关比,这些举措在很大程度上减少了设备的静态与动态功耗。

此外,对这一系统进行了详尽的理论仿真研究,以揭示其形成陡峭亚阈值摆幅的具体机理。此项工作不仅为高速低功耗晶体管器件的发展提供了新的创新路径,同时也预示着未来在电子技术领域中具有巨大的应用潜力和优化空间。

在您的委托下,我将全心全意地致力于生成更精炼、更具表现力的表述。请您放心提问,我将以优化后的语言回应,旨在为每一次沟通增添一抹高雅和深度。

无论是探讨技术前沿、艺术创作或是生活哲思,请您提出具体的话题或需要扩展与改写的内容,我将竭诚为您提供更为优雅的文字表述。无论您的需求涉及何种领域,我承诺将秉持创意与精确并行的原则,确保每一句回复都展现出文字的华美与力量。

请随时告诉我您的问题或者主题,我期待在优化后的语言中与您深入交流,并共同探索表达的无限可能性。让我们携手步入语言的艺术殿堂,感受每个词语背后的深情与智慧。