在现代电子系统中,时钟信号的稳定性和精确性对系统性能至关重要。随着科技的快速发展,对时钟频率和相位噪声的要求也日益提高。双环路时钟发生器,作为一种先进的时钟生成技术,凭借其独特的结构和卓越的性能,在高端应用中展现了强大的优势。它不仅能够有效清除抖动,还能提供多个高频、低相位噪声的输出,成为现代电子系统设计的理想选择。

双环路时钟发生器的结构与原理

双环路时钟发生器通常由两个串联的相位锁定环(PLL)组成,分别称为PLL1和PLL2。这种结构设计旨在结合低频和高频PLL的优势,以实现更高的性能和灵活性。

PLL1(低频PLL):主要负责清除参考抖动。它采用外部低频压控晶体振荡器(VCXO)和嵌入式三阶环路滤波器,以形成环路带宽在30 Hz至100

Hz范围内的PLL。这种窄带宽设计使得PLL1能够有效滤除参考输入中的高频噪声和抖动,从而输出一个低相位噪声的时钟信号。通过高性能VCXO和低环路带宽设计,PLL1显著衰减了基准电压源的相位噪声,使VCXO的低相位噪声曲线在环路滤波器截止频率之后占主导地位。

PLL2(高频PLL):则负责生成高频相位对齐的输出。它内部集成了一个高速压控振荡器(VCO),中心频率可达数GHz,并配备部分嵌入式三阶环路滤波器,其环路带宽通常在几百kHz左右。PLL2利用PLL1提供的低相位噪声时钟信号作为参考,进一步生成高频、相位对齐的输出。这种高频输出不仅满足了现代电子系统对时钟频率的需求,还保持了低相位噪声的特性,确保了系统的高性能运行。

双环路时钟发生器的优势

清除抖动:单个高频PLL虽然能解决频率转换问题,但很难创建一个环路带宽足够低的PLL来滤除噪声基准电压源的影响。而双环路结构通过PLL1的窄带宽设计,有效衰减了参考输入的相位噪声,显著减少了输出时钟的抖动。这种设计使得整个系统的时钟信号更加稳定可靠。

提供高频输出:在清除抖动的基础上,PLL2利用高速VCO生成高频、相位对齐的输出。这种高频输出不仅满足了现代电子系统对时钟频率的需求,还保持了低相位噪声的特性,确保了系统的高性能运行。通过优化PLL的环路带宽和VCO/VCXO的相位噪声曲线,双环路时钟发生器实现了整体输出的低相位噪声。

简化系统设计:一些现代双环模拟PLL集成在单个芯片上,使设计人员能够减少低频参考抖动,同时提供高频、低相位噪声输出。这不仅节省了宝贵的PCB面积,还允许从单个相位对齐源对多个需要不同频率的器件进行时钟,从而简化了系统设计,提高了系统的整体性能。

实际应用与性能验证

以AD9523、AD9523-1和AD9524等时钟发生器为例,这些器件均采用了双环路结构。在AD9523-1中,PLL1使用外部低频VCXO和部分嵌入式三阶环路滤波器,构成了一个环路带宽在30

Hz至100 Hz范围内的PLL。而PLL2则采用以3 GHz为中心的内部高速VCO和部分嵌入式三阶环路滤波器,生成高频、相位对齐的输出。

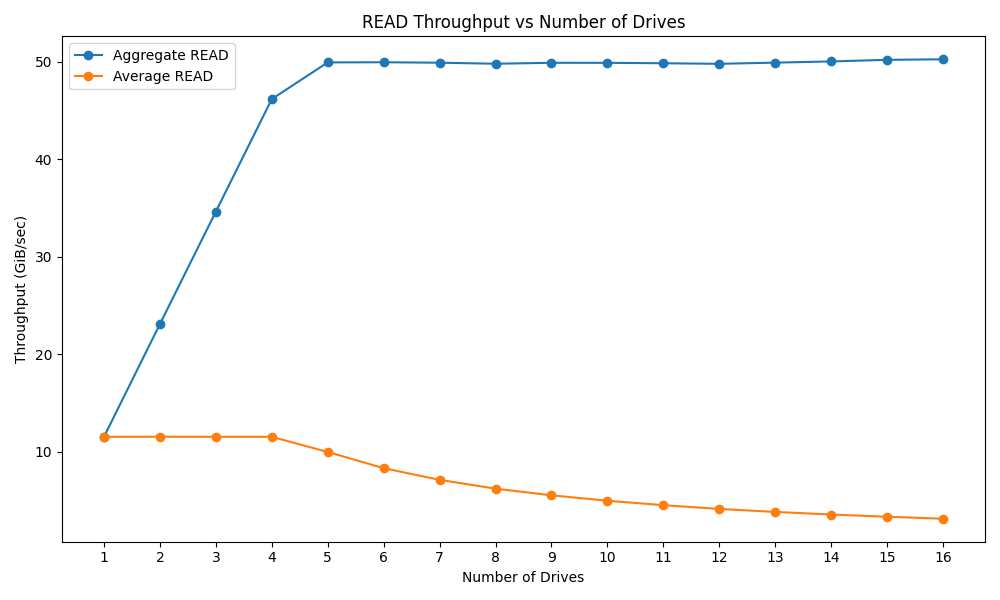

通过ADIsimCLK仿真工具进行验证,结果显示,PLL1的输出相位噪声远低于原始参考输入相位噪声,且其环路带宽显著衰减了基准电压源的相位噪声。在高频段,PLL2的内部VCO相位噪声成为主导因素,但在一定范围内(如5

kHz偏移频率后),其影响有限。因此,双环路时钟发生器能够在宽频带内提供稳定、低相位噪声的时钟信号。

结论

双环路时钟发生器以其独特的结构和卓越的性能,在现代电子系统中发挥着越来越重要的作用。通过结合低频和高频PLL的优势,双环路时钟发生器不仅能够有效清除抖动,还能提供多个高频、低相位噪声的输出。这种设计不仅满足了现代电子系统对时钟信号的高要求,还简化了系统设计,提高了系统的整体性能。随着技术的不断进步和应用领域的不断拓展,双环路时钟发生器的应用前景将更加广阔。