我们经常可以看到初学者在单片机论坛中询问他们是否可以在他们微不足道的小的8位微机中运行Linux。这些问题的结果通常是带来笑声。我们也经常看到,在Linux论坛中,询问Linux运行的最低要求是什么。常见的答案是Linux需要一个32位架构和一个MMU(存储器管理单元),并至少1MB的RAM来满足内核的需求。

考虑到8位的单个芯片比32位芯片要便宜很多的事实,8位的出货量其实远高于32位的。

打个直观的比方,现在我们有了高铁,是不是所有传统的普快、特快火车都要立即淘汰呢?

显然事实并非如此,至于原因就太多了。现实情况就是8位MCU曾经的应用领域并不能立即用32位的MCU直接替代。

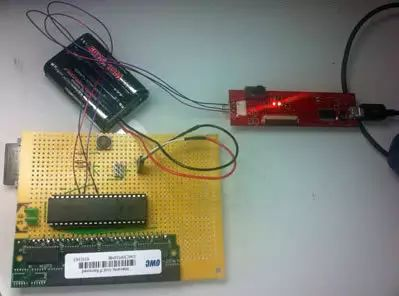

本项目旨在(并且成功)粉碎这些概念。下图中您所看到的开发板基于ATmega1284P。我(歪果仁)还制作了一块基于ATmega644a的开发板,也同样获得了成功。该开发板没有使用其他处理器,启动Linux

2.6.34内核。事实上,它甚至可以运行一个完整的Ubuntu栈,包括X(如果你有时间等它启动)和gnome。

RAM(随即存取存储器)

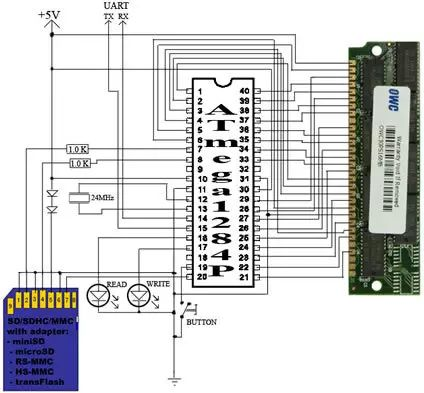

是的,没错,完整的Linux安装需要数兆字节的RAM和32位带有MMU的CPU。本项目拥有这一切。首先,让我们访问RAM。正如您所看到的,在电路中有一块古董级的30引脚SIMM内存模块。这些是基于80286的PC曾经使用的。它通过接口和ATmega连接,我写代码来访问它并按照规格刷新它(SDRAM需要恒定速率刷新以避免丢失数据)。它到底有多快呢?刷新中断每62ms发生一次,占用时间1.5ms,因此占用3%以下的CPU。访问RAM,为了便于编程,一次访问一个字节。这样产生的最大带宽约为300KBps。

存 储

对于RAM需要工作在休眠状态,我们有两件事要处理。存储并不是太难解决的问题。使用SPI可以十分容易的与SD卡交互,我的项目中做到了这一点。一个1GB的SD卡可以工作的很好,虽然512MB就已经满足这一特殊的文件系统(Ubuntu

Jaunty)。ATmega拥有一个硬件SPI模块,但无论出于何种原因,它工作的不是十分顺畅,因此我将这个接口进行位拆裂。它仍然足够块——大约200KBps。这对项目来说还非常有意义——它能够在有足够管脚的任何微控制器上实现,而不用使用其他硬件模块。

CPU(中央处理单元)

所有剩下的就是那个32位CPU和MMU需求。不过AVR没有MMU,并且它是8位的。为了克服这一困难,我编写了一款ARM仿真器。ARM是我最熟悉的架构,并且它足够简单,可以让我很舒服的为它编写出一个仿真器。为什么要编写一个,而不是移植一个呢?好吧,移植别人的代码是没有乐趣的,再加上我看到没有将仿真器轻松移植到8位设备上的书面资料。原因之一:AVR编译器坚持16位处理整数将会给你带来麻烦,如简单的“(1<<20)”,产生0。你需要用“1UL<<20”。不必要的说,困扰其他人的未知基本代码寻遍所有的地方,整数都被假定并将会失败,这将是一个灾难。另外,我想用这个机会编写一款很好的模块化ARM仿真器。所以我付诸行动。

其他功能

电路板通过一个串行端口和真实世界进行通信。目前,它通过串行端口连接到我PC运行的minicom上,但是它可测的替代连接是连接到电路上的一个键盘和一个字符LCD,可以使其完全独立。电路板上还有两个LED。它们指示SD卡的访问情况。一个代表读操作,一个代表写操作。电路板上还有一个按钮。当按下并按住1秒时它将使串行端口脱离仿真的CPU的当前有效速度。AVR的主频是24MHz(超过原有20MHz的轻微超频)。

它的速度有多快?

uARM肯定没有速率守护进程。它花了大约2个小时启动到BASH提示符("init=/bin/bash"内核命令行)。然后用4个多小时启动整个Ubuntu("exec

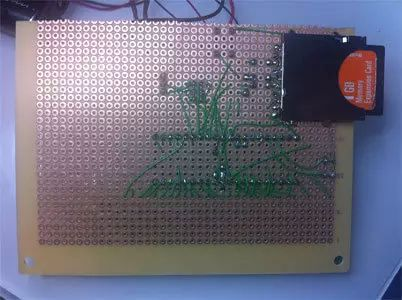

init"然后登陆)。启动X将消耗更长时间。有效的仿真CPU速度约为6.5KHz,这与你期望的在一个可怜的8位微控制器上仿真一个32位CPU和MMU是同等的水平。奇怪的是,一旦启动,该系统是有些可用的。您可以输入一个命令,并在一分钟之内得到答复。也就是说实际上你是可以使用它的。比如,今天我还用它来格式化我的SD卡。这绝对不是最快的,但我觉得它可能是最便宜、最慢、最简单的手工组装、最低的部件数量以及最低端的Linux

PC。电路板是使用导线手工焊接的,甚至没有使用印刷电路板(PCB)的必要。

仿真器的细节?

仿真器是相当模块化的,允许它随意扩展仿真其他SoC(片上系统)和硬件配置。仿真的CPU是ARMv5TE。前一段时间,我开始进行支持ARMv6的工作,但是一直没有完成(从代码中可以看出来),因为不是很需要。仿真的SoC是PXA255。由于模块化的设计,你可以替换SoC.c文件,并使用相同的ARMv5TE核心编译一个完整的新的SoC,或者替换核心,或者按照意愿替换外设。这是有目的的,我的意思是这个代码也是一个关于ARM

SoC如何工作的相当整洁的范例。CPU仿真器自身的代码并不是太整洁,那么,好吧,它是一个CPU模拟器。这是几年前花了超过6个月的空闲时间写的,然后就放在一边了。它最近复活是专门为了这个项目。仿真器实现了i-cache来提高速度。这给予了AVR很多帮助,使内部存储器能够以超过每秒5MB的速率访问,而不像我的外部RAM。我还没有抽出时间去实现d-cache(数据缓存),但是这已经在我的待办事项列表上了。访问块设备没有被仿真为SD设备。事实证明这太慢了。取而代之的是一个准虚拟化磁盘设备(pvdisk,参见pvDisk.tar.bz2,GPL许可证),我编写的时候使用了一个无效的操作码来调入仿真器并访问磁盘。我的镜像中的ramdisk(虚拟磁盘)加载这个pvdisk,然后改变根目录到/dev/pvd1。

ramdisk被包含在了“rd.img”中。我使用的“机器类型”是PalmTE2。为什么?因为我非常熟悉这款硬件,它是我见到的第一款PXA255机器类型。

Hypercall(超级调用)?

有一些服务你可以通过使用一个特殊的操作码向仿真器发出请求。在ARM中它是0xF7BBBBBB,在Thumb中它是0xBBBB。挑选这些是由于它们所在的范围ARM保证是未定义的。超级调用号码通过寄存器R12被传递,参数通过寄存器R0-R3被传递,返回值被放置在R0中。

调用:

· 0 = 停止仿真

· 1 = 打印十进制数

· 2 = 打印字符

· 3 = 获取RAM大小

· 4 = 块设备操作(R0 = 操作,R1 =

扇区(sector)号)。请注意,这些不写入仿真的RAM,它们使用另一个超级调用填充了仿真用户访问的仿真器内部缓冲区,一次一个字。我的意思是实现DMA,但是还没有抽出时间去做。

操作:

· 0 = 获取信息(如果扇区号是0,返回扇区的数量;如果扇区号是1,以字节位单位返回扇区大小)

· 1 = 扇区读取

· 2 = 扇区写入

· 5 = 块设备缓冲区访问(R0 = 值输入/值输出,R1 = 字数,R2 = 如果写入为1,其他情况为0)

Thumb支持?

完全支持Thumb。我欺骗了一下,解码每个Thumb指令字符串(instr)为等价的ARM指令字符串并执行,以此代替使用ARM仿真器函数。它不像它原来一样快,但是它简单并且代码小巧。可以使用256KB的查找表,但是我感觉256KB对于微控制器的闪存来说太大了。一些Thumb指令不能被转换为ARM指令,它们被正确处理代替。

我想要建立一个!

用于非商业目的,你肯定可以做到这一点。接线方式如下:

· RAM的DQ0-DQ7连接AVR的C0-C7;

· RAM的A0-A7连接AVR的A0-A7;

· RAM的A8-A11连接AVR的B0-B3;

· RAM的nRAM nRAS nCAS nWE连接AVR的D7 B4 B5;

· SD的DI SCK DO连接AVR的B6 B7 D6;

· LED的read write连接AVR的D2 D3(LED的其他管脚接地);

· 按钮连接AVR的D4(其他管脚接地)。

RAM可以是任何30引脚的16MB的SIMM,可以运行在每64毫秒4000个周期的CAS-before-RAS刷新频率下。我使用的(OWC)可以花几块钱在网上买到。原理图显示在这里,点击可以放大。

源代码?

这个代码有点儿乱,但是它可以工作(代码国内无法下载)。要在PC上建立仿真器并进行尝试输入“make”。要运行使用“./uARM

DISK_IMAGE”。要建立优化的PC版本使用“make BUILD=opt”。要建立AVR运行的版本使用“make

BUILD=avr”。现在,它的编译目标是ATmega1284P。要以ATmega644为编译目标,除了要修改makefile,减少icache.h中的数字以便于i-cache足够小来配合644内部的RAM。在归档文件中还包括用于1284p最终的hex文件。

启动过程

要在AVR中保留代码空间,几乎没有启动代码存在于仿真器中。事实上,“ROM”总共50字节:8字节用来选择Thumb模式,一些Thumb代码要读取SD卡的第一个扇区并跳到Thumb模式(参看embeddedBoot.c)。SD卡的MBR有另一个bootloader(在Thumb模式下写入)。这个bootloader看着MBR,找到活动分区并加载它的内容到RAM的末尾。然后,它跳到目的RAM地址+512(参看mbrBoot.c)。这里运行着第三个,也是最大的bootloader,ELLE(参看ELLE.c)。这个bootloader重新定位了ramdisk,建立ATAGS,并调用内核。我提供了所有的二进制文件和源代码以便于大家能够按照意愿制作您自己镜像。启动过程会让人回忆起PC开机。:)包含的mkbooting.sh工具可以用来制作用于启动分区的工作镜像。