封装为何需要CAE?

封装是半导体组件制造过程的最后一个环节,会以环氧树脂材料将精密的集成电路包覆在内,以达到保护与散热目的。在芯片尺寸逐年缩小的趋势下,封装制程所要面临的挑战更趋复杂,牵涉到组件高密度分布、金属接脚配置与电学性能等层面。若设计不良,可能会引发结构强度、缝合线、包封、散热与变形等问题。为了控制实际生产过程中的不确定因素与风险,应在封装的研发阶段导入CAE,将有助于事前问题分析与寻求优化设计,以降低不必要的成本损耗。

CAE前处理的实务挑战

在CAE仿真流程之中的前处理过程,即是将设计端的原始二维或三维模型转化为可进行数值分析用的三维实体网格;一般在此阶段大多是使用商业软件进行网格前处理。使用者在这个步骤常常会遇到几项问题:(1)软件难以上手,操作步骤繁杂;(2)模型过于复杂,网格生成过程旷日废时,或是设计变更时,网格难以修改;(3)最终的网格元素量过多,需要冗长的分析时间。

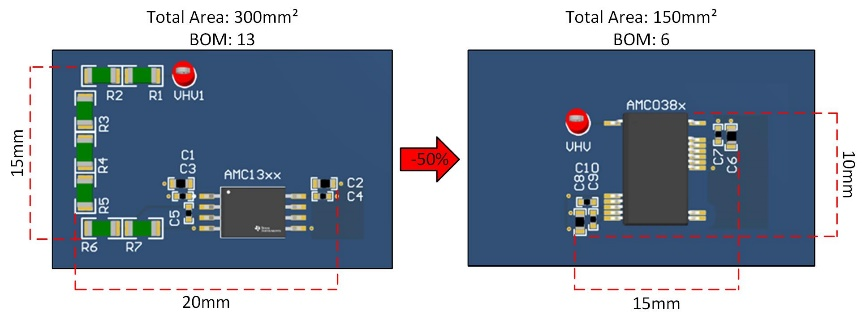

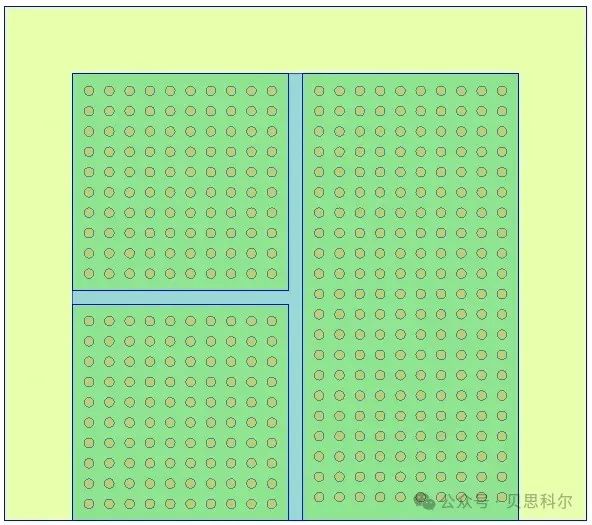

图一是个毛细力底部充填的案例。此类设计常会有数千颗甚至是数万颗的锡球,因此前处理阶段的网格尺寸会受限于锡球大小与其分布,这通常会导致网格过密、网格元素庞大。如果再加上网格质量或设计变更等因素,将会使CAE建模变得相当棘手。

图一 毛细力底部充填案例

图二 使用者可藉读取存有大量点数据的CSV文件,迅速完成建立大量锡球模型的工作。

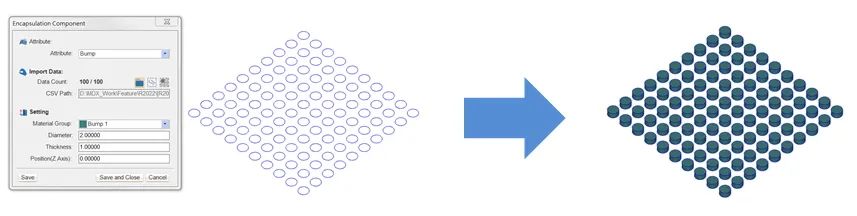

图三 透过撒点机制针对产品整体与局部进行调整。

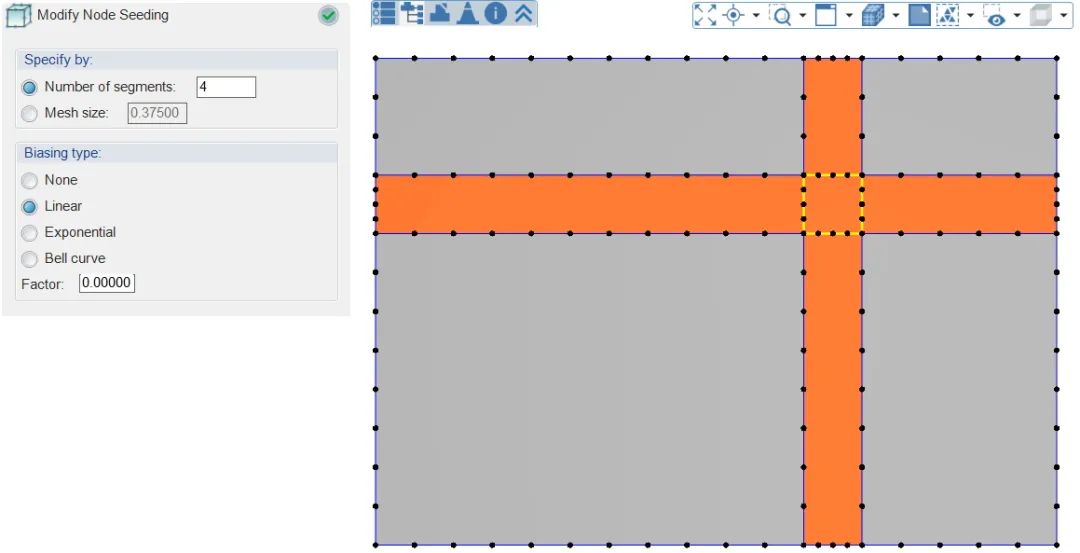

下一步便是以三维几何模型搭配撒点后的基底平面建立网格,并开放手动编辑网格,提高操作弹性,让用户可以建构出所需的疏密分布,获得适当且高质量的网格。图四即为利用前述操作所完成部份加密且整体均匀分布的网格。

图四 部份加密且整体均匀分布的网格

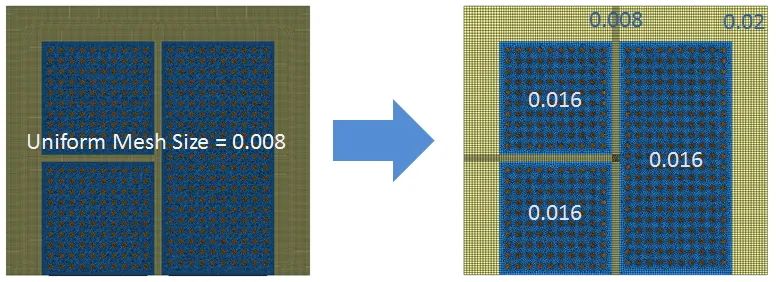

透过自动混合式网格精灵进行IC组件厚度设定,以及自动生成各组件网格,即可轻松建立三维实体网格,同时满足网格轻量化的需求。以图五为例,在给予适合的整体网格尺寸后,接着在局部进行加密,可以有效地减少整体网格元素量。

图五 给予适合的整体网格尺寸,接着在局部进行加密,可有效减少网格元素量

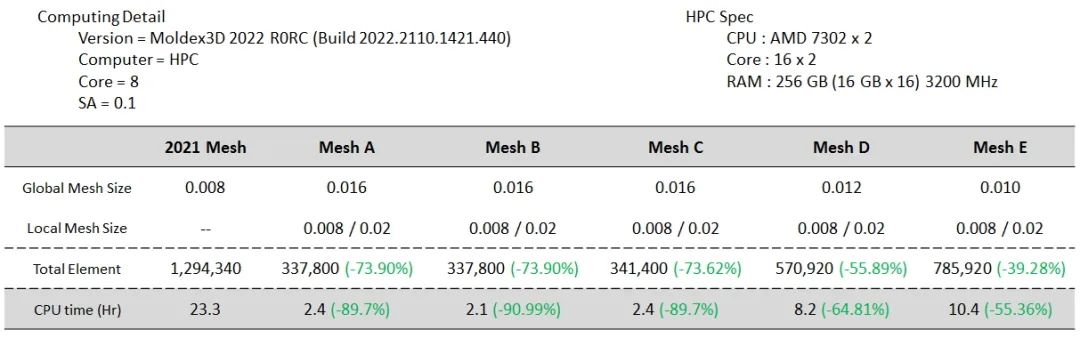

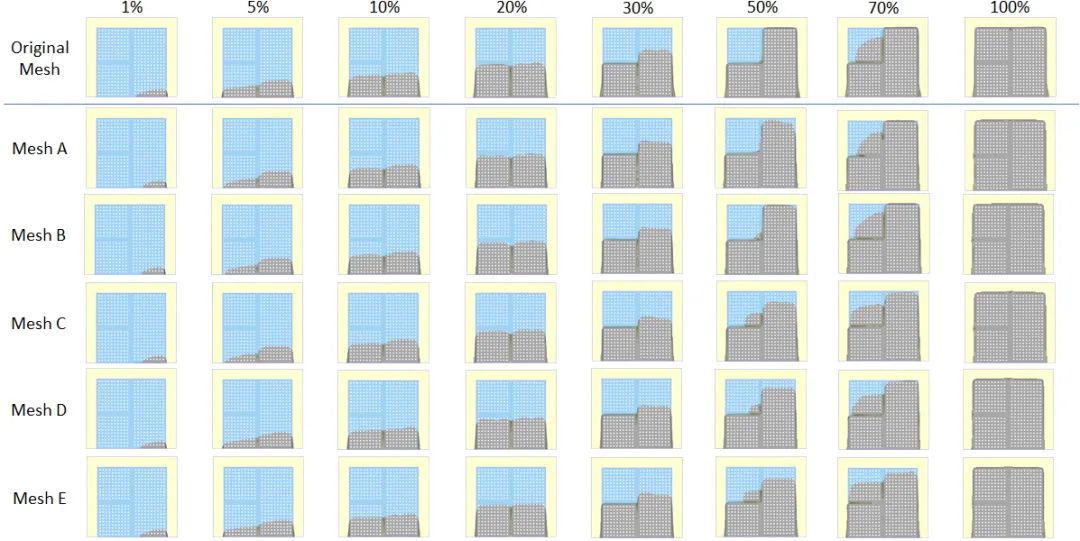

接着以此模型实际测试不同网格尺寸的组合,并且与原始网格相比,整体的元素量可以减少约四成至七成;所需的分析时间则有效节省五成至九成,比较结果如下表所示。

透过上表不同组合的网格与原始网格相互比较,可看出整体的波前行为是近似的。换句话说,适当运用Moldex3D Studio 2022的IC网格自动建构精灵及网格工具,不但能够简化前处理流程,节省建构网格的时间,同时可以得到可靠的分析结果。

图六 Moldex3D Studio 2022的IC网格自动建构精灵,可帮助简化前处理流程

结论:

在Moldex3D 2022封装仿真成型功能中,IC封装自动混合式网格精灵提供了高度自动化的网格流程,能够协助用户方便地进行CAE前处理。另外也新提供了数种的半自动网格编修工具,能够针对基底表面网格进行局部调整,使整体网格建立流程更加灵活。在工程实务上能够大幅节省前处理与后续的分析时间,加快研发期间的问题排除,同时有助于寻求优化方案与封装阶段的成本控制。

想要了解更多Moldex3D产品信息,欢迎联系贝思科尔!