因为

摩尔定律

的失效,半导体行业过去多年正在寻找提升芯片性能的方法,而

Chiplet

正在成为几乎所有巨头的共同目标。然而,因为Chiplet的理念是将芯片的不同功能模块变成一个die,如何保证这些die能够更通用地连接到一起就成为了行业的头等大事。

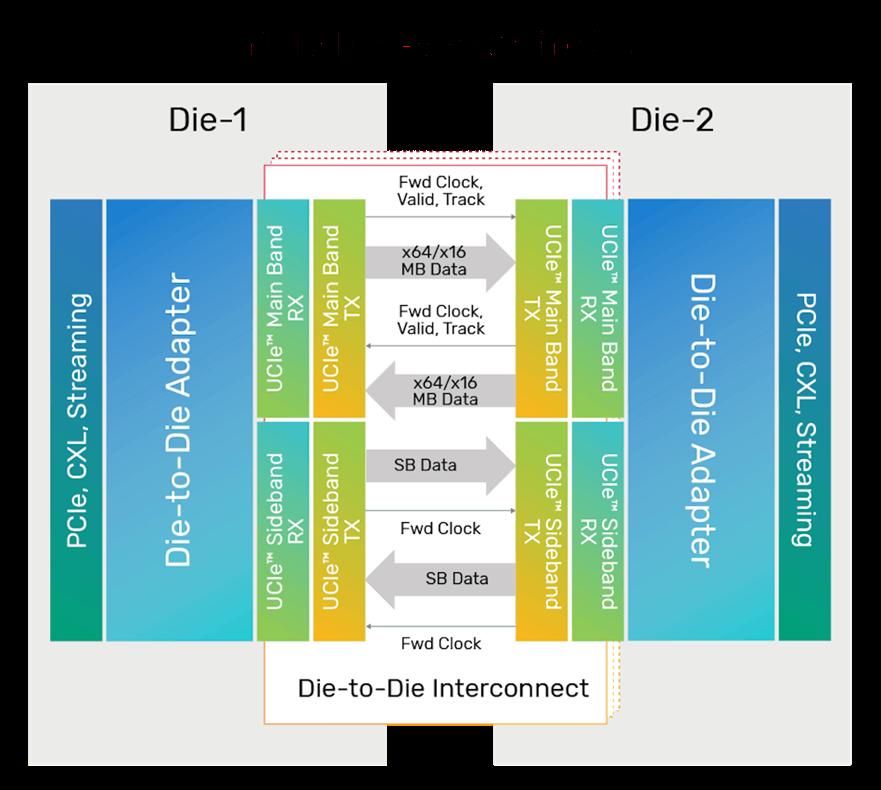

于是,UCIe( Universal Chiplet Interconnect Express )便顺势成立。据介绍,UCIe是一种开放的行业架构标准,可在不同chiplet之间提供die-to-die之间的接口,解决物理芯片间 I/O 层、芯片间协议和软件堆栈问题。

UCIe为die提供了标准接口

(source:Cadence)

而继之前的UCIe 1.0和UCIe 1.1之后,新的UCIe 2.0标准正式发布。而关于新标准的描述,可以参考半导体芯闻昨日发布的

《UCIe 2.0规范,正式发布》

。我们也摘译如下:

UCIe 2.0,发布

UCIe联盟日前宣布发布其 2.0 规范。UCIe 2.0 规范增加了对标准化系统架构的支持,以实现可管理性,并全面解决了跨多个chiplets的 SIP 生命周期(从分类到现场管理)的可测试性、可管理性和调试 (DFx) 设计挑战。可选的可管理性功能和 UCIe DFx Architecture (UDA) 的引入,包括每个芯片内的管理结构,用于测试、遥测和调试功能,允许通过灵活统一的 SIP 管理和 DFx 操作方法实现与供应商无关的芯片互操作性。

此外,2.0 规范支持 3D 封装,与 2D 和 2.5D 架构相比,可提供更高的带宽密度和更高的功率效率。UCIe-3D 针对混合键合进行了优化,凸块间距可适用于大至 10-25 微米、小至 1 微米或更小的凸块间距,从而提供灵活性和可扩展性。

另一个功能是针对互操作性和合规性测试优化的封装设计。合规性测试的目标是根据已知良好的参考 UCIe 实现来Device Under Test (DUT) 的主频带支持功能。UCIe 2.0 为物理、适配器和协议合规性测试建立了初始框架。

UCIe 联盟总裁兼三星电子公司副总裁 Cheolmin Park 表示:“UCIe 联盟支持多种芯片,以满足快速变化的半导体行业的需求。UCIe 2.0 规范在之前的版本基础上开发了全面的解决方案堆栈,并鼓励芯片解决方案之间的互操作性。这又是联盟致力于蓬勃发展的开放芯片生态系统的又一例证。”

UCIe 2.0 规范的亮点:

全面支持具有多个chiplets的任何系统级封装 (SiP) 结构的可管理性、调试和测试。

支持3D封装,显著提升带宽密度和功率效率。

改进的系统级解决方案,其可管理性被定义为chiplet堆栈的一部分。

针对互操作性和合规性测试优化的封装设计。

完全向后兼容 UCIe 1.1 和 UCIe 1.0。

与此同时,我们也带来了UCIe联盟同步发布的UCIe 2.0白皮书,以飨读者。

以下为白皮书正文:

UCIe 2.0 规范:持续创新,

推动开放 Chiplet 生态系统

Universal Chiplet Interconnect Express (UCIe) 是一种开放的行业标准互连,可在 Chiplet 之间提供高带宽、低延迟、节能且经济高效的封装内连接。它满足了整个计算领域(涵盖云、边缘、企业、5G、汽车、高性能计算和手持设备)对计算、内存、存储和连接的预计不断增长的需求。UCIe 能够封装来自各种来源的die,包括不同的代工厂、设计和封装技术。

UCIe 2.0 规范涉及两个广泛的领域,以推动蓬勃发展的开放 Chiplet 生态系统。第一个规范以整体方式解决了任何具有多个 Chiplet 的系统级封装 (SiP) 结构中出现的可管理性、调试和测试挑战。该解决方案超越了 UCIe 接口,使用 UCIe 增强功能,以完全向后兼容的方式进行扩展;第二个领域涉及使用混合键合互连等技术(我们将其称为 UCIe-3D)的间距非常细(9 µm 到大约 1 µm,甚至更低)的垂直

集成芯片

。

一、在整个芯片生命周期中解决 SiP 级别的可管理性、调试和测试挑战

可测试性、可管理性和调试是需要持续创新的三个主要方面。UCIe 1.0 和 1.1 规范有几种机制来处理互连级别的可管理性和测试/调试/遥测(统称为 DFx)设计的各个方面。示例包括通道裕度(lane margining)、合规性测试、故障报告、边带访问(sideband access)等。然而,在芯片和 SiP 级别仍有许多具有挑战性的问题必须解决,才能实现开放、即插即用的基于chiplet的生态系统的愿景。

UCIe 联盟正在全面解决这些挑战,超越接口级别,解决从die分类、封装/键合到现场级别的挑战——这涵盖整个硅片生命周期,这些增强功能将使我们的成员能够应用这些学习成果并改进上游。

在本文中,我们提供了实现广泛的、即插即用的基于小芯片的生态系统所需克服的挑战的示例。

在分类芯片测试期间,虽然我们可以探测凸块,但无法对微凸块进行探测;尤其是当我们转向 25µ 凸块间距时。因此,我们必须创新,使用其他凸块。同样,我们应该能够在现场无缝管理维修或固件升级。

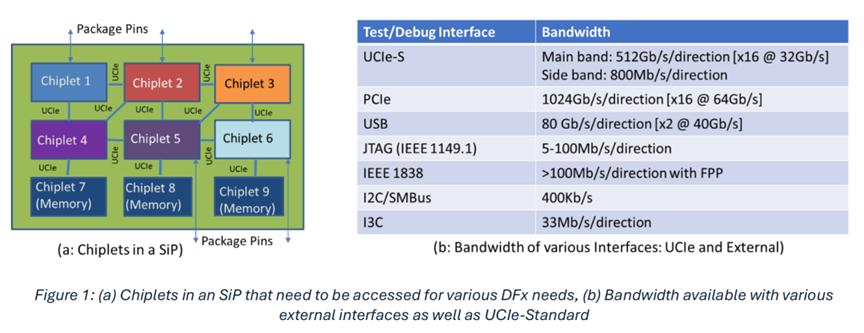

对于在封装级别可控性和可观察性有限的Chiplet,调试提出了独特的挑战(例如,无法在封装内插入逻辑分析仪或示波器)。行业应如何处理 SiP 中芯片的可管理性?最重要的是,我们如何安全地解决这些问题?一些chiplets可能无法从封装引脚直接访问(见图 1a),这一事实使这些问题变得更加困难。我们还需要处理各种带宽需求。例如,不同的chiplets对扫描链、调试、可管理性等所需的带宽范围不同。

我们对 UCIe 2.0 规范的方法是定义一个通用基础设施,该基础设施可在使用现有 IP 构建块(building blocks )以及封装级别的外部接口的同时解决所有已确定的挑战。我们认为这些功能是互补的,我们的方法适用于现有 IP(甚至非 UCIe IP),并对 UCIe PHY 进行了增强。我们还使用外部封装引脚来访问芯片集,以通过规范中定义的桥接机制进行管理、调试或测试。这些接口和 IP 必须与封装上的 UCIe 2.0 链路无缝协作,以提供所需的外部和内部访问。图 1b 列出了不同接口可用的带宽,为 SiP 设计人员提供了多种选择。

在 UCIe 2.0 规范中,可管理性是可选的。支持的机制包括发现chiplet集及其配置;初始化芯片集结构(initialization of chiplet structures)和参数(即串行 EEPROM 替换);固件下载;电源和热管理;错误报告;遥测;检索日志和崩溃转储信息;测试和调试;启动和报告自检状态;以及芯片安全的各个方面。这些机制利用现有的适用行业标准,并且与chiplets上的底层协议无关。这些机制旨在跨来自不同供应商的chiplet工作,并支持特定于供应商的扩展。这些功能是可发现和可配置的,允许在 SiP 之间快速部署通用固件库。UCIe 可管理性所需的核心功能可以通过硬件和/或固件实现,从而提高灵活性。

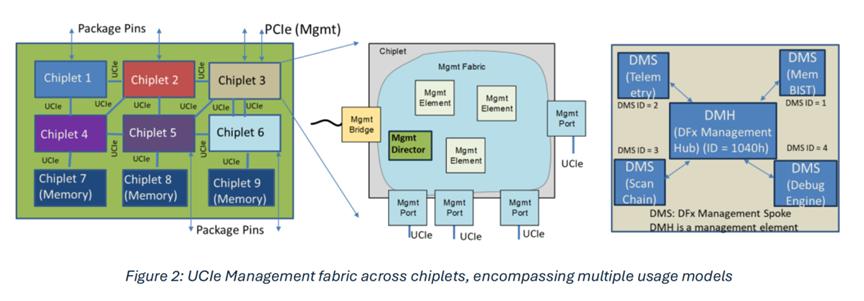

UCIe 2.0 可管理性基线架构(manageability baseline architecture,如图 2)定义了一种桥接功能,用于连接到外部接口(例如 SMBus 或 PCIe),从而实现封装外连接。每个chiplet组中的管理结构由多个管理元素组成,其中一个元素充当管理主管,负责发现、配置和协调 SiP 的整体管理,并充当可管理性信任根。

UCIe 管理传输被定义为一种独立于媒体(media-independent)的协议,用于芯片组中管理实体之间以及 SiP 中芯片组之间的通信。安全机制被定义为根据功能提供所需的保护级别。定义了两种管理链路封装机制,以使用边带和主带传输 UCIe 管理传输数据包。UCIe 定义了最多八个独立的虚拟通道来提供服务质量,每个通道都具有有序或无序语义。数据包基于信用(credits)进行交换,信用最初是在链路训练期间协商的。

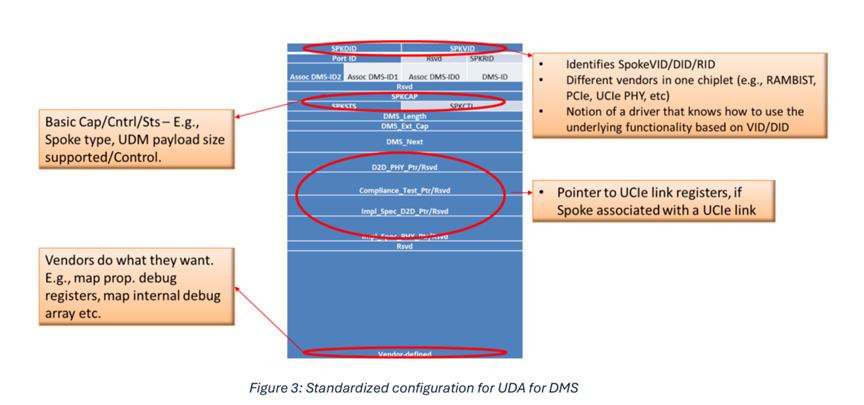

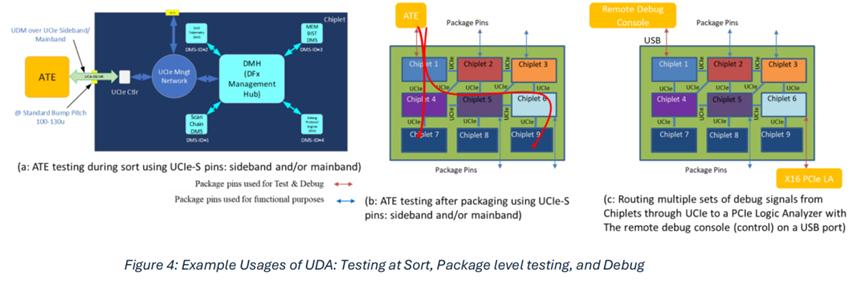

UCIe DFx 架构 (UDA:UCIe DFx architecture) 包含测试、遥测和调试,并通过管理结构进行覆盖。UDA 基于每个chiplet内的 Hub-Spoke 模型(图 2)。每个chiplet都支持一个 DFx 管理中心 (DMH:DFx Management Hub ),这是一个管理元素,可充当访问芯片内测试、调试和遥测功能的网关。DMH 允许发现这些功能,并将与这些功能相关的管理传输数据包路由到各种连接的 DFx 管理“辐条”(DMS:DFx Management “Spokes” )。辐条(Spokes)是实现给定测试、调试或遥测功能的实体。一些示例包括扫描控制器、MEM BIST、SoC(片上系统)结构调试、跟踪协议引擎、核心调试、遥测等。

架构配置寄存器(图 3)在现有寄存器之上具有 UCIe-wrapper,为软件提供了一个通用框架。对于系统级使用,可以根据 Spoke 的(UCIe 联盟分配的)供应商 ID (VID) 和(供应商分配的)Device ID (DID) 加载特定于供应商的驱动程序以支持每个独特的功能。UDA 的管理数据包可以作为内存访问协议数据包(例如,用于发现chiplet中的 DMH/DMS)和/或以供应商定义的 UCIe DFx 消息格式(例如,用于通过chiplet将调试信号发送到 PCIe 等封装引脚,以便使用逻辑分析仪进行观察)发送。图 4 演示了其他使用模型。

虽然管理数据包可以在现有 UCIe 端口上进行

时分复用

,但 UCIe 2.0 还提供了添加专用 UCIe-S 端口以实现可管理性和 UDA 功能的额外功能。这些端口可以是简单的边带(sideband),以 4 个凸块或半宽 (x8) 提供 800 Mb/s/方向,或更高,UCIe-S 以 32 GT/s 的速度为每个 x8 提供 256 Gb/s/方向。

二、垂直集成芯片组可显著提高功率性能,并采用 UCIe-3D

UCIe 联盟于 2022 年 3 月成立,我们发布了定义明确的 UCIe 1.0 规范,解决了平面连接(2D 和 2.5D)问题。我们认识到垂直集成的重要性,并表示我们打算研究 3D 芯片组。UCIe 2.0 规范通过完全定义的规范(涵盖平面和垂直连接)兑现了这一承诺。

十多年来,随着封装内存和计算的商业化,提供垂直连接的 3D 互连芯片组的技术取得了显著进步,证实了需求的存在。现在是时候通过一系列选项来标准化接口,以满足生态系统中的各种需求。

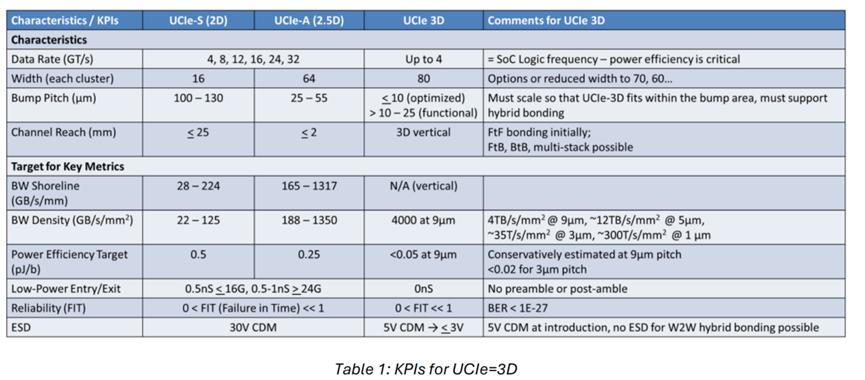

3D 封装技术(例如混合键合 (HB:Hybrid Bonding))的最新趋势是大幅缩Chiplet之间的凸块间距。UCIe-3D 的目标是将凸块间距从 9 µm 缩小到 1 µm,甚至可能更低。3D 互连将Chiplet之间的距离缩小到几乎为 0。因此,互操作性需要限制在相同的凸块间距内。虽然这不是一种广泛的即插即用(即,凸块间距为 1 µm 的芯片只能与凸块间距为 1 µm 的另一个chiplet混合键合,而不能与凸块间距为 9 µm 的chiplet混合键合),但关键性能指标 (KPI:key performance indicator) 的改进(例如带宽密度、功率效率等)是巨大的。如表 1 所示。

UCIe-3D 的第一大优势是带宽密度增加。这是双重优势。首先,减小的凸块间距(从 9 µm 降至 1µm 以下)意味着给定面积的导线数量与平方成反比;例如,将 2.5D 的 25 µm 与 3D 的 5 µm 进行比较,可得出相同面积的导线数量增加 25 倍;其次是面积本身。与 UCIe 2D/2.5D 相比,UCIe-3D 具有真实连接与海岸线消耗的优势。这意味着外围 PHY 上不会浪费任何面积,并且整个芯片组都可用于 3D 连接。

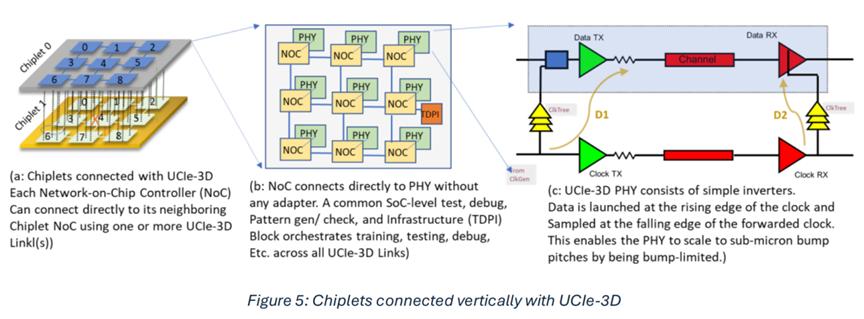

图 5 显示了使用 UCIe-3D 连接的两个Chiplet组和九个片上网络控制器 (

NOC

)。要获得凸块间距缩放的好处,必须保持相关电路简单,限制凸块。随着带宽密度的增加,无需驱动更高的频率。如表 1 所示,即使在 4 GT/s 频率下,带宽密度也比 32 GT/s 的 UCIe 2.5D 提高了几个数量级(例如,凸块间距为 1 µm 的 UCIe-3D 为 300 TB/s/mm²,而凸块间距为 25 µm 的 UCIe-2.5D 为 1.35 TB/s/mm²)。为了适应减小的凸块间距,我们通过选择适当的误码率 (BER:bit error rate ) 消除了对 (反) 序列化、CRC、重放等的需求(如表 1 所示)。同样,ESD 保护电路必须先降低至 5V CDM,并从 3 µm 开始逐渐消除。

UCIe-3D 的第二个主要优势是功耗更低。随着距离减小(~0),相关的电寄生效应也随之减小。随着 SoC 频率(<= 4 GT/s),电路变得简单 - 由简单的逆变器组成。再加上频率降低,功耗甚至更低(至少低一个数量级)。

4、结论

UCIe 技术发展势头强劲!自 UCIe 联盟成立以来,UCIe 联盟成员已宣布了产品开发,并提供了基于 UCIe 1.0 和 1.1 规范的可操作硅片演示。我们正处于与其他成功标准(包括 PCIe、CXL 和 USB)类似的数十年历程的早期阶段。随着技术的普及,我们的成员致力于对未来规范进行必要的改进;

UCIe 2.0 是我们承诺的体现。可管理性和 DFx 增强功能表明我们不断致力于改进现有方法,而 UCIe-3D 则表明我们愿意接受必要的挑战,以实现能效性能的指数级改进。

最后,我想描绘一个系统级封装的愿景,其中使用现有的 UCIe-2.5D 和 UCIe-2D 平面互连连接多个 UCIe-3D 芯片组堆栈,以及所有即将推出的增强功能。如今的芯片级封装就像是小城市,其密度高于十年前的单片芯片,而后者可以比作小村庄。未来采用 UCIe-3D 的 SiP 将像一座摩天大楼林立的大都市,密度极高。计算和内存元件紧密封装在一起的高密度意味着比特传输距离更短,从而实现卓越的性能和更低的功耗。换句话说,未来确实非常光明。

值得一提的的是,作为芯片行业的重要参与者,NVIDIA 硬件工程副总裁 Ashish Karandikar在评价UCIe新标准时候谈到:“UCIe 2.0 规范的发布标志着基于芯片的系统设计发展的一个重要里程碑,它提供了一种初始化、管理和调试片上系统的标准化方法。作为 UCIe 联盟的成员,NVIDIA 致力于推进该规范的各个方面,以帮助推动下一代计算系统的创新和性能。”

推荐

-

VCSEL芯片和光学解决方案提供商瑞识科技完成近亿元B1轮融资

VCSEL芯片和光学解决方案提供商瑞识科技完成近亿元B1轮融资

2023-07-03

-

一文带你搞懂开关电源电路

一文带你搞懂开关电源电路

2024-11-02

-

阿诗特能源L1000液冷新品震撼上市,卓越性能,引领未来!

阿诗特能源L1000液冷新品震撼上市,卓越性能,引领未来!

2024-06-15

-

PLL锁相环:工作原理简述,高效同步控制的核心技术。

PLL锁相环:工作原理简述,高效同步控制的核心技术。

2024-04-07

-

模拟芯片与数字芯片各有独特优势,各具魅力,吸引你的目光。

模拟芯片与数字芯片各有独特优势,各具魅力,吸引你的目光。

2024-03-06

-

国产替代奋进高端,创新引领,开启替代新篇章。

国产替代奋进高端,创新引领,开启替代新篇章。

2024-04-07

-

本征半导体,基础材料之选,了解它,掌握电子世界的关键!

本征半导体,基础材料之选,了解它,掌握电子世界的关键!

2024-04-07

-

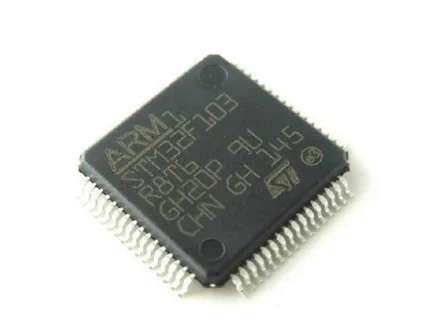

STM32单片机简介

STM32单片机简介

2023-07-26

-

高压智能电池检流器USB,HV-IBSS-USB,高效便捷,轻松检测电池状态。

高压智能电池检流器USB,HV-IBSS-USB,高效便捷,轻松检测电池状态。

2024-04-02

-

国产化加速,GE医疗MR东半球总部落户,共创医疗新篇章!

国产化加速,GE医疗MR东半球总部落户,共创医疗新篇章!

2024-03-24

最近更新

-

洲明科技LED创意显示屏亮相深圳北站

洲明科技LED创意显示屏亮相深圳北站

2025-01-16

-

日本政府斥资1600亿日元扶持本土芯片设计产业

日本政府斥资1600亿日元扶持本土芯片设计产业

2025-01-16

-

塔塔电子拟为小米、OPPO代工智能手机

塔塔电子拟为小米、OPPO代工智能手机

2025-01-16

-

先楫半导体HPM OBOX 离线烧录器正式发布

先楫半导体HPM OBOX 离线烧录器正式发布

2025-01-16

-

比亚迪日本纯电销量超丰田,市场现四年首降

比亚迪日本纯电销量超丰田,市场现四年首降

2025-01-16

-

1月手机面板行情分析

1月手机面板行情分析

2025-01-16

-

英特尔逐步淘汰第12代Alder Lake移动CPU

英特尔逐步淘汰第12代Alder Lake移动CPU

2025-01-16

-

诺基亚与三星达成电视视频技术专利许可协议

诺基亚与三星达成电视视频技术专利许可协议

2025-01-16

-

英伟达大幅削减台积电和联电CoWoS订单

英伟达大幅削减台积电和联电CoWoS订单

2025-01-16

-

TikTok或本周日全面关停美业务

TikTok或本周日全面关停美业务

2025-01-16