(文/吴子鹏)近日,有投资者在互动平台向国芯科技提问:请问贵公司是否有GPU研发计划?

对此,国芯科技回答称,“公司与上海清华国际创新中心合作开展了基于开源RISC-V指令架构的GPGPU内核研发工作,2024年7月公司已完成第一版RTL代码设计并对外公开发布。由于公司聚焦汽车电子芯片、服务器和云应用安全芯片、量子安全芯片以及AI MCU芯片的研发及设计,RISC-V GPGPU当前阶段的研发工作已结束,未来公司将视国际上开源RISC-V GPGPU技术的进一步发展情况再考虑新的研发计划安排。”

基于RISC-V做GPGPU

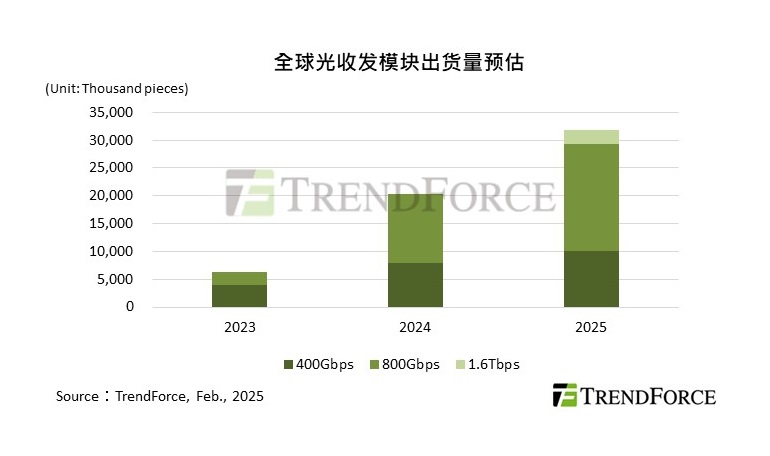

在AI大模型的推动下,目前全球算力需求增长迅猛。以中国市场为例,《全国数据资源调查报告(2023年)》显示,2023年全国2200多个算力中心的算力规模约为0.23十万亿亿次浮点运算/秒(ZFLOPS),同比增长约为30%;全国数据存储总空间为2.93ZB,存储空间利用率为59%。

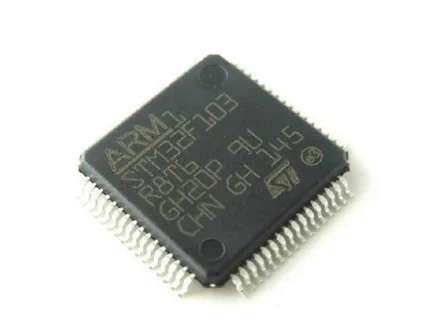

在算力芯片的供应中,根据Gartner的数据,英伟达在全球人工智能芯片市场的市占率最高可能已达到90%。目前,替代英伟达GPGPU的产品有很多,包括各种基于ARM架构的产品,尤其是ASIC形态的算力芯片。当然,也有企业选择采用RISC-V打造GPGPU。

比如,在国际市场,佐治亚理工早在2021年就研究发表了一种支持CUDA的RISC-V GPU架构——Vortex。Vortex RISC-V GPGPU旨在提供基于RV32IMF ISA的全系统RISC-V GPU。这意味着32位内核可以从1核扩展到32核GPU设计,支持OpenCL 1.2图形 API,它还支持一些CUDA操作。

国内市场,国芯科技与上海清华国际创新中心联合开发的首款基于RISC-V向量扩展(RVV)的GPGPU“Ventus(承影)”,是国内首个开源GPGPU。承影原是上海清华国际创新中心自己的科研项目,基于GPGPU编程模型进行设计,采用RISC-V向量扩展,基于LLVM开源工具链完成GPGPU编译器的开发,支持OpenCL开源并行编程框架。同时,承影参考RISC-V CPU开发思路,在满足SIMT基础功能的同时,汲取了RISC-V向量扩展在功能定义和指令设计上的优势,并将二者有机结合,使得承影同时具备向量处理器工具链兼容性和GPGPU编程灵活性,也能更好结合RISC-V编译器、打造统一指令集SoC系统。

根据相关的开源信息,承影是一个开放源码的通用并行计算(GPGPU)框架,专为高效利用现代图形处理器的计算能力而设计。它采用C++接口,并且提供了易于使用的编程模型,旨在简化GPU编程,让开发者能够更便捷地实现高性能计算任务。

承影有很多出色的特性,比如高级抽象层次,允许开发人员以相对简单的代码实现复杂的并行算法,这种抽象降低了理解和调试并行代码的复杂性,使得非GPU专家也能快速上手;拥有动态调度能力,不同于许多其他GPU框架的静态调度,承影实现了一个动态调度系统,能在运行时根据硬件状态调整任务分配,从而最大化资源利用率;灵活可定制,承影可以根据特定需求进行调整;异构计算支持特性,承影除了支持标准的GPU,还可应用于多核CPU和其他加速器,适应不同应用场景的需求。

如上所述,作为开源的且基于RISC-V架构的GPGPU,国芯科技同上海清华国际创新中心以及智绘微电子合作研发的开源RISC-V GPGPU正是基于上海清华国际创新中心“承影”GPGPU的技术基础,然后联合发展基于Verilog版本的开源RISC-V GPGPU内核技术。不过,就像除了英伟达的GPGPU之外,其他同类型的产品很难落地一样,从技术难度来说,开源RISC-V GPGPU落地的挑战更大。

这里面的挑战有很多,比如原本承影是使用Chisel HDL进行开发,然后通过make verilog命令生成Verilog代码,便于进一步的FPGA或ASIC实现,这就无形中抬高了技术门槛,比如Chisel本质上还是Scala语言,因此要学习Chisel,需要具备Scala语言的基础,而scala是一门相对较难的语言,从Chisel HDL转换到Verilog之后,名词的替换给问题定位和代码替换带来了很大的挑战。还有一个挑战是生态,无论是Chisel HDL的工具生态,还是基于RISC-V打造GPGPU的产品生态,生态都太过于狭窄,而开源是一个需要大量人员参与的项目形态。

结语

基于RISC-V实现GPGPU具有很宏大的愿景,且拥有很多独特的优势。然而,当前GPGPU所面临的算力输出场景其实并不多元,高算力、高并行、高能效是主要的需求,虽然针对不一样的模型有一定的算子需求差异,但是现阶段英伟达GPGPGU和其他同类的GPGPU,在算力丰富度方面已经很强大,RISC-V想靠灵活性和开源进去这个领域,难度确实太大了。