先进封装是“超越摩尔”(More than Moore)时代的一大技术亮点。当芯片在每个工艺节点上的微缩越来越困难、也越来越昂贵之际,工程师们将多个芯片放入先进的封装中,就不必再费力缩小芯片了。

系统级封装 (System-in-Package, SiP)

定义:将多个不同功能的芯片(如处理器、内存、传感器等)集成在一个封装中,提供一个完整的系统解决方案。

优点:

多功能集成:可以集成多个不同功能的芯片,减少PCB尺寸和系统复杂性。

空间利用率高:适合体积要求较小的设备,如智能手机、可穿戴设备等。

节省成本:通过集成多个芯片,降低了PCB的复杂性和制造成本。

三维封装 (3D Packaging)

定义:通过垂直堆叠多个芯片,并使用硅通孔(TSV)连接各层,实现在高度方向上的集成。

优点:

高性能:由于芯片之间的垂直连接,信号传输延迟降低,性能提升。

节省空间:通过垂直堆叠多个芯片,节省了横向的空间,非常适合小型设备。

高带宽与低功耗:减少了芯片之间的连接距离,提高了带宽,同时降低功耗。

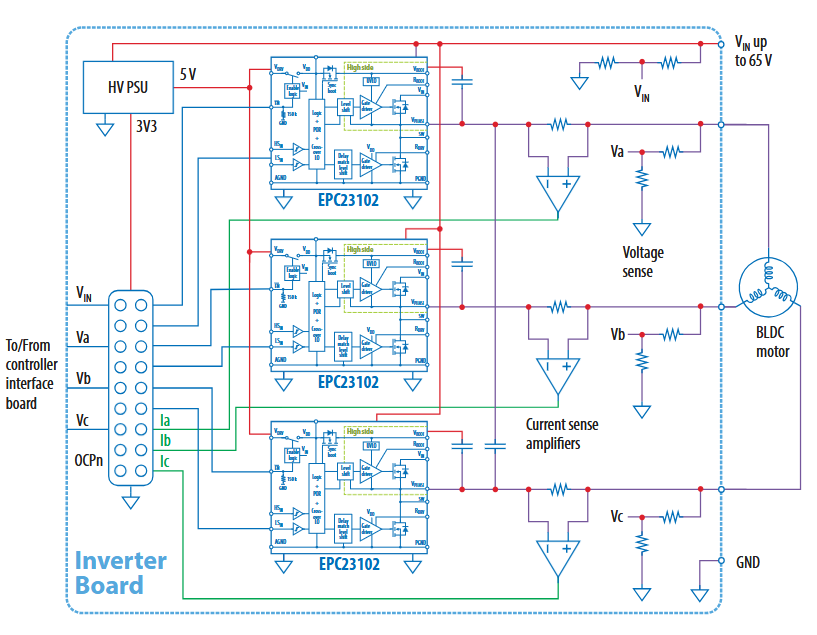

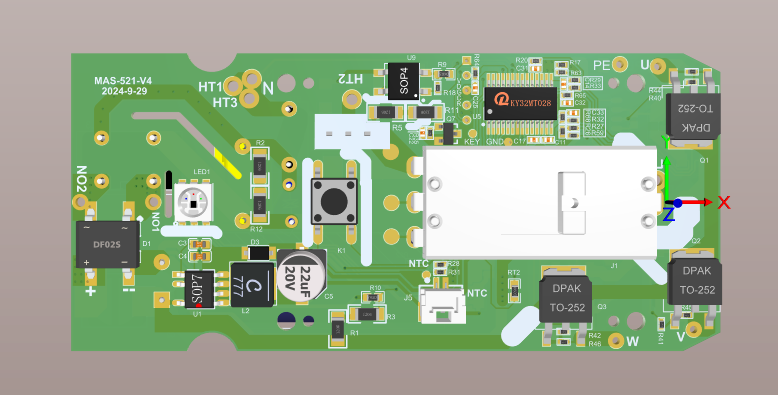

其利天下技术·无刷电机驱动方案开发

倒装芯片封装 (Flip Chip)

定义:将芯片倒装并直接焊接到基板上,而不是传统的引线封装方式。

优点:

高密度连接:通过直接焊接芯片到基板,提供更高的引脚密度,适合高性能计算。

低功耗和低信号损失:由于连接的直接性,信号传输损失和功耗都较低。

改善热管理:可以更有效地散热,因为热量可以直接从芯片传导到基板。

晶圆级封装 (Wafer-Level Packaging, WLP)

定义:在晶圆级别进行封装处理,封装过程在晶圆层面完成,避免了后续的封装步骤。

优点:

尺寸小:可以在晶圆级别完成封装,减少封装体积,非常适合移动设备。

高性能:由于直接在晶圆上进行封装,芯片与外部连接的路径更短,传输速度更快。

成本降低:生产过程简化,降低了制造成本。

埋片封装 (Embedded Die Packaging)

定义:将芯片嵌入到基板内部,而不是在基板表面。可以将多个芯片埋入到PCB层中。

优点:

节省空间:通过将芯片埋入到PCB内部,节省了空间,可以设计更小巧的产品。

提高可靠性:由于芯片被嵌入,减少了外部机械压力,提升了产品的可靠性。

更好的散热:由于埋片可以与基板直接接触,热量更容易传导和散发。

异构集成封装 (Heterogeneous Integration)

定义:将不同工艺、不同功能的芯片集成在同一个封装中,例如将模拟芯片、数字芯片、传感器等不同类型的芯片结合起来。

优点:多功能集成:可以将不同功能和工艺的芯片集成在一起,提升整体性能。

灵活性高:适用于各种不同的应用场景,如AI