Arm Neoverse 数据中心计算路线图刚刚添加了许多巧妙的东西,但其中之一不是数据中心级的离散 GPU 加速器。另一种也不存在的是更具体的矩阵数学加速器,例如英特尔(以及 Habana Labs)、SambaNova Systems、Tenstorrent、Groq 或 Cerebras Systems 创建的加速器。

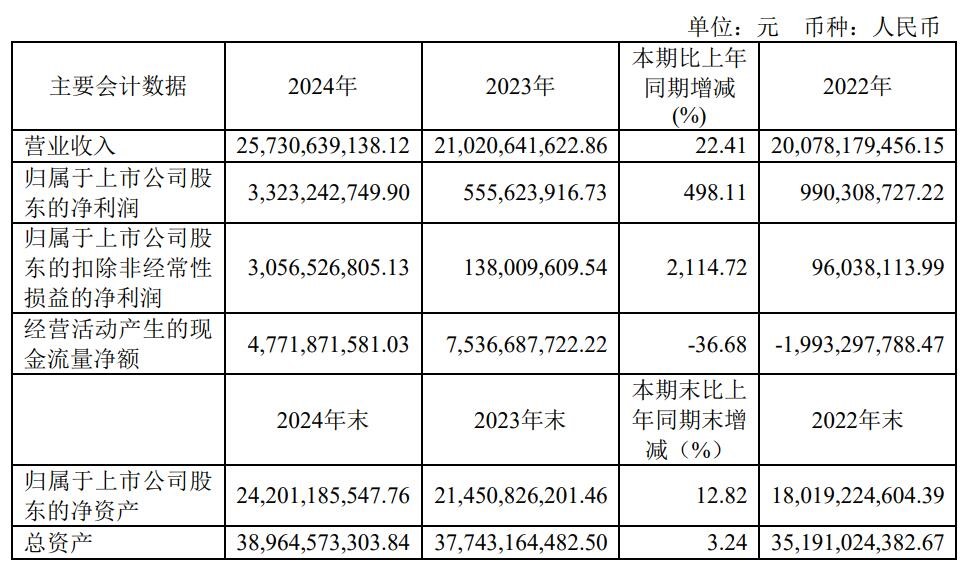

这确实是一种耻辱。

考虑到英伟达(Nvidia 几乎是 Arm Holdings 的前所有者,并且承诺如果其400 亿美元收购 Arm 的交易获得地球监管机构批准,将通过 Arm 授权工厂运行其 GPU 设计)的所有资金,收割,不是交出拳头,而是用一英亩的联合收割机,你可能会认为市场会要求 Arm 拿出一种更便宜的替代品来替代 Nvidia 现有的“Hopper”H100/H200 和即将推出的“Blackwell”B100/B200 离散产品GPU 和 AMD 现有的“Antares”Instinct MI300 和未来的 Instinct MI400 独立 GPU。

我们知道您在想什么。为什么你没有提到英特尔的独立数据中心 GPU?嗯,英特尔的“Ponte Vecchio”Max 系列 GPU,除了阿贡国家实验室“Aurora”超级计算机中的 GPU,并不是独立 GPU 领域的真正竞争者,但遗憾的是,如果英特尔现在能够生产 100 万个 GPU,那么英特尔将 Max 系列 GPU 与 Gaudi 矩阵加速器融合在一起以创造出可能具有竞争力的产品还需要很长时间。

不,这艘船早已起航,谷歌已经创建了它的 TPU,亚马逊网络服务已经创建了它的 Trainium 和 Inferentia,微软已经创建了它的 Maia,而Meta Platforms 已经在开发它的 MTIA 系列。就数据中心基础设施收入而言,近一半的市场已经在做自己的事情,尝试构建新的 GPU 或矩阵架构存在太大风险,否则 Arm 就会这么做。由于存在这种风险,我们可以说只有 Arm可以做到这一点并有成功的希望。

如果有人有勇气创建一款与 Nvidia 设备逐个兼容的 GPU,那么我们至少会因为 IBM 与 Amdahl、富士通和日立之间的大型机克隆战争重演而感到好笑——IBM 最终赢得了这场战争尽管发生了几起反垄断诉讼,或者英特尔和 AMD 之间在数据中心的 X86 架构上展开了史诗般的战斗,但顺便说一句,AMD 赢了两次。

但可惜的是,Arm 似乎没有这个胃口。其他人也没有这样做。正是因为大型机和 X86 架构所发生的事情。

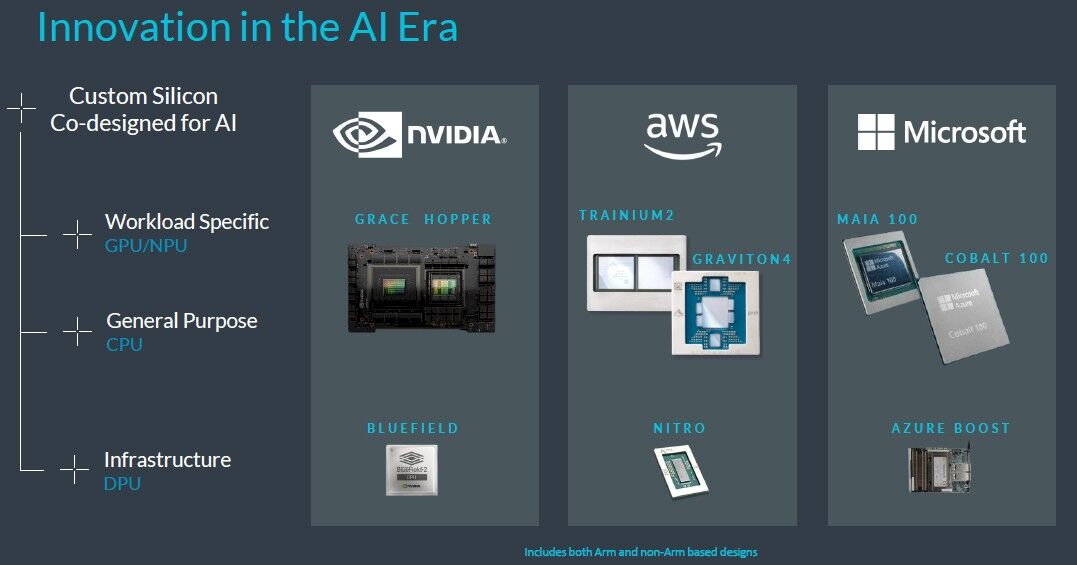

因此,Arm Holdings 本身又是一家上市公司,而且由于股票流通量微薄和非理性繁荣,它比软银母公司更有价值,它将坚持其 CPU 编织并抓住人工智能培训的任何部分并通过其 Neoverse CPU 设计进行推理。没有什么比这张图表更清楚地说明这一点了,它是我们参加的 Arm 2024 Neoverse 路线图简报的一部分:

了解你的位置。别惹麻烦。趁你还领先的时候就退出吧。

公平地说,上述所有三个 CPU 以及这些国产加速器都基于 Arm 架构,并且底部运行的三个 DPU 中至少有两个也是 Arm 架构。(我们不确定 Azure Boost,但如果里面有 CPU,几乎可以肯定它是基于某种 Arm 内核的。)这种图表在 2011 年是一个梦想,当时 Arm 开始向 X86 发起进攻。数据中心的CPU 正在认真工作。Arm CPU 在超大规模数据中心和云构建器数据中心的崛起绝对是成功的。

我们只是想要更多而已。我们认为数据中心人工智能工作负载的复杂性和独特性值得更多关注。愤世嫉俗者可能会说,英伟达愿意为 Arm Holdings 支付 400 亿美元,以阻止这家 IP 公司创造和授权杀手级 GPU,而这笔交易让 Arm 处于次要位置,而英伟达看到了 GenAI 浪潮的到来。

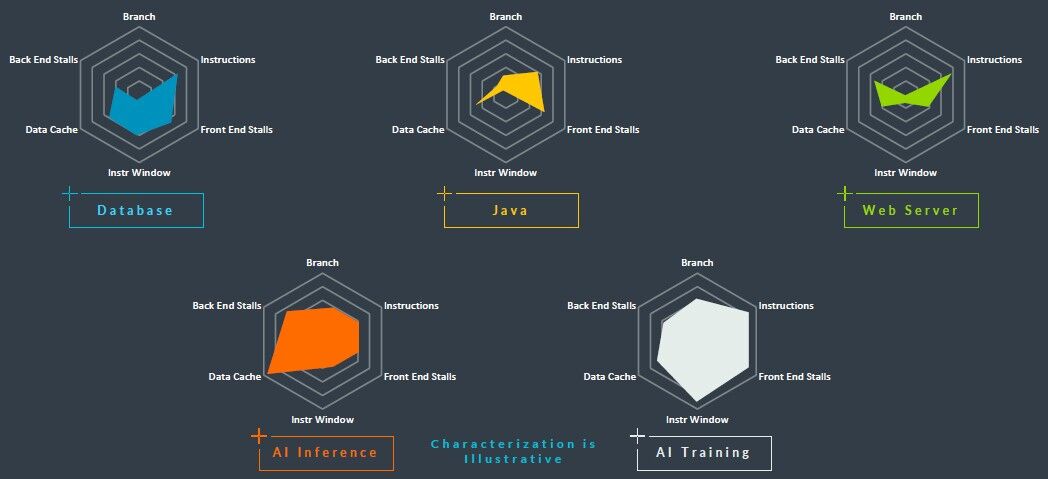

即使 Arm 自己的蜘蛛图概述了不同类型的数据中心工作负载的性能向量,也证明了更多:

唉,到了 2024 年,我们从 Arm Holdings 得到的更多是随着路线图的扩展,各种 Neoverse 核心类型的延续,以及计算子系统(CSS)许可包,这些许可包将可用于高性能 V -class 核心以及去年夏天已经发布的 N 级核心,“Genesis”知识产权围绕“Perseus”N2 核心。

Nvidia 的“Grace”CG100 和亚马逊的 Graviton4均基于“Demeter”V2 核心,我们去年夏天对此进行了深入研究。微软的 128 核 Cobalt 100 处理器基于 Genesis CSS N2 设计,我们强烈怀疑传闻中的 Google“Maple”Arm 服务器 CPU 也将基于 CSS 跳跃启动——也许是在“CSS 堆栈”上“波塞冬”V3 核心或“赫尔墨斯”N3 核心。很大程度上取决于谷歌想要实现什么目标以及何时实现。我们认为,不可避免的是,所有超大规模企业和云构建商都会在其数据中心部署混合使用 N 和 V 核心的 Arm CPU,并在边缘部署 E 核心。当然,他们也会混合使用 X86 处理器,并且这些处理器可能会在很长一段时间内占据主导地位。但是,有时变化会很快发生,所以AMD,不要满足于你的成就,英特尔,也不要满足于AMD 的成就。

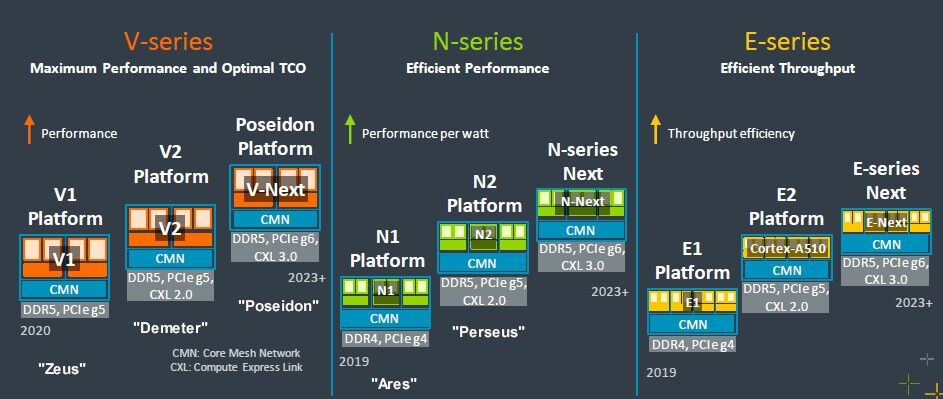

让我们深入了解 Neoverse CPU 路线图,从 2022 年 9 月的路线图开始回顾一下,因为坦率地说,它比 2024 年路线图有更多细节:

Neoverse 的努力已经有六年了,早在 2018 年 10 月,它开始的想法是每年制作一个新的核心和服务器平台,并每年完成台积电制造工艺步骤的变化。2019年的“战神”平台采用7纳米晶体管蚀刻,“宙斯”预计在2020年采用增强型7纳米工艺,“波塞冬”预计在2021年采用5纳米工艺。也许比这种时钟工作节奏更重要的是,人们期望——真的希望——在可预见的未来,Arm 能够在每一代产品中实现 30% 的性能提升(部分通过架构,部分通过功能)。

然后 Neoverse 路线图分为 N、V 和 E 核心,并且需要更多时间才能将核心投入使用。例如,Poseidon V3 核心最初预计在 2021 年推出,但现在才上市,然后在两年前的路线图中修改为更加模糊的“2023+”。这些事情需要时间,而真正推动 Neoverse 路线图的超大规模厂商和云构建商需要在全球大流行期间让他们的芯片计划井然有序,这确实扰乱了供应链和计划。

我们认为,随着 Neoverse 的发展,Arm 及其客户的发展将会更加顺利。

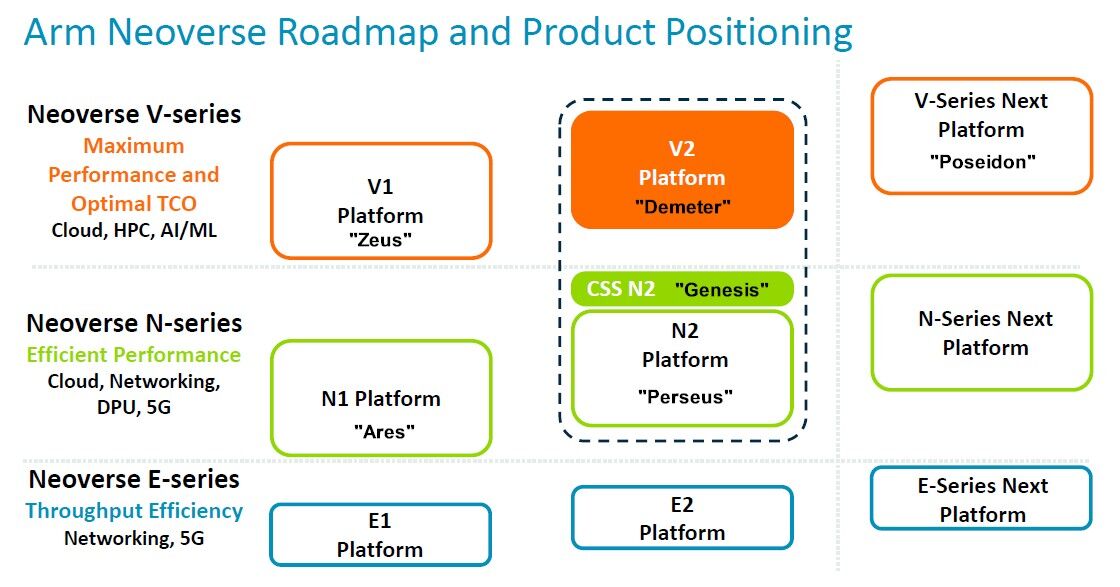

仅供参考,这是去年的 Neoverse 路线图,该路线图随 CSS 发布而发布,为了清晰起见,我们添加了代号:

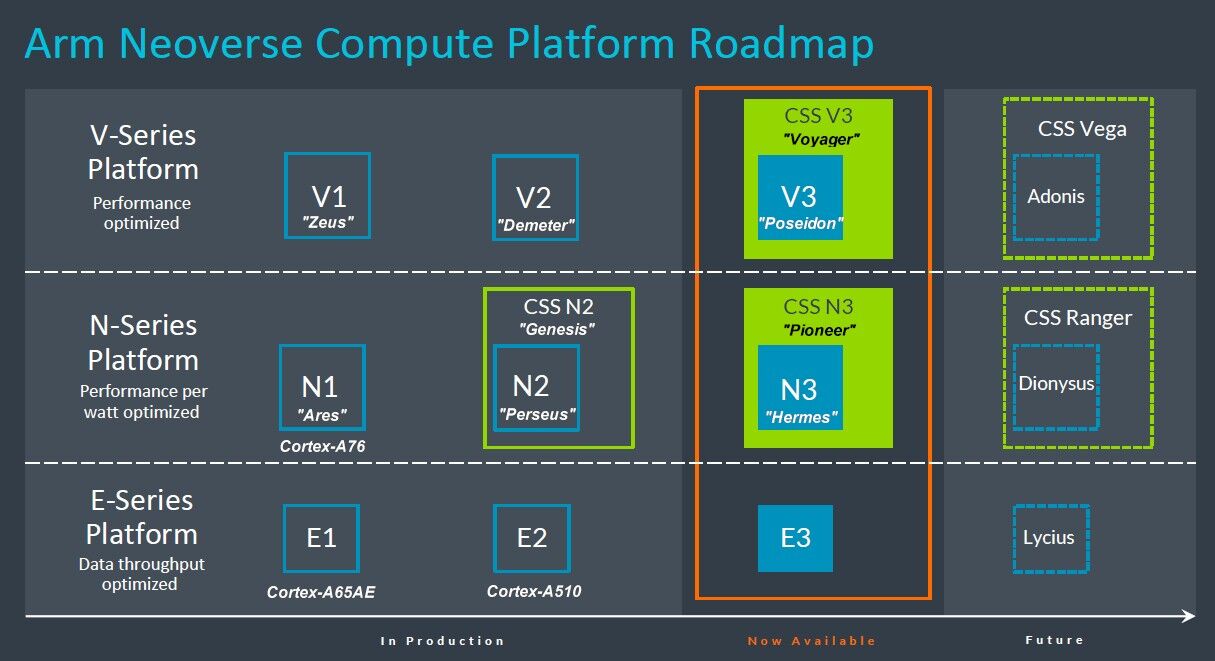

我们去年说过,Nvidia 最初部署的 Demeter V2 核心需要一个 CSS 包,但看起来这不会发生。好消息是,Poseidon 核心及其 CSS 包现已推出,Hermes N3 核心及其 CSS 包也已推出,如 2024 年 Neoverse 路线图所示:

我们不知道 N3 和 V3 CSS 包的代号是什么,但我们不会是“出埃及记”和“利未记”,这与《旧约》的书卷一致,即创世记名称所暗示的。 Neoverse N2 IP 堆栈。事实证明,它们是 CSS V3 的“Voyager”和 CSS N3 的“Pioneer”。

Arm 在 2024 年路线图上省略了 X 轴上的年份,因此我们不知道后续的“Adonis”V4 内核及其“Vega”CSS 包、后续的“Dionysus”N4 内核和他们的“Ranger”CSS 包和后续的“Lycius”E4 核心将可用。Arm Neoverse 高层将在未来承诺提供更多细节。

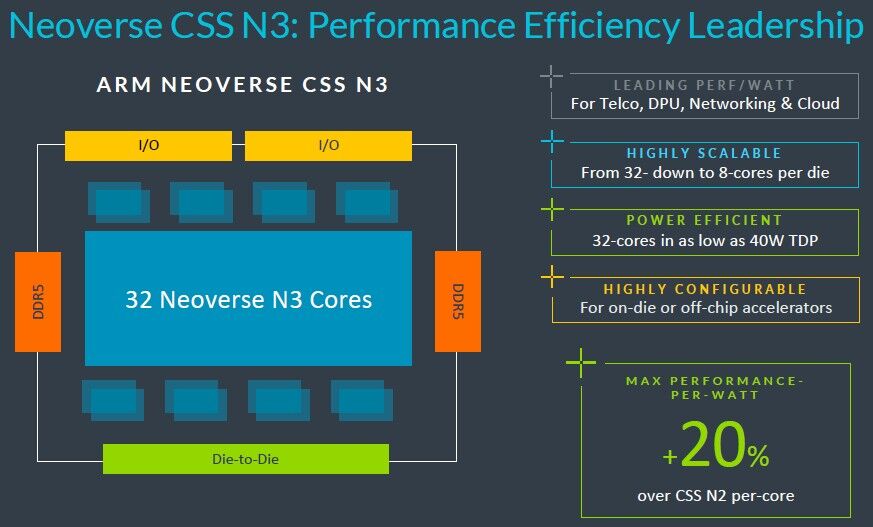

这是我们所知道的。CSS N3 封装从 32 个 N3 核心块开始,并具有一对 DDR5 内存控制器、一对 I/O 控制器和可选的芯片间互连,以创建具有我们预期的两个复合体的计算复合体粘合在一起形成一个插槽,产生 64 个核心。这些 N3 内核是根据最新的 Armv9.2 规范构建的。

N3 核心或 CSS N3 封装的工艺技术尚未公布,但我们相信它将有台积电的 5 纳米和 3 纳米以及三星和英特尔的任何类似产品可供选择。

上面的数据点表明,N3 CSS 封装可以在 40 瓦热设计点中提供 32 个内核,这强烈表明该设计将采用台积电的 3N 3 纳米工艺。

据 Arm 称,N3 封装可以缩小至 8 个内核,大概带有 1 个 DDR 控制器和 1 个 I/O 控制器。根据之前的 2022 年 9 月路线图,我们怀疑 N3 核心将被放入支持 DDR5 内存和 PCI-Express 6.0 外围控制器以及 CXL 3.0 一致性覆盖的封装中。但如果下面描述的 CSS V3 包作为指导,它可能会被限制在 PCI-Express 5.0 外设和 CXL 2.0 上。(我们并不是说确实如此。)

我们不知道 N3 核心上的矢量单元有多宽,也不知道有多少个,但如果 N3 核心要在 CPU 上进行 AI 推理和一些 AI 训练,那么 Arm 相信这将会发生– 然后,与 N2 内核相比,它们必须得到增强,N2 内核具有一对 128 位向量,每个时钟可以执行四次 FP64 操作,然后将其分解以实现混合精度性能。一个适当的矩阵数学单元——可以说是一个张量核心——也可能会被添加到 N3 核心中,但 Arm 没有透露。

Poseidon V3 核心可能会以类似的方式得到增强,如果历史有任何指导的话,其矢量和矩阵能力是 Hermes N3 核心的两倍。但我们还不知道。Zeus V1 核心有一对 256 位向量,而 Demeter V2 核心则改为四个 128 位向量;两者每个时钟执行 8 次 FP64 操作,但后一种设计效率更高。看看 V3 核心会发生什么将会很有趣。鉴于我们对 V1 核心的了解,四个 256 位向量会很奇怪,而八个 128 位向量可能听起来很奇怪,直到您意识到这正是英特尔在“Sapphire Rapids”Xeon SP CPU 中创建 AMX 矩阵数学单元的方式。

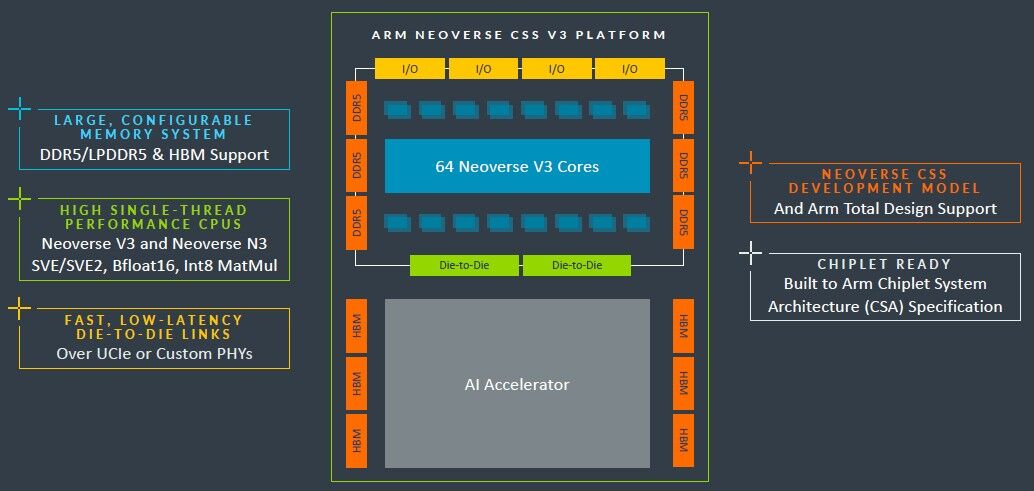

无论如何,基本 CSS V3 构建块是 64 个 V3 内核,带有 6 个 DDR% 内存控制器、4 个 PCI-Express 5.0 I/O 控制器和一对芯片间互连。2022 年 9 月的路线图告诉我们预计 V3 代将采用 PCI-Express 6.0 和 CXL 3.0。这种情况直到 V4 甚至可能是 N4 代才会发生。(也有可能 N3 首先获得 PCI-Express 6.0,而 V3 根本没有获得。)

据 Arm 称,这种 CSS V3 复合体的性能比现有的 CSS N2 复合体提高了 50%,其中两个复合体可以放入一个封装中,在单个插槽中扩展到 128 个内核。令我们惊讶的是它无法扩展到 256 个核心,但这可能是 CSS 的限制,而不是 V3 架构本身的限制。我们确信有人可以构建 256 核 V3 插槽;然而,这在技术或经济上可能没有意义。

V3 封装将支持 DDR5 内存或 HBM 堆叠内存,看看世界上是否有任何 CPU 制造商会支持 HBM 将会很有趣。为什么不?HPC 和 AI 的好处是显而易见的,当钱不是问题时(GenAI 的情况似乎如此),为什么不建造一个热棒呢?

Arm 热衷于指出 CSS V3 封装的设计目的是直接紧密地连接加速器,考虑到 Nvidia 的 Grace-Hopper 超级芯片复合体,这对 Nvidia 来说显然很重要。

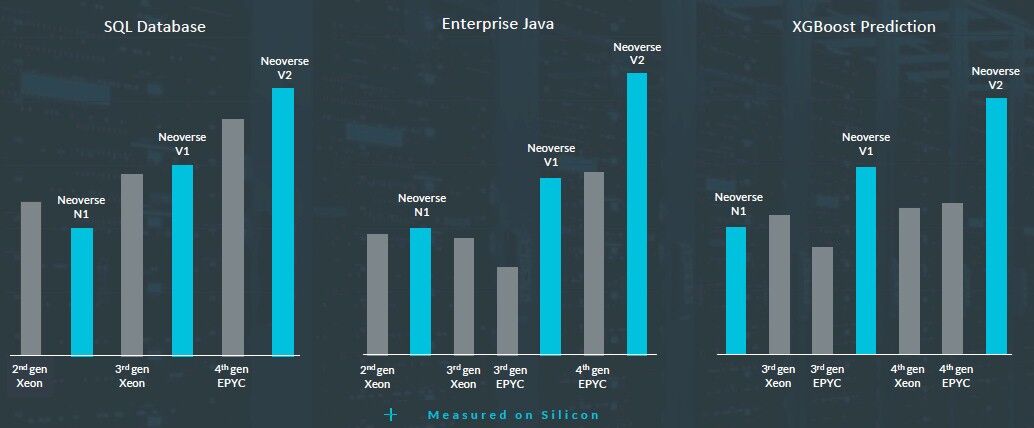

为了激发人们的兴趣,Arm 给出了 V2 内核与之前的 N1 和 V1 内核以及英特尔和 AMD 过去两代 X86 处理器的一些早期性能规格。看看这些:

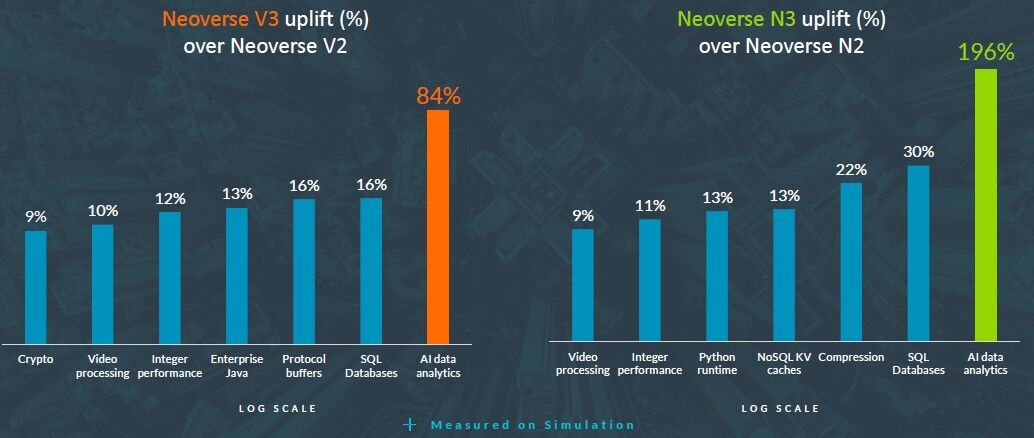

这是另一张图片,展示了 V3 如何与 V2 相比,以及 N3 如何与 N2 对比,以适应各种工作负载:

Arm 特别努力提高 XGBoost 的性能,这是一种用于进行回归、分类和预测的经典机器学习算法。

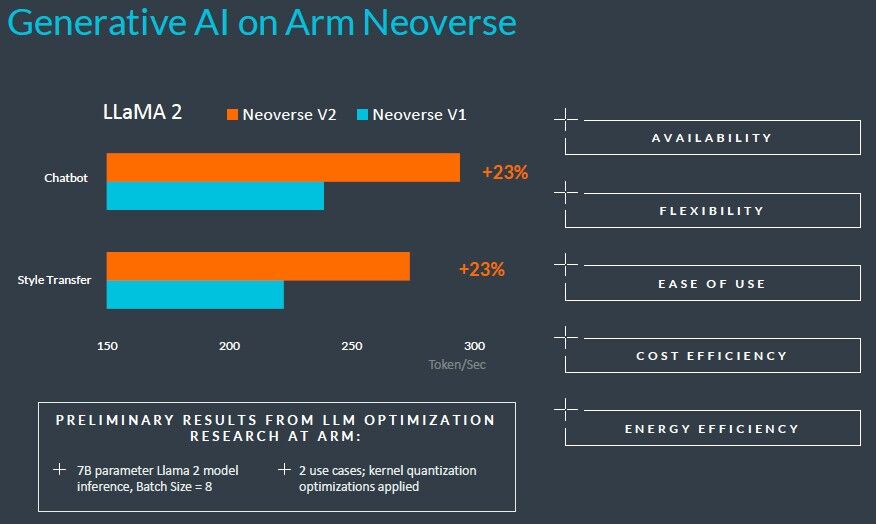

为了好玩,Arm 在相对较小的 LLaMA 2 大型语言模型(只有 70 亿个参数)上给出了一些 AI 推理基准测试:

V3设计还没有数据,这是大家都会关心的。