JEDEC 周二发布了 GDDR7 DRAM 的官方规范,这是显卡和其他 GPU 驱动设备的长期内存标准的最新版本。最新一代 GDDR 带来了内存容量和内存带宽增益的组合,后者主要由内存总线上切换到 PAM3 信号驱动。最新的图形 RAM 标准还增加了每个 DRAM 芯片的通道数量,添加了新的接口训练模式,并引入了片上 ECC 以保持内存的有效可靠性。

JEDEC 董事会主席 Mian Quddus 表示:“JESD239 GDDR7 标志着高速内存设计的重大进步。“随着向 PAM3 信号的转变,内存行业有了一条新的途径来扩展 GDDR 设备的性能并推动图形和各种高性能应用的不断发展。”

GDDR7 已经开发了几年,大约一年前,JEDEC 成员首次披露了该内存技术,当时Cadence 透露使用 PAM3 编码作为其验证工具的一部分。从那时起,我们从多家 内存制造商处得知,我们预计该内存的最终版本将于 2024 年推出,而 JEDEC 的发布基本上如期进行。

正如之前透露的,GDDR7 最大的技术变化是内存总线上的两位不归零 (NRZ) 编码转换为三位脉冲幅度调制 (PAM3) 编码。这一变化允许 GDDR7 在两个周期内传输 3 位数据,比在相同时钟速度下运行的 GDDR6 多传输 50% 的数据。因此,GDDR7 可以支持更高的总体数据传输速率,这是使每一代 GDDR 连续比其前身更快的关键组件。

| GDDR世代 | |||||

| GDDR7 | GDDR6X (非 JEDEC) |

GDDR6 | |||

| 每个引脚黑白 | 32 Gbps(第 1 代) 48 Gbps(规格最大值) |

24 Gbps(运输) | 24 Gbps(采样) | ||

| 芯片密度 | 2GB(16GB) | 2GB(16GB) | 2GB(16GB) | ||

| 总黑白(256 位总线) | 1024 GB/秒 | 768 GB/秒 | 768 GB/秒 | ||

| 内存电压 | 1.2V | 1.35V | 1.35V | ||

| 数据速率 | 量子DR | 量子DR | 量子DR | ||

| 信令 | PAM-3 | PAM-4 | NRZ(二进制) | ||

| 最大密度 | 64GB | 32GB | 32GB | ||

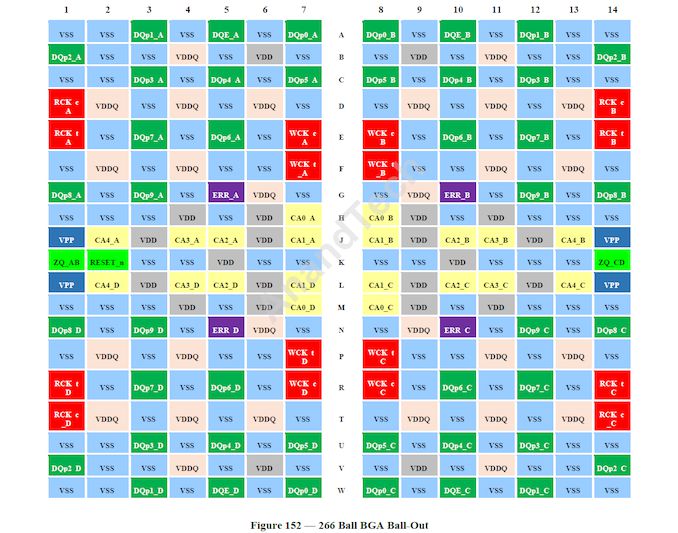

| 包装 | 266 FBGA | 180 FBGA | 180 FBGA | ||

第一代 GDDR7 预计将以每个引脚 32 Gbps 左右的数据速率运行,内存制造商此前曾表示,高达 36 Gbps/引脚的速率很容易实现。然而,GDDR7 标准本身为更高的数据速率(高达 48 Gbps/pin)留出了空间,JEDEC 甚至在其新闻稿中宣称 GDDR7 内存芯片“每台设备的速率高达 192 GB/s [32b @ 48Gbps]” 。值得注意的是,这比 PAM3 信号本身带来的带宽增加要高得多,这意味着 GDDR7 的设计中有多个级别的增强。

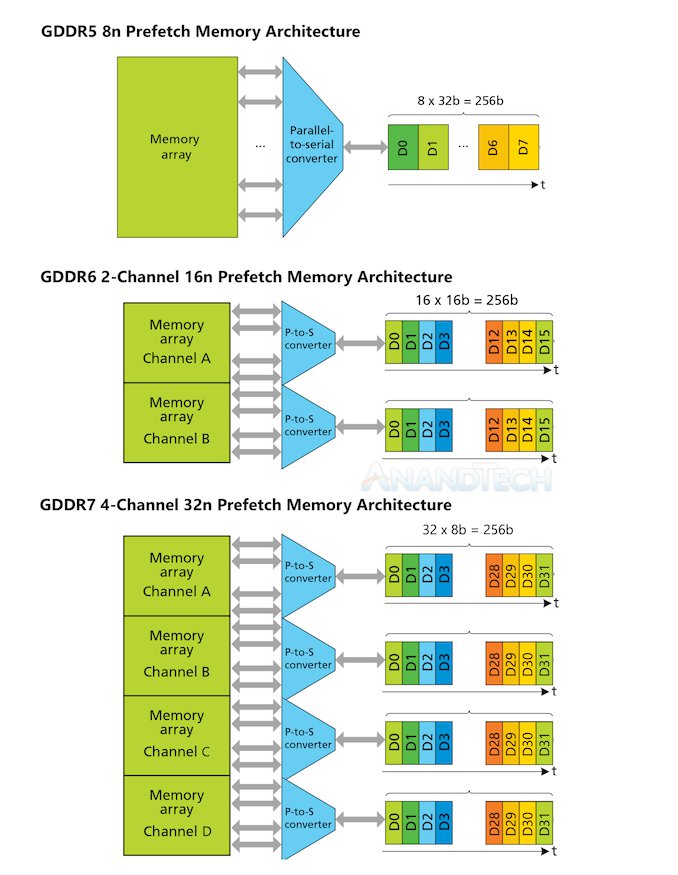

深入研究规范,JEDEC 还再次将单个 32 位 GDDR 内存芯片细分为更多数量的通道。GDDR6 提供两个 16 位通道,而 GDDR7 将其扩展为四个 8 位通道。从最终用户的角度来看,这种区别有些随意——无论如何,它仍然是一个以 32Gbps/引脚运行的 32 位芯片——但它对芯片内部的工作方式有很大影响。特别是 JEDEC 保留了 GDDR5 和 GDDR6 的每通道 256 位预取,使 GDDR7 成为 32n 预取设计。

所有这些的最终影响是,通过将通道宽度减半但保持预取大小相同,JEDEC 有效地将 DRAM 单元每个周期预取的数据量增加了一倍。这是扩展 DRAM 内存带宽的非常标准的技巧,本质上与 JEDEC 在 2018 年对 GDDR6 所做的事情相同。但它提醒我们,DRAM 单元的速度仍然非常慢(大约数百 MHz)并且速度并没有变得更快。因此,提供更快内存总线的唯一方法是一次性获取越来越多的数据。

每个内存芯片通道数量的变化对于多通道“翻盖”模式如何适用于更高容量的内存配置也有较小的影响。GDDR6 从翻盖配置中的每个芯片访问单个内存通道,而 GDDR7 将访问两个通道 - JEDEC 称之为双通道模式。具体来说,该模式从每个芯片读取通道A和C。它实际上与 GDDR6 翻盖模式的行为方式相同,这意味着虽然最新一代内存仍然支持翻盖配置,但除了不断增加的内存芯片密度之外,没有采用任何其他技巧来提高内存容量。

值得注意的是,GDDR7 标准正式增加了对 64Gbit DRAM 设备的支持,是 GDDR6/GDDR6X 最大容量 32Gbit 的两倍。还继续支持非二次方容量,支持 24Gbit 和 48Gbit 芯片。对更大内存芯片的支持进一步将具有 384 位内存总线的高端显卡理论上的最大内存容量推至高达 192GB,这一发展无疑会受到大容量时代数据中心运营商的欢迎。语言人工智能模型。尽管如此,尽管 GDDR6 支持 32Gbit 芯片,但我们仍然经常看到当今的存储卡上使用 16Gbit 内存芯片。再加上三星和美光已经透露他们的第一代 GDDR7 芯片也将分别达到 16Gbit/24Gbit,可以肯定地说,64Gbit 芯片现在还很遥远(所以不要卖)还没有使用 48GB 卡)。

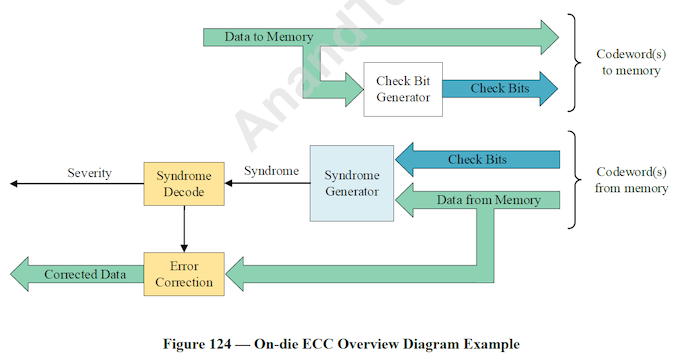

对于最新一代的内存技术,JEDEC 还包括了多项新的 GDDR 内存可靠性功能。最值得注意的是,片上 ECC 功能,类似于我们在 DDR5 推出时看到的功能。虽然我们还没有得到 JEDEC 的官方评论,说明他们为什么现在选择包含 ECC 支持,但考虑到 DDR5 的可靠性要求,包含 ECC 支持并不令人意外。简而言之,随着存储芯片密度的增加,生产没有缺陷的“完美”芯片变得越来越困难;因此,添加片上 ECC 可以让内存制造商在遇到不可避免的错误时保持其芯片可靠运行。

在内部,GDDR7 规范要求每 256 位用户数据至少有 16 位奇偶校验数据 (6.25%),JEDEC 给出了 9 位单纠错码 (SEC) 加上 7 位循环冗余的示例实现检查(CRC)。总体而言,GDDR7 片上 ECC 应能够纠正 100% 的 1 位错误,并检测 100% 的 2 位错误 - 在罕见的 3 位错误情况下,检测率降至 99.3%。有关内存错误的信息也可通过 JEDEC 称之为片上 ECC 透明协议的方式提供给内存控制器。虽然在技术上与 ECC 本身是分开的,但 GDDR7 还引入了另一个内存可靠性功能,即具有命令阻塞功能的命令地址奇偶校验 (CAPARBLK),旨在提高命令地址总线的完整性。

否则,虽然包含片上 ECC 对消费者显卡的影响可能不会比其对 DDR5 内存和消费者平台的影响更大,但这对工作站和服务器意味着什么还有待观察视频卡。那里的供应商已经在未受保护的内存上使用软 ECC 了好几代了;想必这对于 GDDR7 卡来说也是如此,但软 ECC 的定期使用使得事情比 CPU 领域更加灵活。

最后,GDDR7 还引入了一系列其他与可靠性相关的功能,主要与帮助 PAM3 操作相关。这包括具有眼图掩蔽和错误计数器的核心独立 LFSR(线性反馈移位寄存器)训练模式。LFSR 训练模式用于测试和调整接口(以确保效率),眼图掩蔽评估信号质量,错误计数器跟踪训练期间的错误数量。

抛开技术问题不谈,本周的公告还包括来自两岸所有主要参与者的支持声明,包括 AMD 和 NVIDA,以及美光/三星/SKhynix 三巨头。不言而喻,鉴于 GDDR7 带来的内存容量和带宽改进,各方都热衷于分别使用或销售 GDDR7,尤其是在这个任何针对 AI 市场的产品都热销的时代。

目前尚未公布具体产品,但由于三星和美光此前已宣布打算在今年推出 GDDR7 内存,因此我们应该会在今年晚些时候看到新的内存(以及与其配对的新 GPU)。