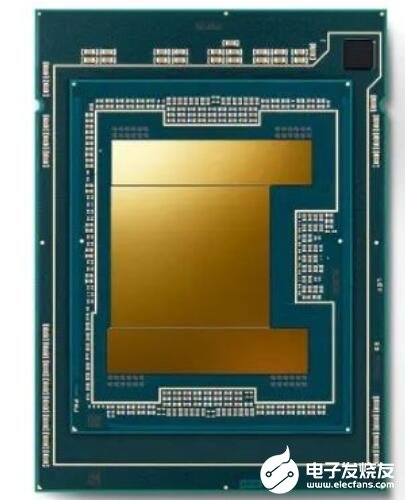

近来,全球领先的集成电路设计企业Marvell宣布,他们已成功推出了一款基于台积电先进的3纳米制程技术的数据中心芯片,这一壮举标志着首个应用于数据基础设施领域的3纳米级芯片正式问世。

依据台积电先前的阐述,与五纳米工艺相比,三纳米工艺在逻辑元件密度方面实现了显著增长,大约提升了七成;同时,在保持功耗不变的情况下,其运行速度有望加速至百分之十到十五的程度,或是在同等运行速度前提下,能大幅削减约百分之二十五到三十的能耗。

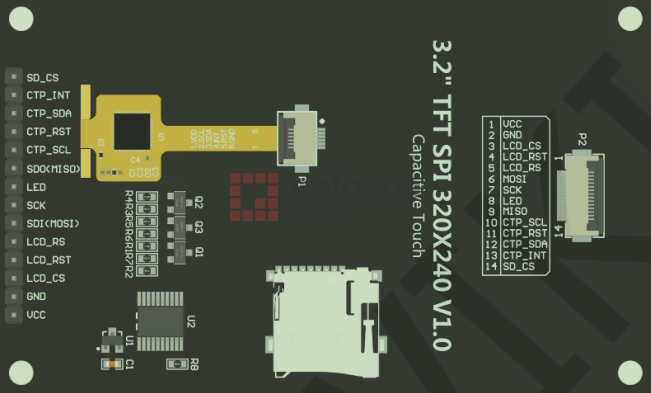

台积电的三纳米芯片被巧妙地应用于各类新产品的构思之中,不仅包含了核心的基础IP构件,还集成了112G XSR SerDes、远程距离SerDes、PCIe Gen 6 PHY/CXL 3.0 SerDes以及高达240 Tbps的芯片对芯片互联技术等。这一系列先进的组件为产品设计提供了卓越的技术支撑与强大的性能保障,使得研发出具有高效率、高速度和高可靠性的创新产品成为可能。

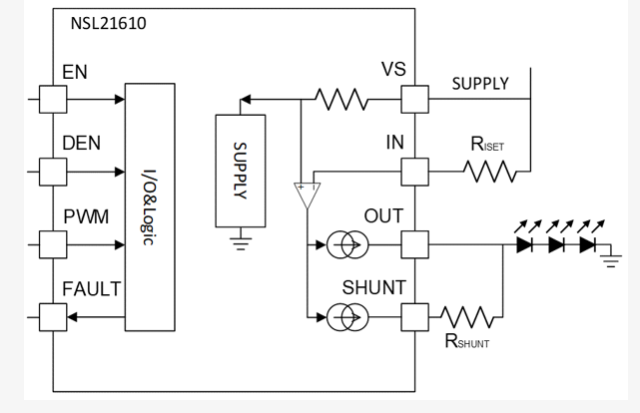

正如Marvell所阐述的那样,Serializer/Deserializer与并行互连共同构筑起高速数据传输的桥梁,专门用于芯片级或硅组件之间的信息交换。在2.5D及3D封装技术的支持下,这些架构有效解决了系统层面的性能局限,为复杂半导体设计铺平了道路。更值得称赞的是,鉴于大规模数据中心机架内可能集成成千上万条SerDes链路,该技术不仅加速了数据流通,还巧妙地减少了引脚、连线与电路板的空间需求,从而在成本控制方面展现出卓越的效能。

全新的并行芯片间互联技术,实现了惊人的240Tbps数据聚合传输速度,较现有的多芯片封装解决方案领先了45个百分点。想象一下,这等同于每一秒钟能够下载数以万计的高清电影,即便互联设备之间的物理距离仅咫尺之间,乃至更短。

Marvell已将先进的SerDes与互连技术融入其顶尖级半导体解决方案之中,这其中包括了Teralynx交换机、采用PAM4及相干DSP的信号处理单元、用于以太网物理层通信的Alaska设备、OCTEON处理器、Bravera存储控制器、Brightlane汽车以太网组件以及定制化的ASIC。通过迁移到3纳米制程,我们可以有效降低芯片与计算系统的成本和能耗,并且确保其讯号完整性及性能维持在最顶尖水平。