1.1 VESA 视频标准

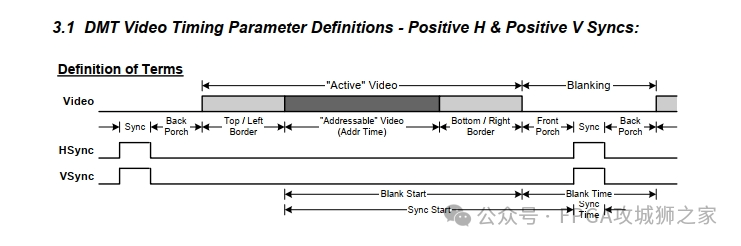

VESA 视频标准同步信号产生器,是从事FPGA图像领域工程师经常使用到的模块。首先,它的标准时序来自 VESA 视频标准文件。

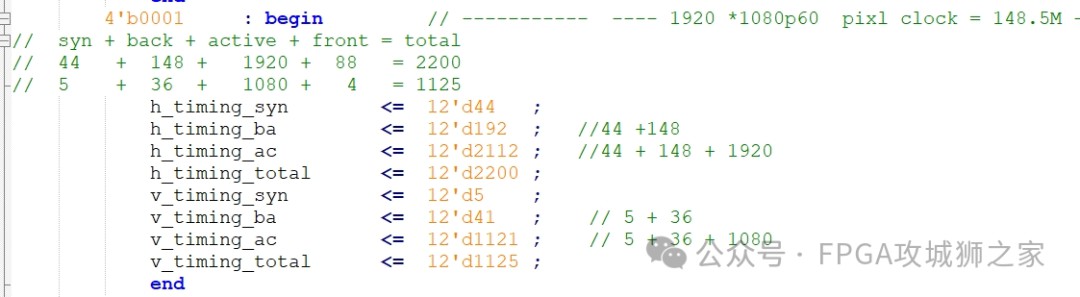

里面规定了VESA视频流同步信号的时序,以1080p为例可以查询到具体情况如下图,

1.2 产生视频流同步信号

那么依照这个视频流可以在FPGA中产生标准时序,首先将这些参数添加进去,看注释中数据,就知道怎么填了。这样任意的分辨率都可以产生了。

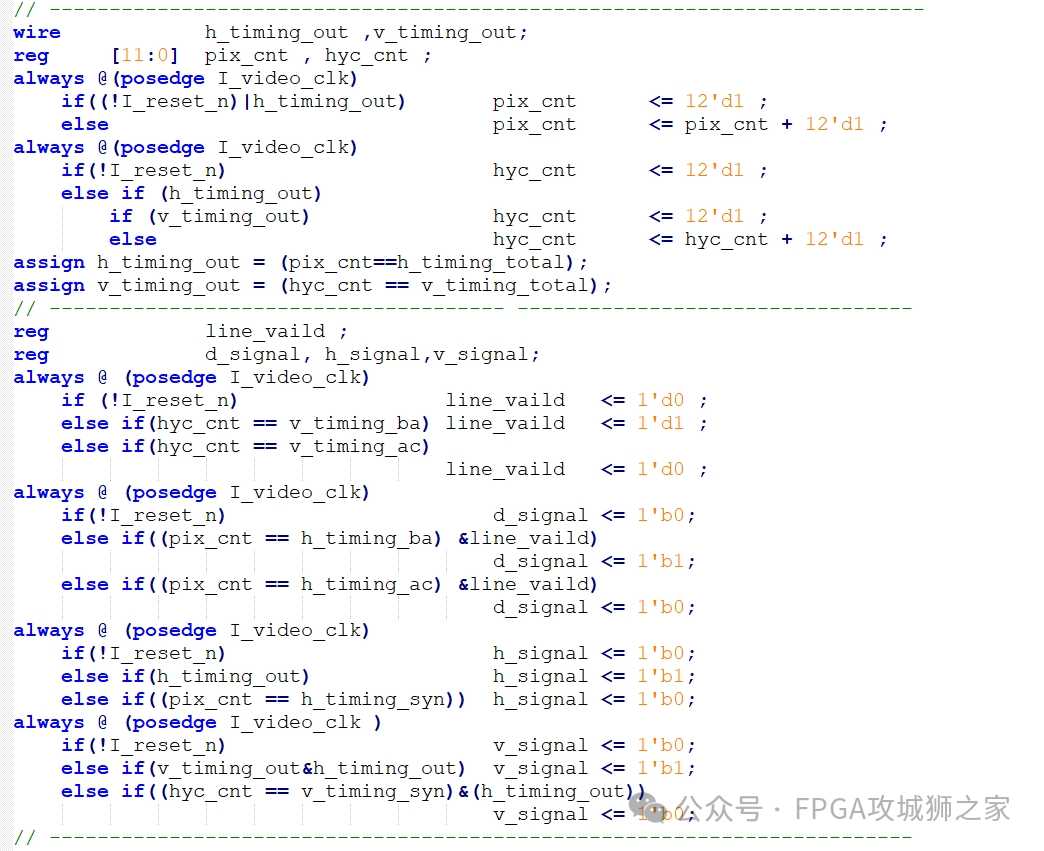

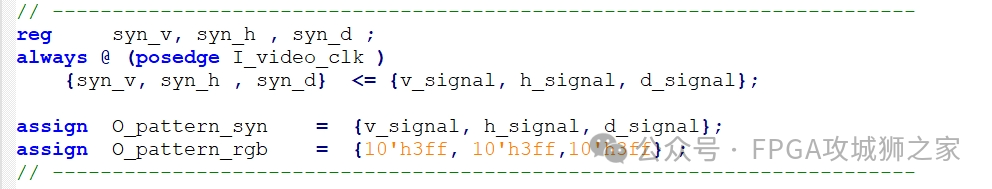

然后利用这个参数产生同步信号,自此任意同步信号产品器就完成了。有人会说,这个东西,不就是xilinx官方的IP VTC 嘛,干嘛要重复造轮子。嘿嘿,那是因为,一,我们在做图像处理的时候要尽量的避免使用vivado这个仿真器,因为它实在是太墨迹了。二,如果是1080p以上的分辨率,比如4k,8k,的视频流,它在FPGA里面是双点,四点模式的,VTC没有这个功能,这个就要靠自己去实现了。

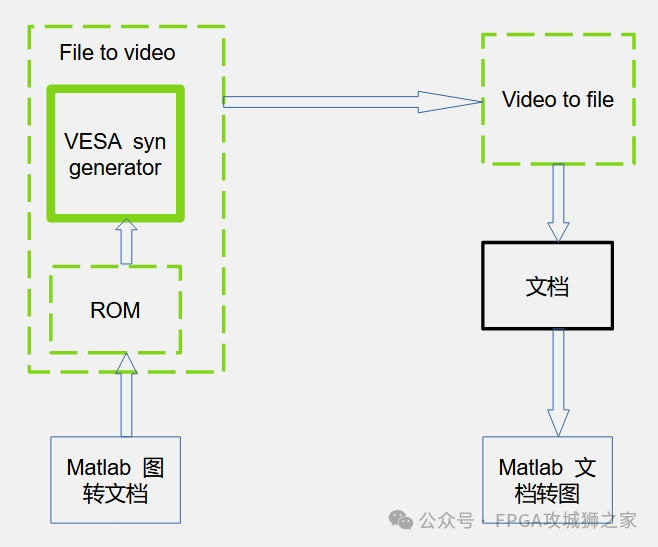

1.3 图导入FPGA

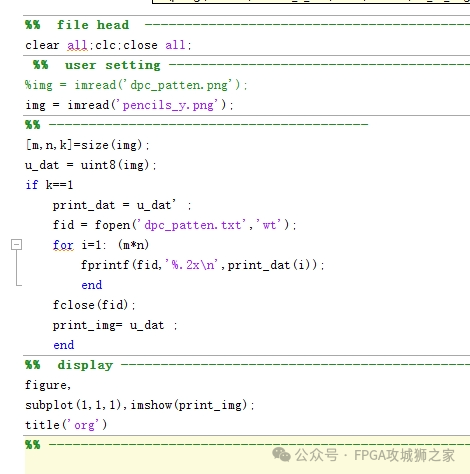

首先需要把图转换成txt,这个可以利用matlab,

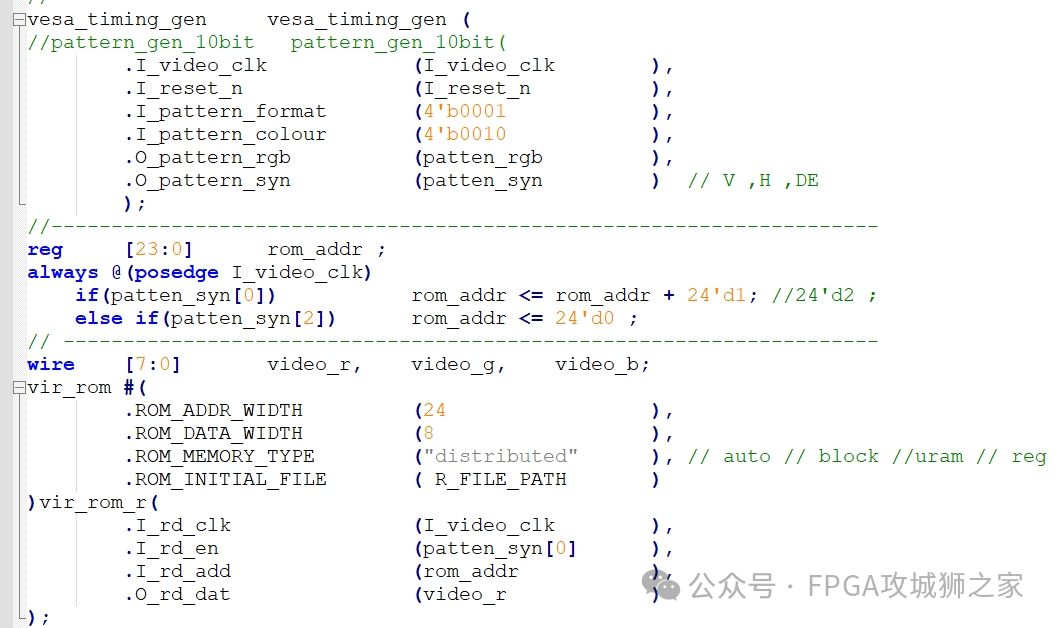

这是一张黑白图导入到matlab中,然后再保存到txt中的程序。然后在FPGA中将txt导入到rom,利用VESA视频流同步信号产生器,虚拟一条视频输入到代码中。

vir_rom 就是一个虚拟的rom。利用VESA视频流同步信号产生rom读地址,从而把rom中的图像数据导出来。

1.4 视频到文件

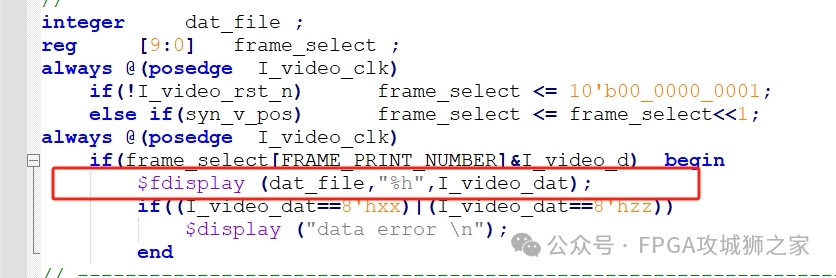

仿真的下半场,就是将视频流存入到文件中,这里需要写一个视频保存文件,选择其中一帧保存下来。此时modelsim会产生一个txt文件,保存我们所需要的数据。

1.5 txt到图像。

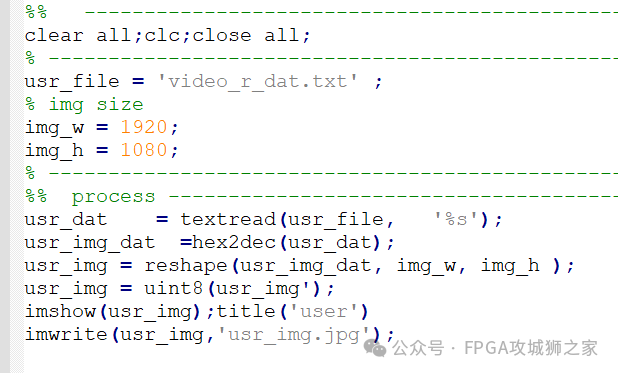

当我们拿到了modelsim里面的仿真视频流一帧的文件txt,直接读入到matlab里面去就好了。几行代码就完成了华丽的转换。

自此,测试图产生器就完成了。既可以放到可综合项目中,也可以放到仿真工程中使用。自此,这个结构图里面的内容就完成了。

推荐

-

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

2025-05-01

-

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

2025-05-01

-

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

2025-05-01

-

一文解析电磁场与电磁波的区别

一文解析电磁场与电磁波的区别

2025-05-01

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

详解CPU 的大小端模式

详解CPU 的大小端模式

2025-05-01

-

超详细解析!电阻在电路中的作用

超详细解析!电阻在电路中的作用

2025-05-01

最近更新

-

洲明科技再登“中国最具价值品牌500强”

洲明科技再登“中国最具价值品牌500强”

2025-05-21

-

帝奥微AMOLED显示屏电源管理芯片DIO53010简介

帝奥微AMOLED显示屏电源管理芯片DIO53010简介

2025-05-21

-

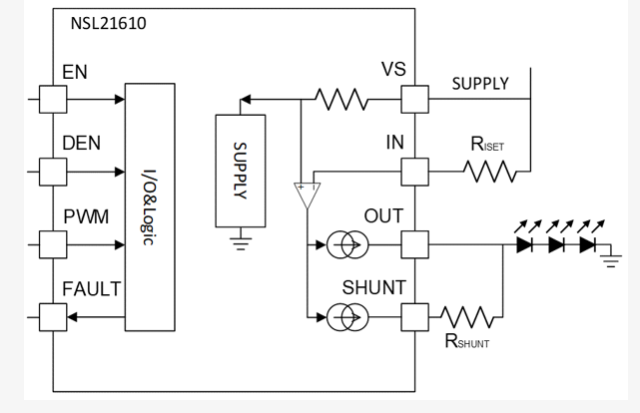

纳芯微LED线性恒流驱动NSL21610 汽车级40V/单通道具备散热加强功能

纳芯微LED线性恒流驱动NSL21610 汽车级40V/单通道具备散热加强功能

2025-05-21

-

极海半导体GALT61120汽车前灯LED矩阵控制芯片荣获AEIF 2025 金芯奖

极海半导体GALT61120汽车前灯LED矩阵控制芯片荣获AEIF 2025 金芯奖

2025-05-21

-

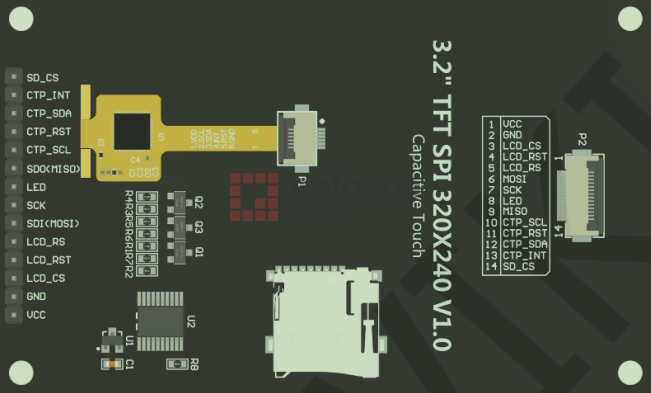

使用恩智浦FRDM LCD模组

使用恩智浦FRDM LCD模组

2025-05-21

-

【CW32模块使用】1.8寸彩色触摸屏

【CW32模块使用】1.8寸彩色触摸屏

2025-05-21

-

正方科技欧荷18S30AH智能电池在大载重无人机中的应用

正方科技欧荷18S30AH智能电池在大载重无人机中的应用

2025-05-21

-

广和通发布5G模组FG390系列

广和通发布5G模组FG390系列

2025-05-21

-

2025年OBC的新趋势:单级拓扑

2025年OBC的新趋势:单级拓扑

2025-05-21

-

谷歌I/O 2025大会前透露:Android 16接入Gemini,智能手机、XR设备升级

谷歌I/O 2025大会前透露:Android 16接入Gemini,智能手机、XR设备升级

2025-05-21