FPGA设计是无情的,所以我们需要利用能获得的任何软件进行检查。Verilator是一个 Verilog 仿真器,还支持 linting:静态分析设计中的问题。Verilator 不仅可以发现综合工具可能忽略的问题,而且运行速度也很快。Verilator 也非常适合使用 SDL 进行图形仿真。

安装Verilator,Linux,Verilator 在大多数 Linux 发行版存储库中都可用,并适用于 Windows 子 Linux 系统上运行。

对于 Debian 和基于 Ubuntu 的发行版,可以使用 apt 安装 Verilator>

苹果系统,在 macOS 上,可以通过Homebrew包管理器安装最新版本的 Verilator >

要为其他平台(例如 FreeBSD)安装 Verilator,请参阅官方Verilator 安装指南。

基本 Linting,对于独立模块,linting 本身就很简单>

如果一切顺利,将不会看到来自 Verilator 的消息。

如果 Verilator 发现潜在问题,它会提供明确的建议,包括如何禁用警告。Verilator 手册包含可能的警告列表。

让我们创建一个简单的“add”模块,并设置几个问题,然后对其进行 lint>

进行lint检查,第一个问题是宽度:x和y是 4 位宽,但z没有明确的宽度,因此只有 1 位宽。

我们可以通过这样做来忽略宽度警告>

这仅仅是隐藏了问题,却没有采取任何措施。

相反,我们可以通过将z的宽度设置为 4 来修复该问题>

虽然这消除了 Verilator 警告,但可能无法完全解决问题。

例如,如果x和y都是4'b1000,会发生什么?我们的加法溢出,计算出z值4'b0000。此示例说明了 linting 的局限性之一:它可以查看不同信号的宽度,但无法解释应用于它们的所有逻辑。

因此,除了固定z的宽度外,我们还可以将其用作c进位信号,这也解决了“信号未驱动”警告>

依赖关系和路径,如果一个模块依赖于另一个模块会发生什么?Verilator 将在当前路径中搜索匹配的模块。如果想向模块搜索路径添加其他目录,我们可以使用-I. 例如,如果top.v依赖于../maths目录中的模块>

可以使用多个-I参数来包含多个目录。

黑匣子和空模块,大多数设计依赖于没有源的供应商原语或 IP 核,例如使用 PLL 生成时钟。当尝试对引用供应商原语的模块进行 lint 处理时,将收到如下错误>

第一个想法可能是找到一种排除MMCME2_BASElint 的方法。唉,Verilog “不经过精心设计就无法检查,需要整个设计”。我们可以通过为原语创建一个空模块来解决这个问题。空模块包含 IO,但不包含任何逻辑。

例如,为 Xilinx 的 BUFG 原语创建了一个空模块>

创建空模块有点乏味,但可以检查整个设计。要使用 null 模块,请确保它位于 Verilator 的搜索路径中(请参阅上一节)。

Linting Waivers,如果需要对较大的设计或使用第三方源的设计消除 linter 警告,那么/* verilator lint_off */注释可能不行。从 Verilator 4.028 开始,可以创建Waivers来处理警告,而无需触及源代码。要了解更多信息,请参阅 Stefan Wallentowitz 的帖子Verilator Waivers(https://wallento.cs.hm.edu/post/20200612-verilator-waivers/)。

Linting Shell Script,如果有许多顶级模块和/或包含目录,可以使用 Makefile 或简单的 shell 脚本自动检查。

以下 shell 脚本 lint 与该脚本位于同一目录中的所有顶级模块>

可以调整-I参数以适合自己的设置。top_*.*v捕获扩展名为 .v 和 .sv 的文件。

总结,今天关于Verilator 进行 Verilog Lint介绍就这样,这是一个功能强大的工具,希望有兴趣的可以尝试一下

推荐

-

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

2025-05-01

-

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

2025-05-01

-

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

2025-05-01

-

一文解析电磁场与电磁波的区别

一文解析电磁场与电磁波的区别

2025-05-01

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

详解CPU 的大小端模式

详解CPU 的大小端模式

2025-05-01

-

超详细解析!电阻在电路中的作用

超详细解析!电阻在电路中的作用

2025-05-01

最近更新

-

洲明科技再登“中国最具价值品牌500强”

洲明科技再登“中国最具价值品牌500强”

2025-05-21

-

帝奥微AMOLED显示屏电源管理芯片DIO53010简介

帝奥微AMOLED显示屏电源管理芯片DIO53010简介

2025-05-21

-

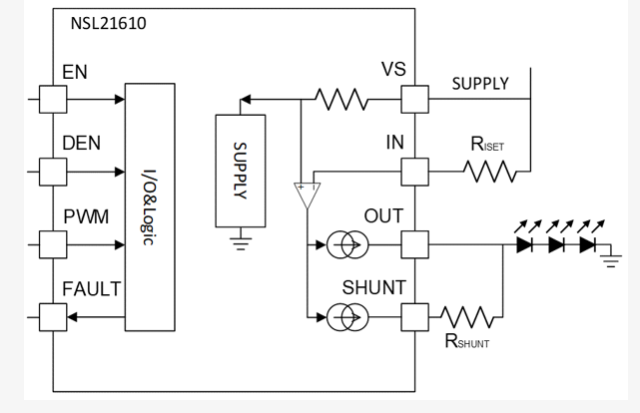

纳芯微LED线性恒流驱动NSL21610 汽车级40V/单通道具备散热加强功能

纳芯微LED线性恒流驱动NSL21610 汽车级40V/单通道具备散热加强功能

2025-05-21

-

极海半导体GALT61120汽车前灯LED矩阵控制芯片荣获AEIF 2025 金芯奖

极海半导体GALT61120汽车前灯LED矩阵控制芯片荣获AEIF 2025 金芯奖

2025-05-21

-

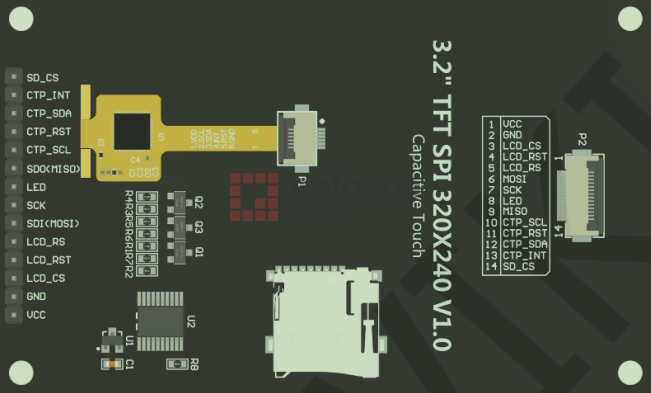

使用恩智浦FRDM LCD模组

使用恩智浦FRDM LCD模组

2025-05-21

-

【CW32模块使用】1.8寸彩色触摸屏

【CW32模块使用】1.8寸彩色触摸屏

2025-05-21

-

正方科技欧荷18S30AH智能电池在大载重无人机中的应用

正方科技欧荷18S30AH智能电池在大载重无人机中的应用

2025-05-21

-

广和通发布5G模组FG390系列

广和通发布5G模组FG390系列

2025-05-21

-

2025年OBC的新趋势:单级拓扑

2025年OBC的新趋势:单级拓扑

2025-05-21

-

谷歌I/O 2025大会前透露:Android 16接入Gemini,智能手机、XR设备升级

谷歌I/O 2025大会前透露:Android 16接入Gemini,智能手机、XR设备升级

2025-05-21