分治法是经典优化算法之一。分治分治,即分而治之。分治,就是把一个复杂的问题分成两个或更多的相同或相似的子问题,再把子问题分成更小的子问题……直到最后子问题可以简单的直接求解,原问题的解即子问题的解的合并。

分治法的思想我们也可以用在FPGA开发中,使得设计更加高效。

本文以 leading zero count 为例来看一下分治法的应用。

这个题目是计算一个 vector 的 leading zero 的数目。比如 8'b00001111,结果为4,而8'b00111111,结果为2。

Casex 优先级选择器,我们可以用最简单的 casex 优先级选择器来实现。假设输入的vector位宽为64。

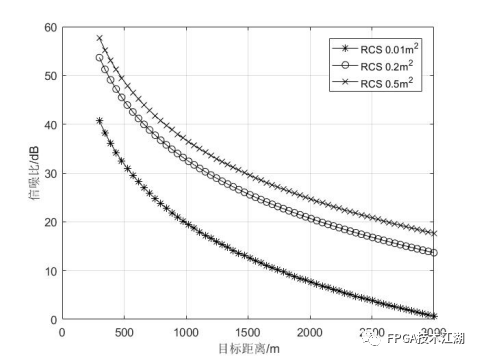

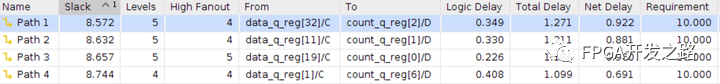

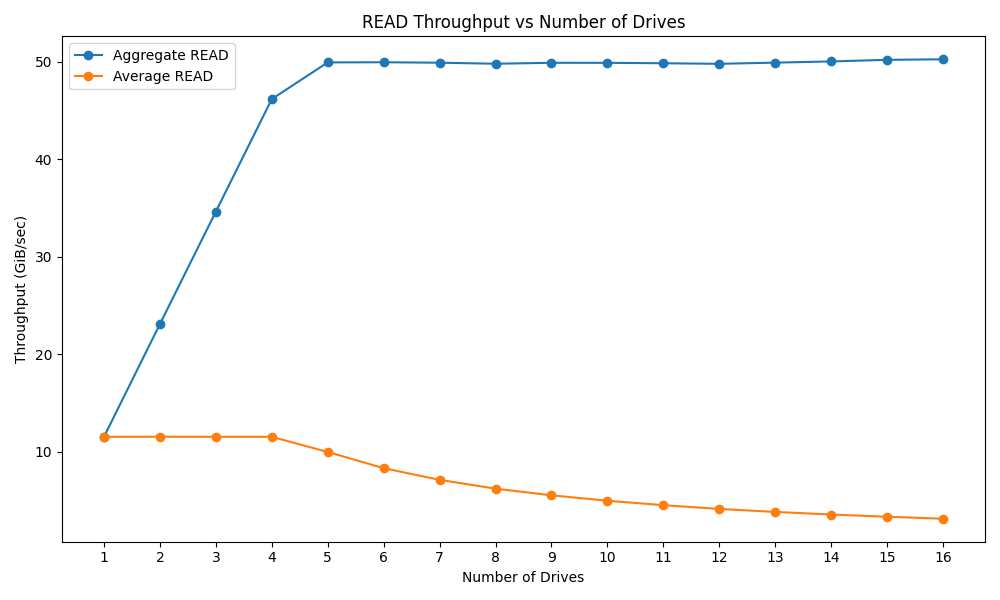

综合结果如图一所示。Vivado综合完预估的slack为8.572ns,critical path是5级,共消耗71个LUT。

图1 - leading zero count 1,分治法 - Tree Structure,现在我们使用分治法来实现这个功能。通过一个 balanced tree structure 来实现。

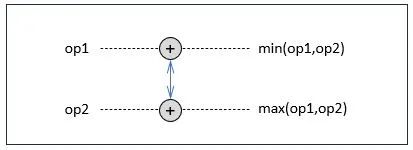

首先将 64bit 的 vector 分成32个 2bit 的小 vector。先对2bit的小 vector 做encode>

然后按照如下规则将相邻的 encoded value 进行组合>

如果两边都是 1xxx,那么结果为 10..0,如果左边是 0xxx,那么结果为 0[左边],如果左边是 1xxx,那么结果为 01[右边[msb-1:0]],可以看到每个组合的操作是一个mux。每次组合后,新的vector位宽加1,然后新的vector再两两组合,直到得出最终的结果。

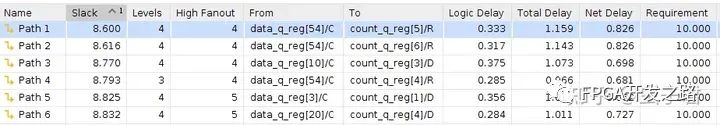

我们以8bit输入的vector为例:8'b00000111,按照2bit分解: 00 00 01 11,Encoded value: 10 10 01 00,两两组合: 100 001,再组合: 0101 = 5 leading zeros,当输入为64bit的vector时,此 tree structure 的设计综合结果如图2所示。Vivado综合后预估的slack为8.600ns,critical path为4级,消耗38个LUT。

图2 - leading zero count 2,可以看到相比于casex的设计,tree structure节省了超过50%的LUT,同时逻辑级数也减少了一级。

总结,分治法的思想也可以应用在FPGA开发中。尤其是当我们遇到大位宽数据的处理时,分治法往往可以提升设计的资源使用率和时序结果。

推荐

-

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

2025-05-01

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

2025-05-01

-

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

2025-05-01

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

一文解析电磁场与电磁波的区别

一文解析电磁场与电磁波的区别

2025-05-01

-

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

2025-04-19

-

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

2025-04-19

最近更新

-

芯驰科技与Arteris深化合作

芯驰科技与Arteris深化合作

2025-05-06

-

戴尔PowerEdge R770服务器的性能测试

戴尔PowerEdge R770服务器的性能测试

2025-05-06

-

光庭信息与芯驰科技签署战略合作协议

光庭信息与芯驰科技签署战略合作协议

2025-05-06

-

京东方发布2025年第一季度报告

京东方发布2025年第一季度报告

2025-05-06

-

中科曙光DeepAI深算智能引擎全面支持Qwen3

中科曙光DeepAI深算智能引擎全面支持Qwen3

2025-05-06

-

中微爱芯亮相第21届家电电源与智能控制技术研讨会

中微爱芯亮相第21届家电电源与智能控制技术研讨会

2025-05-06

-

中科曙光亮相第八届数字中国建设峰会

中科曙光亮相第八届数字中国建设峰会

2025-05-06

-

RDK全系赋能!点猫科技与地瓜机器人共建具身智能大中小贯通培养闭环要闻

RDK全系赋能!点猫科技与地瓜机器人共建具身智能大中小贯通培养闭环要闻

2025-05-06

-

魔视智能携手德州仪器亮相2025慕尼黑上海电子展

魔视智能携手德州仪器亮相2025慕尼黑上海电子展

2025-05-06

-

曙光存储亮相2025 IT市场年会

曙光存储亮相2025 IT市场年会

2025-05-06