一、时序逻辑,时序逻辑是Verilog HDL 设计中另一类重要应用。从电路特征上看来,其特点为任意时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关。

从电路行为上讲,不管输入如何变化,仅当时钟的沿(上升沿或下降沿)到达时,才有可能使输出发生变化。

1、在描述时序电路的always块中的reg型信号都会被综合成寄存器,这是和组合逻辑电路所不同的。

2、时序逻辑中推荐使用非阻塞赋值“<=”。

3、时序逻辑的敏感信号列表只需要加入所用的时钟触发沿即可,其余所有的输入和条件判断信号都不用加入,这是因为时序逻辑是通过时钟信号的跳变沿来控制的。

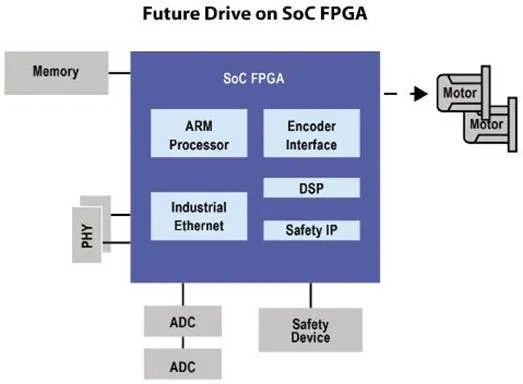

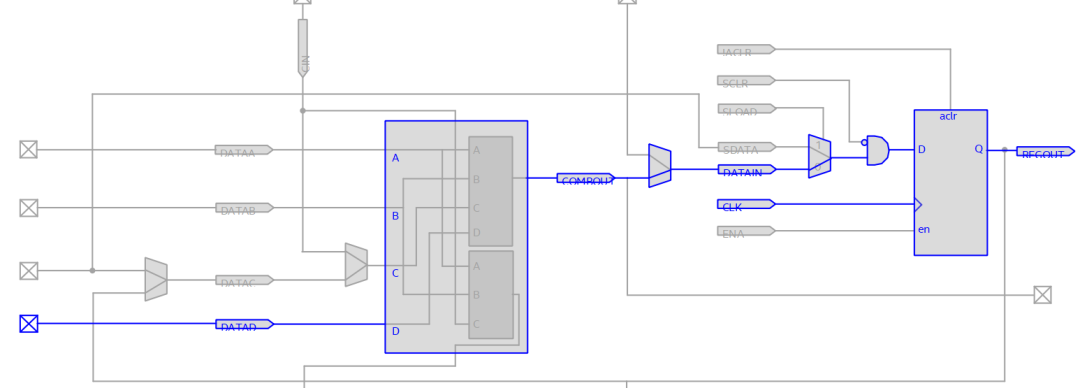

二、时序逻辑在FPGA里RTL实现,我们写一个简单的寄存器,看看fpga是怎样实现时序逻辑的,我们看一下fpga的芯片规划器,

从芯片规划器,可以看出来几个细节。

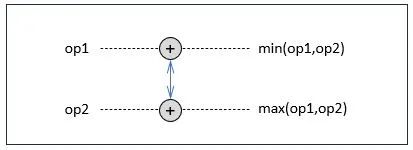

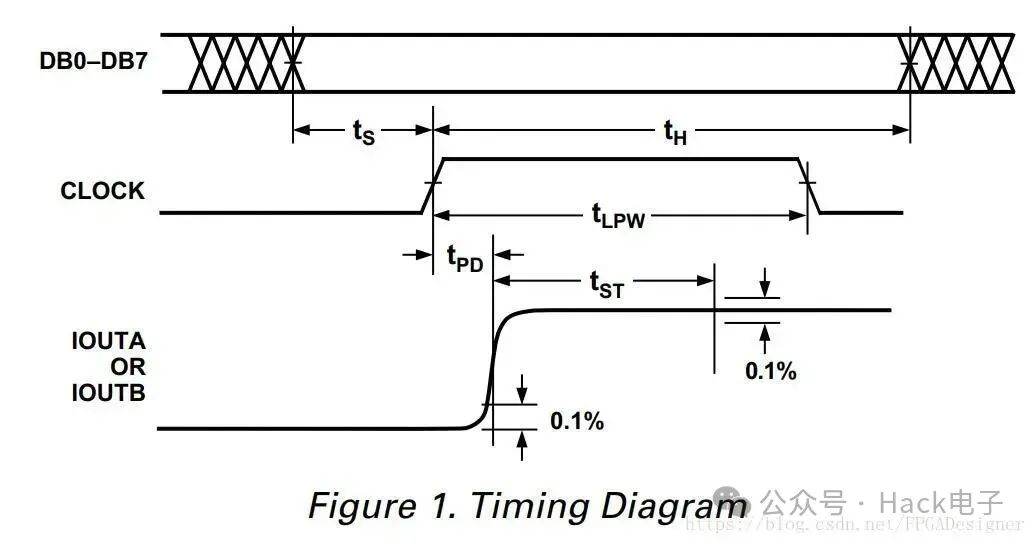

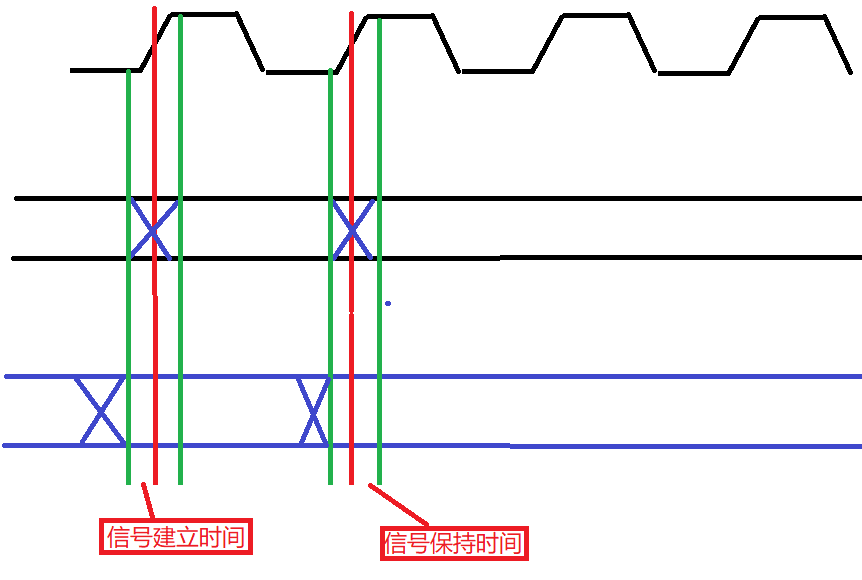

1、我们用了一个查找表、一个寄存器。对FPGA来说,这个寄存器你就算不使用他也是在那里的,2、我么的输出信号是与clk同步的,必须要等到clk的上升沿到来是,输出才会更新,因此就实现了寄存器的功能,三、同步复位、异步复位,1、同步复位:其实就是你的操作和时钟的上升沿同步,举个例子,你要将q设置为0,下面这代码就是同步复位,q <= 0,是在时钟上升沿到来时执行的,所以是同步复位,2、异步复位:其实就是你的操作和时钟没有关系,举个例子,你要将q设置为0,下面这代码就是异步复位,q <= 0,无论时钟是什么状态,只有rst_n到来就执行清零,四、竞争冒险,竞争冒险:意思是,在我时钟的上升沿进行采样时,输入信号处于不稳定状态,这个会给电路带来亚稳态的问题,

为了解决竞争冒险,我们只要满足信号的建立时间和保持时间即可,

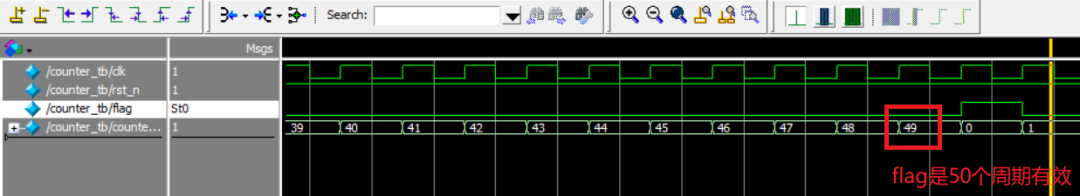

五、verilog语法补充,1、parameter 定义全局变量,2、defparam重新定义参数,这个主要是在仿真脚本修改例化的模块的内部参数,六、计数器设计,设计一个1秒的计数器,当时间到一秒后给出一个flag信号,1、代码实现 verilog.v,2、仿真脚本,我在仿真脚本将时间参数改为T改为 T=26‘d49;方便仿真,3、仿真结果,1、可以看出脉冲flag只持续了一个周期,

2、可以看出脉冲的触发是50个计数值,

七、计数器里隐藏的加法器问题,我们设计的这个计数器,里面其实用了一个加法器,加法器是组合逻辑(因为组合逻辑只取决于输入),当我们给加法器一个初值0的时候,加法器的输出立即就输出1,这就是仿真的时候,开始复位拉高后,count在第一个clk上升沿就为1的原因,

推荐

-

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

2025-05-01

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

2025-05-01

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

2025-05-01

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

一文解析电磁场与电磁波的区别

一文解析电磁场与电磁波的区别

2025-05-01

-

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

2025-04-19

-

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

2025-04-19

最近更新

-

芯驰科技与Arteris深化合作

芯驰科技与Arteris深化合作

2025-05-06

-

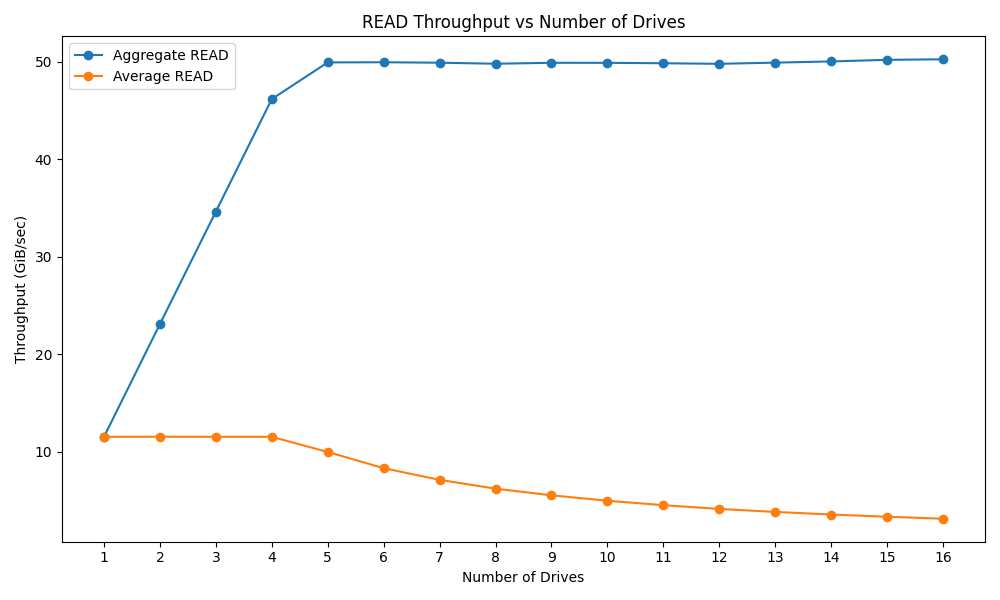

戴尔PowerEdge R770服务器的性能测试

戴尔PowerEdge R770服务器的性能测试

2025-05-06

-

光庭信息与芯驰科技签署战略合作协议

光庭信息与芯驰科技签署战略合作协议

2025-05-06

-

京东方发布2025年第一季度报告

京东方发布2025年第一季度报告

2025-05-06

-

中科曙光DeepAI深算智能引擎全面支持Qwen3

中科曙光DeepAI深算智能引擎全面支持Qwen3

2025-05-06

-

中微爱芯亮相第21届家电电源与智能控制技术研讨会

中微爱芯亮相第21届家电电源与智能控制技术研讨会

2025-05-06

-

中科曙光亮相第八届数字中国建设峰会

中科曙光亮相第八届数字中国建设峰会

2025-05-06

-

RDK全系赋能!点猫科技与地瓜机器人共建具身智能大中小贯通培养闭环要闻

RDK全系赋能!点猫科技与地瓜机器人共建具身智能大中小贯通培养闭环要闻

2025-05-06

-

魔视智能携手德州仪器亮相2025慕尼黑上海电子展

魔视智能携手德州仪器亮相2025慕尼黑上海电子展

2025-05-06

-

曙光存储亮相2025 IT市场年会

曙光存储亮相2025 IT市场年会

2025-05-06