LiteX 框架为创建 FPGA 内核/SoC、探索各种数字设计架构和创建完整的基于 FPGA 的系统提供了方便高效的基础架构。

简介,LiteX 提供了轻松创建 FPGA 内核/SoC 所需的所有常用组件>

总线(Wishbone、AXI、Avalon-ST)及其互连。

简单内核:RAM、ROM、定时器、UART、JTAG 等。

通过内核生态系统的复杂内核:LiteDRAM、LitePCIe、LiteEth、LiteSATA等......,各种 CPU 和 ISA:RISC-V、OpenRISC、LM32、Zynq、X86(通过 PCIe)等...,混合语言支持 VHDL/Verilog/(n)Migen/Spinal-HDL/etc...,通过各种桥接器和Litescope进行强大的调试基础设施。

通过Verilator直接/快速仿真。

为开源和供应商工具链构建后端。

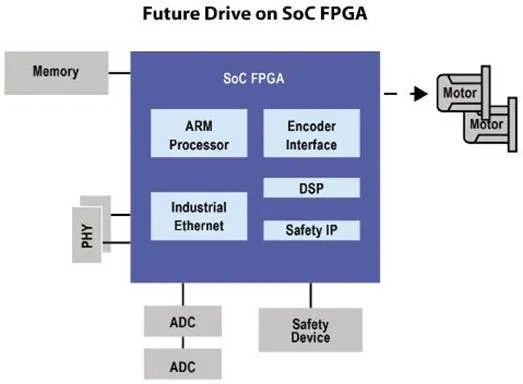

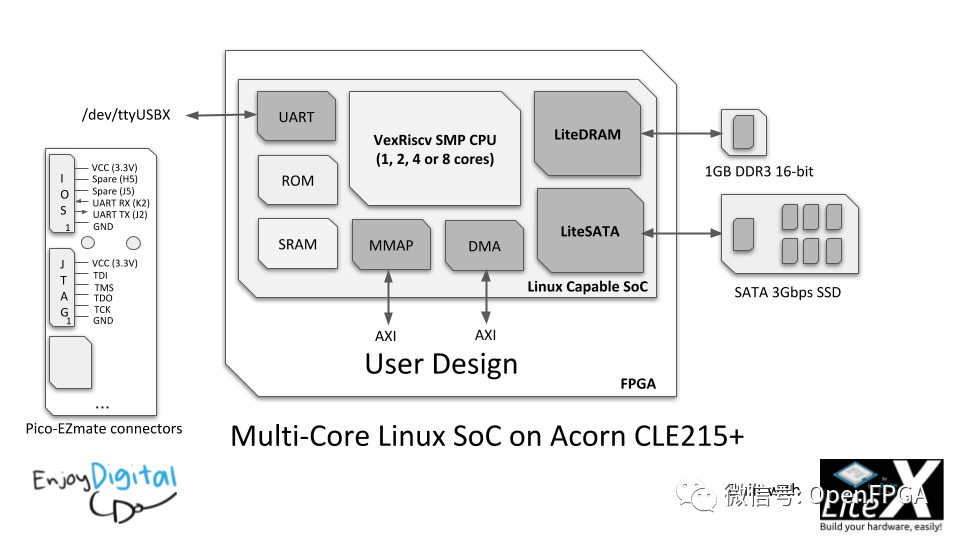

通过将 LiteX 与内核生态系统相结合,创建复杂的 SoC 变得比使用传统方法容易得多,同时提供更好的可移植性和灵活性:例如,基于 VexRiscv-SMP CPU、LiteDRAM、LiteSATA 构建的多核 Linux SoC与 LiteX 集成,在廉价的改造Acorn CLE215+ Mining Board上运行>

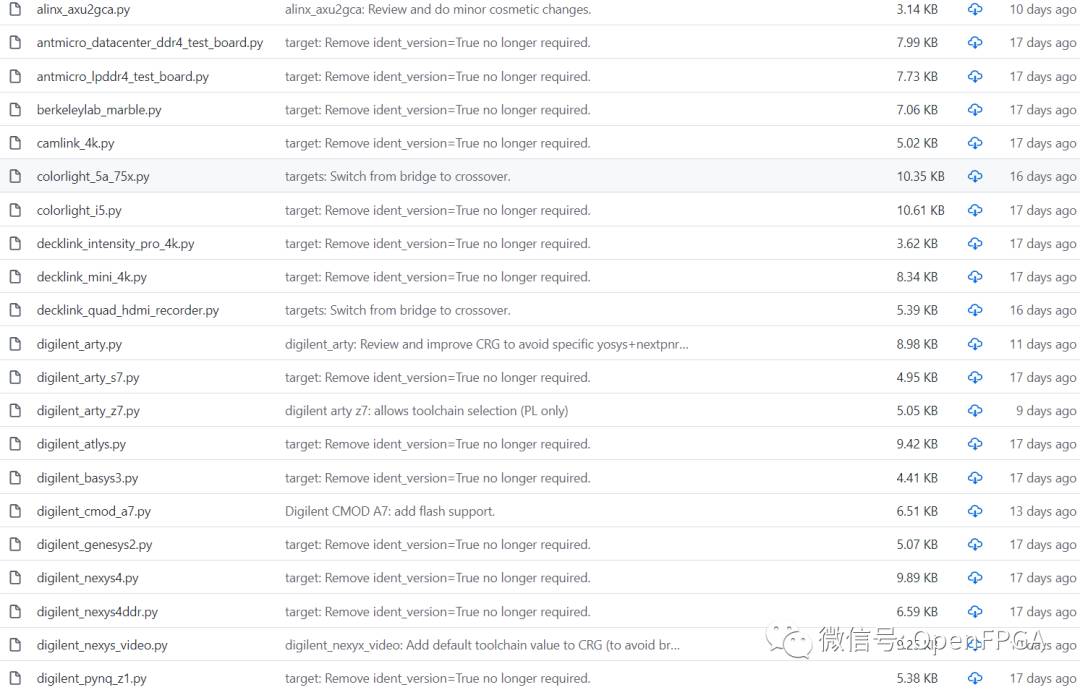

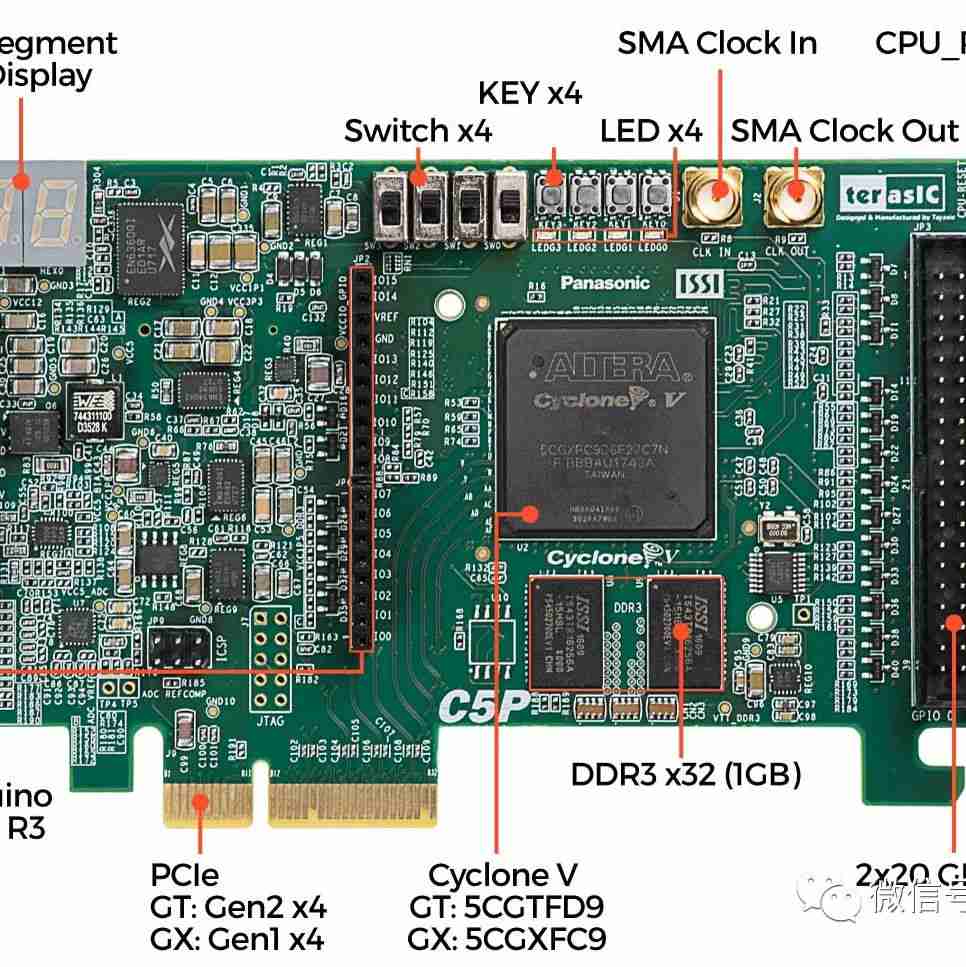

支持的硬件,❝,https://github.com/litex-hub/litex-boards/tree/master/litex_boards/targets,

典型的 LiteX 设计流程>

LiteX 已经支持各种软核 CPU:VexRiscv、Rocket、LM32、Mor1kx、PicoRV32、BlackParrot,并且与 LiteX 的核心生态系统兼容:

使用 LiteX 构建的设计示例>

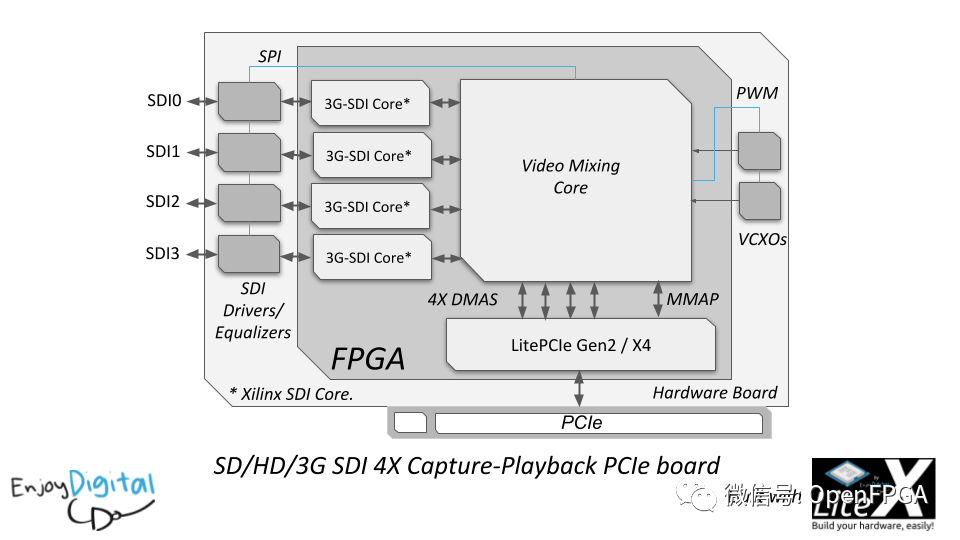

围绕 LitePCIe 构建并与 LiteX 集成的定制 PCIe SDI 采集/播放板,允许完全控制 SDI 流和极低的延迟。

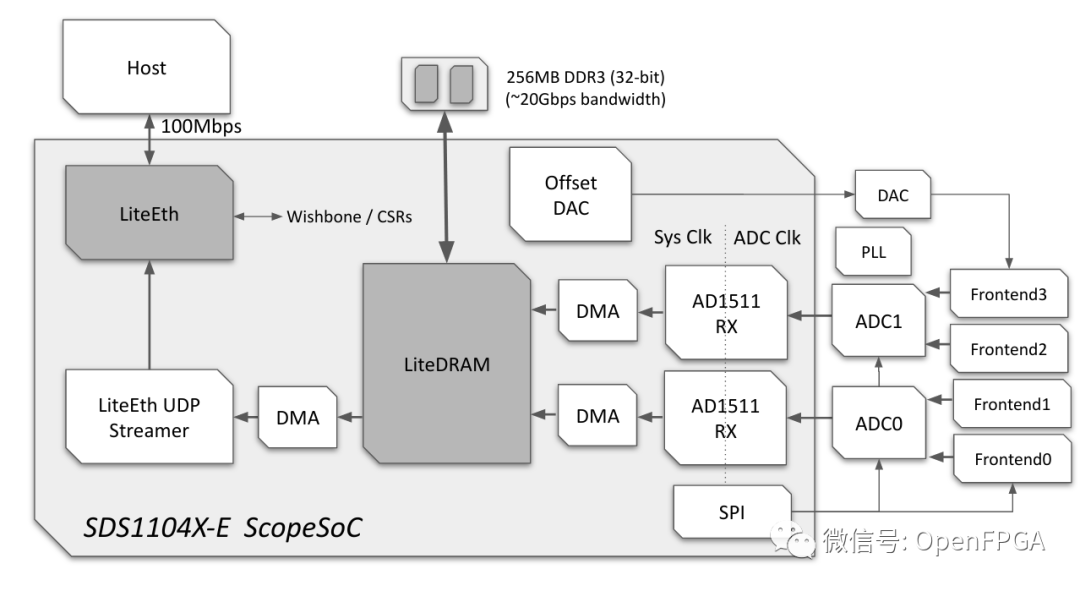

SDS1104X-E 范围的替代固件/网关>

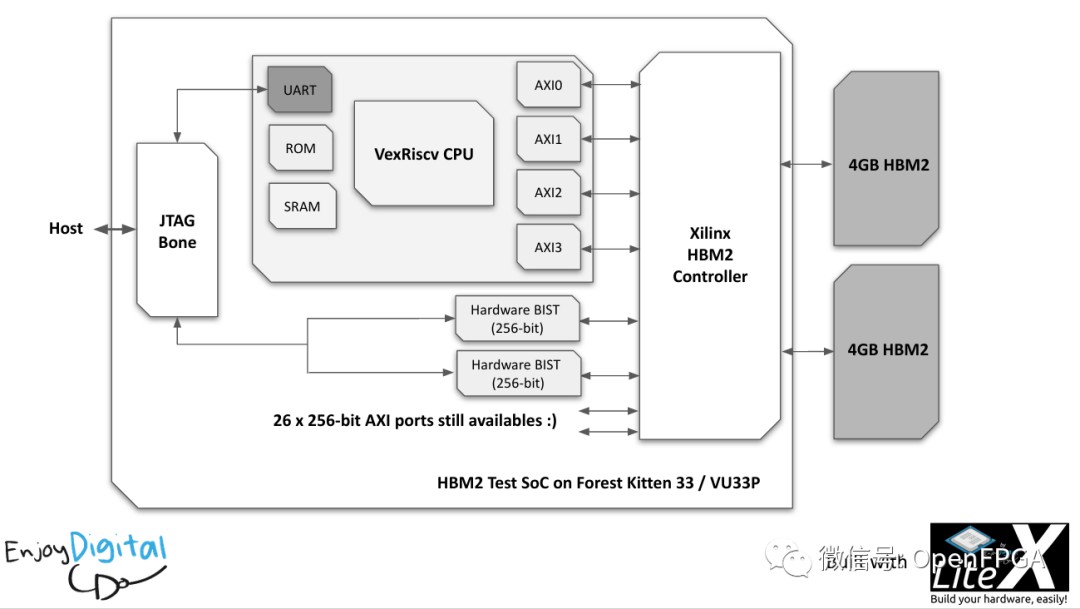

Forest Kitten 33 上的 HBM2 测试基础设施>

快速入门指南,安装 Python 3.6+ 和 FPGA 供应商的开发工具和Verilator(仿真器,可以不安装)。

安装 Migen/LiteX 和 LiteX 的核心>

需要更新所有存储库:

./litex_setup.py --update

注意:在 MacOS 上,确保您已安装HomeBrew。然后做,brew install wget。

注意:在 Windows 上,您可能必须将SHELL环境变量设置为SHELL=cmd.exe.,安装 RISC-V 工具链(仅当您想使用 CPU 测试/创建 SoC 时)>

建立目标......:

转到 litex-boards/litex_boards/targets 并执行您要构建的目标。

直接在您的计算机上安装Verilator并测试 LiteX,无需任何 FPGA 板>

在 Linux (Ubuntu) 上>

在 MacOS 上:

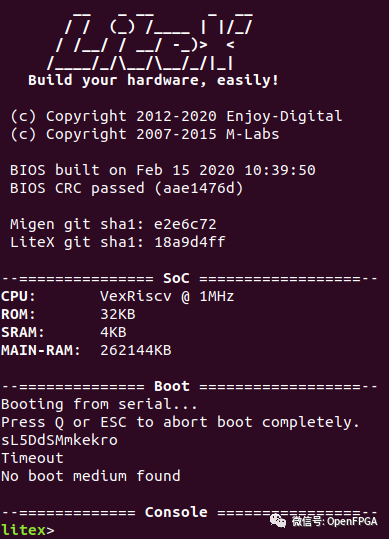

在板上的串行端口 115200 8-N-1 上运行终端程序。

应该得到如下所示的 BIOS 提示。

在FPGA上完美复刻Windows 95,

优秀的 Verilog/FPGA开源项目介绍(十七)- AXI

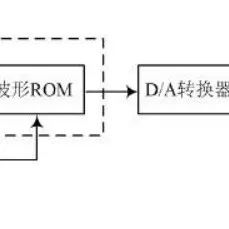

优秀的 Verilog/FPGA开源项目介绍(十六)- 数字频率合成器DDS

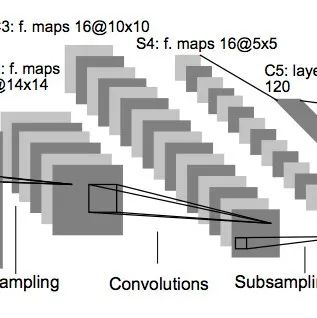

想用FPGA加速神经网络,这两个开源项目你必须要了解

推荐

-

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

2025-05-01

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

2025-05-01

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

2025-05-01

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

一文解析电磁场与电磁波的区别

一文解析电磁场与电磁波的区别

2025-05-01

-

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

2025-04-19

-

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

2025-04-19

最近更新

-

芯驰科技与Arteris深化合作

芯驰科技与Arteris深化合作

2025-05-06

-

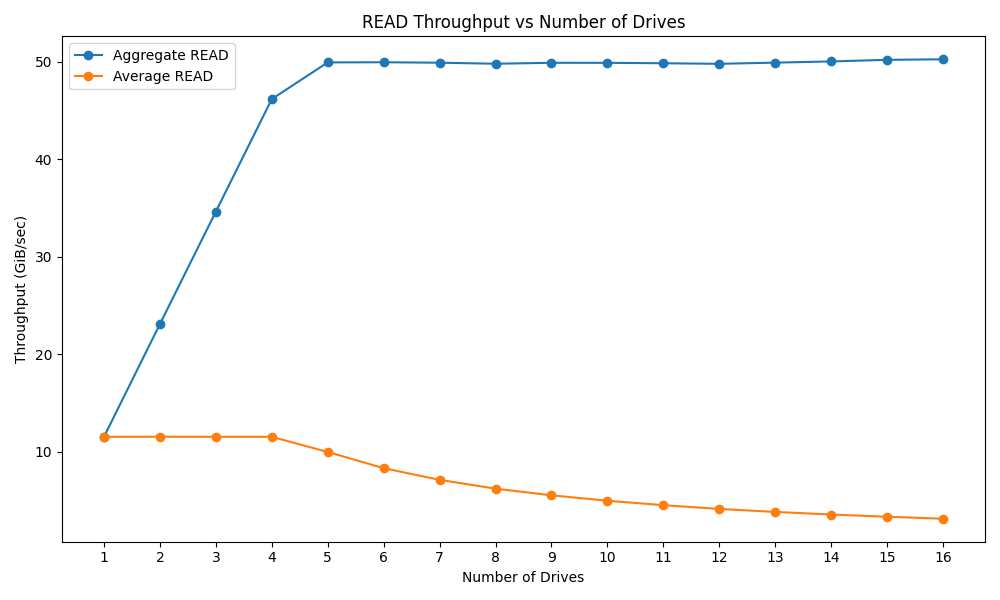

戴尔PowerEdge R770服务器的性能测试

戴尔PowerEdge R770服务器的性能测试

2025-05-06

-

光庭信息与芯驰科技签署战略合作协议

光庭信息与芯驰科技签署战略合作协议

2025-05-06

-

京东方发布2025年第一季度报告

京东方发布2025年第一季度报告

2025-05-06

-

中科曙光DeepAI深算智能引擎全面支持Qwen3

中科曙光DeepAI深算智能引擎全面支持Qwen3

2025-05-06

-

中微爱芯亮相第21届家电电源与智能控制技术研讨会

中微爱芯亮相第21届家电电源与智能控制技术研讨会

2025-05-06

-

中科曙光亮相第八届数字中国建设峰会

中科曙光亮相第八届数字中国建设峰会

2025-05-06

-

RDK全系赋能!点猫科技与地瓜机器人共建具身智能大中小贯通培养闭环要闻

RDK全系赋能!点猫科技与地瓜机器人共建具身智能大中小贯通培养闭环要闻

2025-05-06

-

魔视智能携手德州仪器亮相2025慕尼黑上海电子展

魔视智能携手德州仪器亮相2025慕尼黑上海电子展

2025-05-06

-

曙光存储亮相2025 IT市场年会

曙光存储亮相2025 IT市场年会

2025-05-06