若将英伟达的Grace CPU超级芯片的独特设计视作偶然间的耦合,那么英特尔与AMD相继推出的Falcon Shores XPU芯片及Instinct MI300芯片在功能结构上采用CPU+GPU组合配置,则无疑揭示出一种难以被单纯巧合解释的设计趋向。

恰逢其时的是,在接下来的两载里,AMD、NVIDIA以及Intel这三大科技巨头均将携手推出融合型CPU与GPU处理器,以满足数据中心领域的高端需求。

CPU与GPU相结合的架构已然成为先进芯片研发策略中的主导方向。

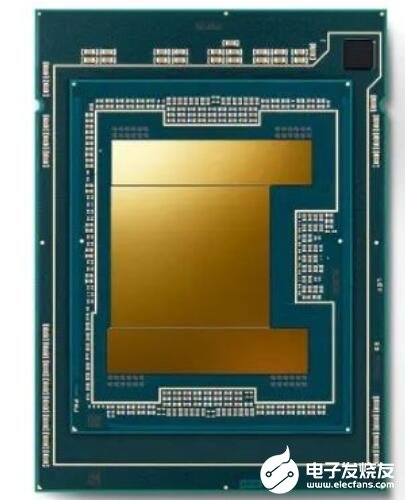

Intel has unveiled a distinctive fused processor, christened "Falcon Shores", which the company proudly labels as an XPU. This innovation features a groundbreaking microarchitecture that seamlessly integrates Intel's traditional x86 Central Processing Units alongside Xe Graphics Processing Units , all encapsulated within a unified Xeon chip, signaling a pivotal advancement in hardware convergence.

Falcon Shores微架构依托于模块化设计原则,展现出卓越的可扩展性和适应性,其精巧构建使其成为高性能计算和人工智能领域应用的理想选择。

根据Intel提供的数据,在当前基准下,Falcon Shores在能效方面实现了显著跃升,其能效比大幅度提升了超过五倍;同时,它在基于X86的计算资源集约度上也取得了卓越成就,计算密度较之先前提高了逾五倍;此外,内存容量与密度均获得了显著增强,相较于以往实现的是五倍以上的增长。

Falcon Shores的先进芯片预计于二零二四年问世,届时将引领科技领域的崭新篇章。

在数据处理与存储的专域中,AMD彰显出其雄心壮志。

自2006年Opteron CPU的全盛时期以来,AMD一直以来憧憬并致力于将APU引入市场;这一愿景在2010年得以实现,首度为个人电脑市场带来了第一款APU。后续发展涵盖了游戏机领域——索尼Play Station 4及5和微软Xbox XS均采用了定制设计的APU系列组件,并且也推出了面向服务器市场的Opteron APU,如于2013年面世的X2100型号以及在2017年问世的X3000版本。

近期,AMD披露了其发展规划,宣布计划于二零二三年问世的Instinct MI300处理器。这标志着AMD迈出了里程碑式的一步,即首次发布一款百亿亿级加速处理单元,并自豪地宣称其为“全球首个数据中心级APU”。

此APU乃一集成设计,巧妙融合了采用先进Zen4工艺的Epyc中央处理器与革新性的CDNA3图形处理器单元于单一封装之中,旨在实现更卓越的性能与能效比。

AMD宣布,预计其即将推出的Instinct MI300处理器将在人工智能训练任务中实现显著的性能飞跃,相较先前的Instinct MI250X型号,这一新款产品有望带来逾八倍的强大效能增益。相较于支撑Instinct MI200系列的CDNA2 GPU架构,专为Instinct MI300设计的CDNA3架构在处理AI工作负载时,将实现超过五倍的性能与能效比的卓越提升。

预期于二零二三年面世的Instinct MI300,将引领科技潮流。

专注于GPU领域开发的英伟达公司在去年的决策,即涉足基于Arm架构的CPU技术,曾激起了广泛的关注与热议。今年三月,英伟达再推前沿科技,引入了用于高性能计算及大规模人工智能应用的Grace Hopper超级芯片。此款先进芯片创新性地将NVIDIA Hopper系列GPU与Grace CPU通过NVLink-C2C技术整合于一个精巧集成的模块中,从而展现出其在高能效与性能优化方面的卓越能力。

CPU与GPU的Grace Hopper核心配置缩减至一半规模,而LPDDR5X内存容量精简为512GB,却额外引入了80GB的HBM3显存,其总带宽能力得以显著提升至惊人的每秒3.5TB。这一优化方案虽将系统功耗控制在了1000瓦特,并允许每个机架内部署42个节点,但同时也对资源分配和能效平衡提出了更高要求。

该配置的调整旨在通过显存性能的强化来显著提升整体数据处理效率与图形计算能力,即便在缩减了核心处理器数量与内存总容量的前提下。这一设计考量体现了在现代高性能计算领域中对于局部峰值性能和带宽需求的高度关注,同时也对系统能效管理及硬件布局提出了新的挑战。

在这样的配置下,通过巧妙地分配资源和优化工作负载,可以实现对计算密集型应用的高效支持,同时确保在高功耗限制下的稳定运行。这一设计方案不仅展示了对于先进内存技术与GPU加速能力的充分利用,也体现了在节能减排目标驱动下的创新与实践。

英伟达宣布,计划于二零二三年上半年隆重发布其卓越的超级芯片。

审视其发布时间框架,我们可以预见英特尔的Falcon Shores处理器将在二零二四年面世;而AMD的Instinct MI300和英伟达的Grace Hopper超级芯片则将提前,在二零二三年即与公众见面,其中Grace Hopper系列更将于上半年与我们相见。

CPU与GPU的融合架构,成为了科技界瞩目的焦点,吸引了行业内的三大领导者——亚马逊AWS、微软Azure和阿里巴巴云——纷纷在其数据中心中进行部署。这一趋势的根本动力在于,该形式能够提供卓越的计算性能与能效比,以满足日益增长的数据处理需求,并在人工智能、机器学习以及大规模数据分析等领域展现出无可比拟的优势。

CPU作为传统意义上处理通用任务的核心,其计算能力和效率在特定场景下可能已经接近极限。与此相对,GPU最初被设计用于图形渲染和游戏开发,但随着并行计算技术的成熟与普及,其在高并发、大规模数据并行处理方面展现出巨大潜力。

CPU+GPU架构的优势在于,通过将任务划分为多个可并行执行的部分,并由GPU高效地处理这些任务,可以显著提高计算效率。对于数据中心而言,这意味着能够在相同时间内处理更多数据或运行更复杂的算法,从而极大地提升业务处理能力和服务质量。

三大巨头选择布局这一形式于数据中心的原因还涉及对未来的前瞻性和市场竞争力的追求。随着人工智能、大数据分析、云计算服务等领域的需求持续增长,能够提供强大计算能力与能效比的产品和解决方案成为了竞争的关键所在。通过整合CPU+GPU架构,这些公司能够在数据处理速度、资源利用率以及整体性能上保持领先地位,从而吸引更多的用户和企业客户,增强其在市场中的竞争优势。

因此,无论是从技术发展的必然趋势、业务需求的迫切性,还是对于未来竞争力的高度关注,三大巨头都将CPU+GPU布局视为数据中心战略的重要一环。这一举措不仅体现了科技领域的前沿探索与实践,也预示着云计算、AI等应用在未来将持续迎来更为强大的动力支撑和更高效的服务体验。

在数字经济的浪潮之中,算力日益成为驱动社会生产和生活进步的新引擎,全面渗透并整合至各个领域的运作之中。数据中心作为算力实现物理形态的基础平台,扮演着推动数字化转型的关键角色与核心基础设施。全球范围内,数据中心建设持续稳定增长,截至2021年,其市场规模已显著突破679亿美元大关,相较于前一年实现了9.8%的增长幅度。因此,这一庞大且极具潜力的市场领域,早已成为了科技界领头羊们的密切关注焦点。

数据中心在运行过程中生成的庞大数据量,使得构建于其上的芯片需具备卓越的计算能力。为此,英特尔高级副总裁兼加速计算系统与图形集团总经理Raja Koduri强调,在进军HPC市场时,关键在于所用芯片应能够高效处理海量数据集的能力。

值得一提的是,GPU因其强大的并行处理性能而备受青睐——它能同时激活众多内核以实现高速运算。然而,当前独立GPU仍面临一个显著的局限:在处理大型数据集时,这些集合难以简便地装载进其内存之中,进而导致需要花费时间等待显存中的数据进行缓慢刷新。

因此,在大数据时代下,实现高效的数据处理与管理成为推动计算技术发展的关键挑战之一。

为了优化架构并解决冗余问题,采取了整合策略,即将中央处理器与图形处理单元置于同一架构内运作。这样做能显著减少内存副本来提升效率。不再需要额外的内存副本供CPU单独使用,因为数据可以直接在共享的封装中流通,无需复制至专用内存池。

例如,在Instinct MI300这款创新处理器中,通过将CDNA3 GPU的小芯片与采用Zen4架构的CPU小芯片整合进一个封装内,并共用HBM内存。这样的设计不仅消除了对第二个独立DRAM内存芯片的需求,还确保了数据在CPU和GPU之间流畅交换,增强了系统性能的同时,也显著提高了能源效率。

英伟达官方声明指出,通过采用NVLink-C2C互连技术,Grace中央处理器在向Hopper图形处理单元传输数据时的速度较传统CPU快出惊人的十五倍之多;然而,在面对大规模数据集的场景中,即便借助了NVLink、AMD Infinity Fabric这类高速接口,因HPC级处理器处理海量数据的速度极快,导致CPU与GPU间交换信息的延迟及带宽损耗依然不容小觑。为此,缩短该连接物理距离的做法,有望显著提升能效并优化性能表现。

AMD声称,相较于采用独立中央处理器和图形处理单元的配置方案,其所设计的体系结构能实现更为高效的能耗使用,以更低的能量成本达到性能目标。而英特尔也指出,其Falcon Shores系列芯片将大幅度优化带宽、提升每瓦特性能、增强计算集约度,并增加内存容量,从而显著改善整体系统效能。

集成多种独立模块通常能带来一系列长远的利益,并非仅限于将中央处理器和图形处理器单纯地合并在单一芯片之上。在这方面,业界领导者如英特尔、英伟达以及AMD所采用的模组级封装策略,揭示了整合多样组件的智慧与前瞻性。这种策略不仅实现了硬件资源的优化配置,还为系统性能的提升开辟了新途径,进一步推动了计算领域的创新与发展。

在过去,为打造功能丰富的集成电路解决方案,各供应商致力于将多种功能整合至单一微芯片之上。随时间推移,每一版芯片所承载的功能密度显著提升,在最近的7纳米与5纳米制造节点中,相关的开发成本及技术复杂度达到了前所未有的高峰。

采用Chiplet设计策略,能够灵活地集成具有特定功能与工艺节点的微小芯片模块,客户得以挑选并整合这些独立的小芯片组件,以构建出高度定制化的先进封装解决方案。这种方法革新了传统的系统级芯片设计理念,提供了一种更加优化、适应性更强且可扩展的路径。

得益于小型芯片的独特属性,三家公司不仅各自致力于推进多元化的芯片互联技术发展,而且还推出了个性化的定制服务。

当英特尔在公布Falcon Shores之时,阐述了他们将采用Chiplet设计策略,这一创新方法允许通过集成源自不同制造工艺和具有多元功能的处理器模块,紧凑地构建于单一芯片封装内。此举赋予了英特尔前所未有的灵活性与能力,得以对芯片内部的构成进行深度定制,包括但不限于CPU、GPU、I/O接口、内存类型以及电源管理机制等关键部件,以及其他复杂电路技术。这一策略不仅提升了系统的集成度和能效,还拓展了工艺兼容性和设计优化的可能性。

在Falcon Shores中,我们提供了一种高度定制化的解决方案,允许用户按照特定需求构建不同的区块组件。这包括对x86 CPU内核与Xe GPU核心的数量以及其配比进行自由调整,以确保无论您的项目侧重于何种功能或应用,都能得到恰如其分的支持和优化。

当下,英特尔已经放宽了对x86架构的授权限制,并实施了Chiplet战略,此举措旨在赋能客户灵活整合Arm与RISC-V核心于单一封装之中,从而推动计算生态系统的多样化与协同创新。

近期,在分析师会议中,AMD首席技术官马克·帕帕默斯宣布了公司致力于简化和提升定制化芯片的可获取性和灵活性的战略目标。

AMD现为客户提供了一种创新解决方案,在紧凑型集成电路封装内整合多颗芯粒,这些芯粒可被视为独立的计算模块。该公司的现有实践已基于此理念,而今更进一步开放平台,允准第三方开发的加速器或其他半导体元件与AMD的传统x86中央处理器及图形处理单元协同工作,无论在二维平面还是三维空间中。此举旨在整合多样化计算资源,以满足广泛的应用需求和性能目标。

AMD的战略蓝图以革新性的Infinity Architecture 4.0为核心,该架构致力于优化芯片封装内裸片间的互联机制。其独特的设计与CXL 2.0互连标准无缝兼容,从而引领了计算领域中的先进集成与协同处理技术的前沿。

Infinity网络架构将全面兼容并支持UCIe,这一先进的标准旨在实现封装内芯片单元的整合与互连。UCIe技术已汇聚了包括英特尔、超微、Arm公司、以及科技巨头谷歌和Meta在内的行业领军人物的支持,共同推进其在集成电路领域的应用与扩展。

根据市场研究机构Counterpoint Research的研究专家Akshara Bassi的观点,当面临日益增大的芯片尺寸及晶圆产出效率挑战时,多芯片组件整合方案在能耗与性能方面展现出超越单一芯片架构的卓越优势。

尽管chiplet技术前景广阔,当前其发展却仿佛置身于独立岛屿之上。在这个领域内,包括AMD、Apple、Intel与NVIDIA在内的先驱企业,正聚焦于开发自主设计的互联策略,并将其融入定制化的封装体系之中。

在2018年,英特尔对其EMIB技术进行了革新与升级,使之演变为一种高度先进的逻辑晶圆三维堆叠技术。翌年,即2019年,该科技巨头进一步推出了创新的Co-EMIB解决方案,此一革命性技术能够实现两个乃至更多Foveros芯片间的紧密互联。

AMD在2019年前瞻性地引领了Chiplet模式的发展,并全面采用小型化芯片技术,从而获得了显著的技术领先。Lisa Su在其演讲中阐述了长远的战略规划:与台积电紧密合作,旨在将小芯片封装和芯片堆叠技术融为一体,共同打造面向未来高性能计算领域的3D Chiplet架构。

于今年三月初,英特尔、AMD、Arm、高通、台积电、三星、日月光、谷歌云、Meta与微软这十家行业领头羊共同组建了Chiplet标准联盟,并联合推出了统一小芯片互连规范,旨在集全球之力加速整合与推进这一技术领域的发展。

迄今为止,仅有一小部分领先的半导体企业成功研发并生产了采用chiplet架构的处理器。鉴于制造更高集成度芯片所需成本的持续攀升,在当前环境下,业界对chiplet技术的需求比以往任何时候都更为迫切。随着多芯片方案的普及趋势日益凸显,未来顶级芯片设计无疑将倾向于采取多芯片整合策略。