在这篇文章中,小编将为大家带来FPGA电源排序方案的相关报道。如果你对本文即将要讲解的内容存在一定兴趣,不妨继续往下阅读哦。

一、FPGA设计

FPGA设计不是简单的芯片研究,主要是利用 FPGA 的模式进行其他行业产品的设计。与 ASIC 不同,FPGA在通信行业的应用比较广泛。通过对全球FPGA产品市场以及相关供应商的分析,结合当前我国的实际情况以及国内领先的FPGA产品可以发现相关技术在未来的发展方向,对我国科技水平的全面提高具有非常重要的推动作用。

与传统模式的芯片设计进行对比,FPGA 芯片并非单纯局限于研究以及设计芯片,而是针对较多领域产品都能借助特定芯片模型予以优化设计。从芯片器件的角度讲,FPGA 本身构成了半定制电路中的典型集成电路,其中含有数字管理模块、内嵌式单元、输出单元以及输入单元等。在此基础上,关于FPGA芯片有必要全面着眼于综合性的芯片优化设计,通过改进当前的芯片设计来增设全新的芯片功能,据此实现了芯片整体构造的简化与性能提升。

当采用现场可编程门阵列 (FPGA) 进行设计时,电源排序是需要考虑的一个重要的方面。

二、技术设计中,可采用的2种FPGA电源排序方案

下面,本文介绍两种在技术设计过程中,可以采用的两种解决方案。

方法一:把PGOOD 引脚级联至使能引脚

实现排序的一种基本的成本效益型方法是把一个电源的电源良好 (PG) 引脚级联至相继的下一个电源的使能(EN) 引脚。

第二个电源在 PG 门限得到满足(通常是在电源达到其终值的90% 之时)时开始接通。这种方法的优势是成本低,但是无法轻松地控制定时。在EN 引脚上增设一个电容器会在电路级之间引入定时延迟。然而,此方法在温度变化和反复电源循环期间是不可靠的。而且,这种方法并不支持断电排序。

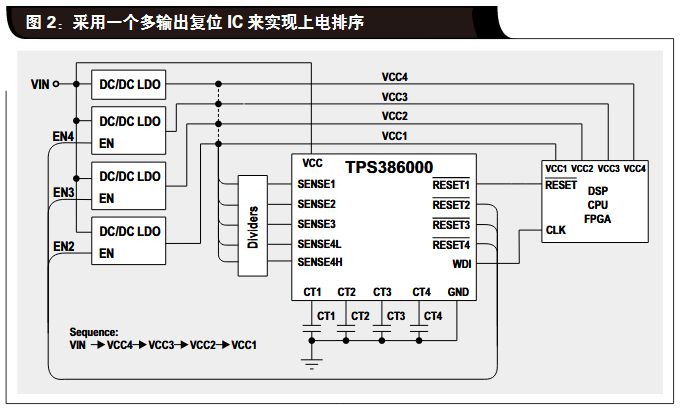

方法二:采用一个复位 IC 来实现排序

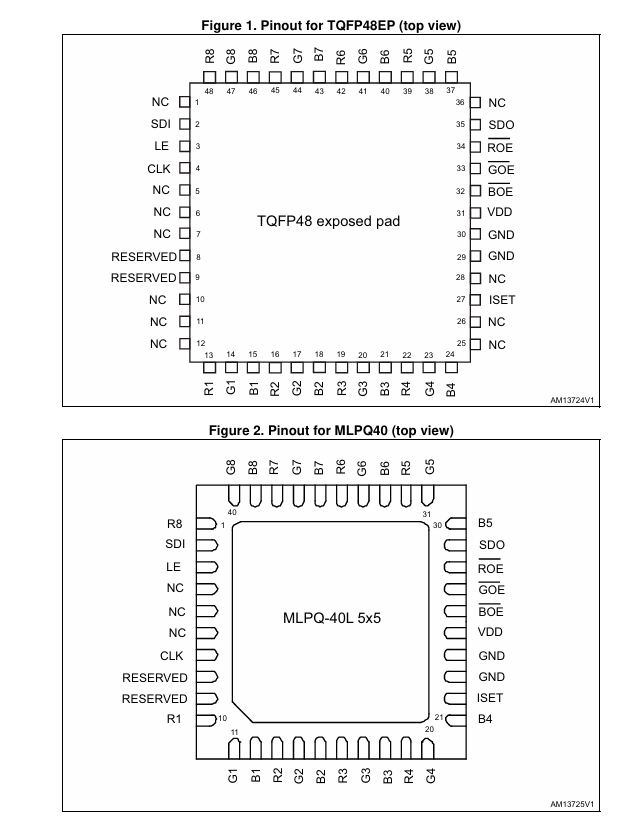

另一种可以考虑的用于上电排序的简单选项是采用一个具有时间延迟的复位 IC。当采用此选项时,复位 IC 以严格的门限限值来监视电源轨。一旦电源轨处于其终值的3%(或更小)以内,复位 IC 将进入由解决方案定义的等待周期,然后再执行下一个电源轨的上电操作。该等待周期可以采用 EEPROM 编程到复位 IC 中,也可利用外部电容器来设定。图 2 示出了一款典型的多通道复位IC。采用复位 IC 来实现上电排序的优点是解决方案处于受监视的状态。

以上便是小编此次带来的全部内容,十分感谢大家的耐心阅读,想要了解更多相关内容,或者更多精彩内容,请一定关注我们网站哦。