在这篇文章中,小编将对奇数分频器的技术设计和代码实现加以介绍以帮助大家增进对它的了解程度,和小编一起来阅读以下内容吧。

一、奇数分频器技术设计 & 代码实现

1、设计方法

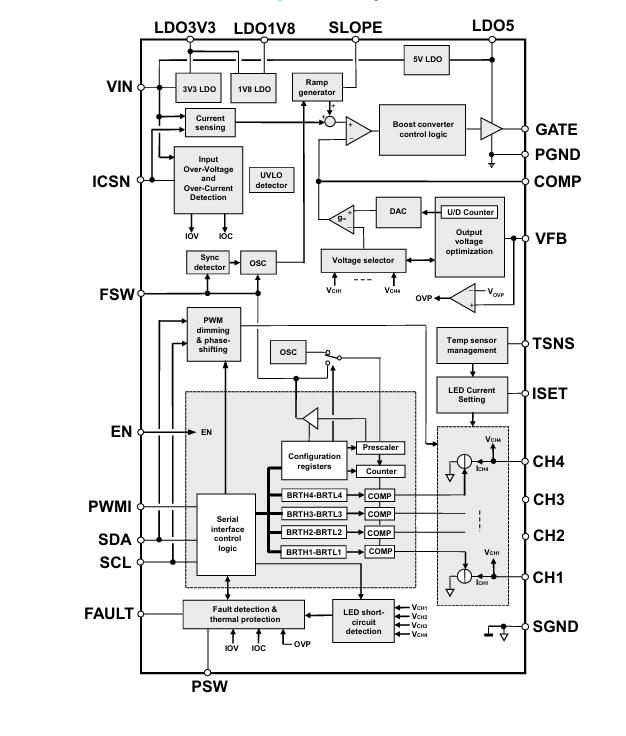

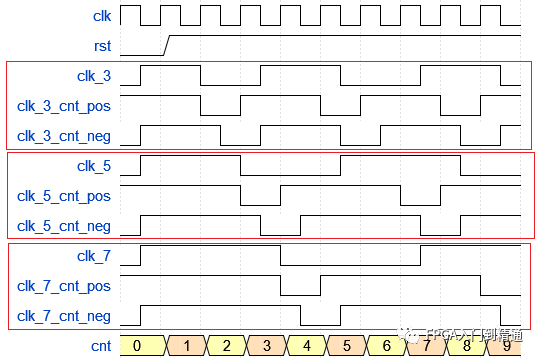

3分频时钟设计,只需要在上升沿时循环计数0~2,上升沿计数时钟信号和下降沿计数时钟信号,都是前1个周期为低电平,后2个周期为高电平;

5分频时钟设计,只需要在上升沿时循环计数0~4,上升沿计数时钟信号和下降沿计数时钟信号,都是前2个周期为低电平,后3个周期为高电平;

7分频时钟设计,只需要在上升沿时循环计数0~6,上升沿计数时钟信号和下降沿计数时钟信号,都是前3个周期为低电平,后4个周期为高电平;

下图分别画出了基准时钟、3分频时钟、5分频时钟、7分频时钟。

由此可以推导出,奇数分频设计的方法:设为2N+1分频,只需设计一个计数器在上升沿时循环计数0~2N,上升沿计数时钟信号和下降沿计数时钟信号,都是前N个周期为低电平,后N+1个周期为高电平;

2、verilog代码实现

任意偶数分频设计,可通过设置参数NUM,设定分频数,具体代码如下所示:

module clk_divider_odd#(parameter NUM = 7)(input clk,input rst,output wire clk_o);//参数定义

localparam WIDTH = $clog2(NUM);

localparam CNT_END = NUM - 1;

localparam CNT_END0 = NUM/2 - 1;

reg [WIDTH-1:0] cnt;

reg clk_pos, clk_neg;//计数模块

always@(posedge clk or posedge rst)

beginif(rst)cnt <= 'b0;

else if(cnt == CNT_END) //计满则清零

cnt <= 'b0;elsecnt <= cnt + 1'b1;

end//分频时钟输出模块,时钟上升沿

always@(posedge clk or posedge rst)

beginif(rst)clk_pos <= 1'b0;

else if(cnt == CNT_END0)clk_pos <= 1'b1;

else if(cnt == CNT_END )clk_pos <= 1'b0;

elseclk_pos <= clk_pos;

end//分频时钟输出模块,时钟下降沿

always@(negedge clk or posedge rst)

beginif(rst)clk_neg <= 1'b0;

else if(cnt == CNT_END0)clk_neg <= 1'b1;

else if(cnt == CNT_END)clk_neg <= 1'b0;

elseclk_neg <= clk_neg;

end//输出时钟

assign clk_o = clk_pos && clk_neg;

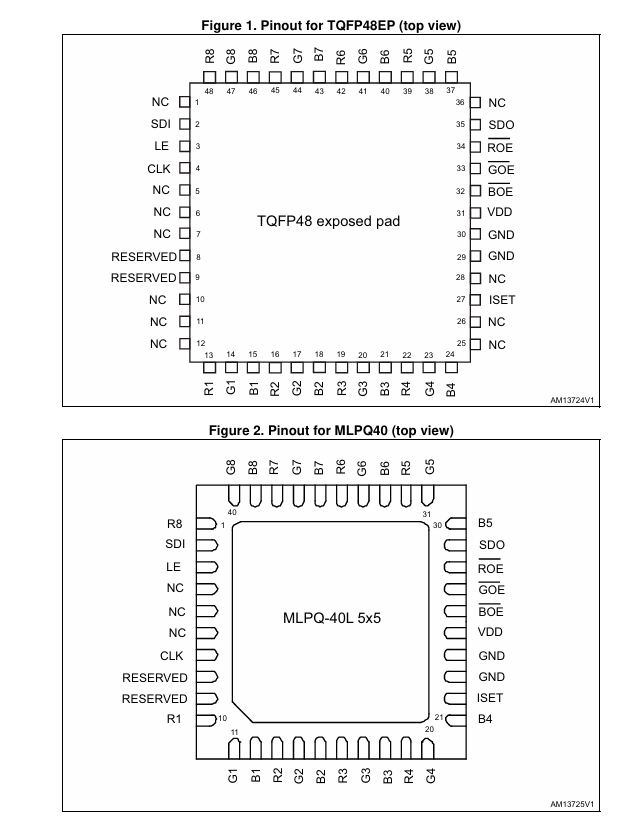

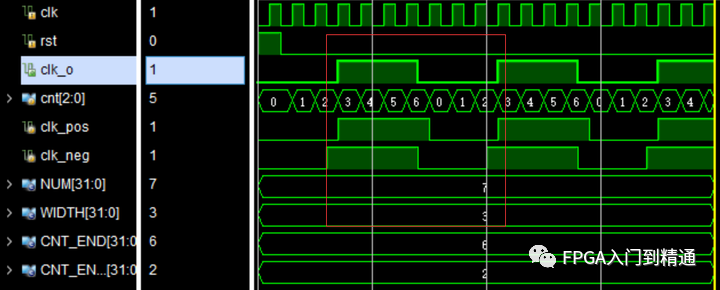

endmodule仿真结果如下图:

从图中看出,输出了7分频时钟信号,与预期一致。

二、分频器技术参数

一般来说,分频器包括三个基本参数。

第一个,就是分频器的分频点,这个应该不用多说。

第二个,就是所谓分频器的“路”,也就是分频器可以将输入的原始信号分成几个不同频段的信号,我们通常说的二分频、三分频,就是分频器的“路”。

第三个,就是分频器的“阶”,也称“类”。

一个无源分频器,本质上就是几个高通和低通滤波电路的复合体,而这些滤波电路的数量,就是上面所说的“路”。但是在每一个滤波电路中,还有更精细的设计,换句话说,在每一个滤波电路中,都可以分别经过多次滤波,这个滤波的次数,就是分频器的“阶”。

一阶分频器也是感容分频的结构,而二阶分频器中的每一路都经过了两次滤波,这个“两次滤波”才是“二阶”的真正含义!

以上便是小编此次想要和大家共同分享的有关奇数分频器的技术设计和代码实现的内容,如果你对本文内容感到满意,不妨持续关注我们网站哟。最后,十分感谢大家的阅读,have a nice day!