概要:文章探讨FPGA及数字电路设计中异步FIFO深度计算的重要性,包括其原理、方法及代码实现示例。FIFO深度需考虑时钟频率、数据位宽、速率差异等因素,确保数据跨时钟域传输时不溢出或丢失。介绍了基于读写指针、时钟频率及时序参数、读写速率等计算方法,并给出Verilog代码示例,为FPGA开发者提供参考。

在FPGA与数字电路设计的璀璨星空中,FIFO犹如一颗耀眼的星辰,以其独特的魅力,在数据传输的舞台上扮演着不可或缺的角色。特别是在跨时钟域数据传输的广阔天地里,异步FIFO更是如同一位英勇的领航者,引领着数据在时域之间顺畅穿梭。

当我们提及异步FIFO的深度计算时,这不仅仅是一个简单的数字问题,它关乎着FIFO能够容纳多少数据、承载着多少信息。深度计算的准确性,直接关系到数据传输的效率与稳定性。本文将带您走进异步FIFO深度计算的神秘世界,深入剖析其原理与方法,同时为您提供实用的代码实现示例,助您在设计的道路上更进一步。

让我们一同踏上这场充满挑战与发现的旅程,探寻异步FIFO深度计算的奥秘,为数字电路设计的辉煌未来添砖加瓦!

深入解析:异步FIFO的深度计算之道

在数字系统设计的深邃海洋中,异步FIFO扮演着至关重要的角色。其深度计算,更是确保数据流畅传输、系统稳定运行的基石。接下来,让我们一同探寻这背后的原理与奥秘。

异步FIFO,顾名思义,其“异步”特性意味着其读写操作可以在不同的时钟域下独立进行。这种特性使得它在跨时钟域数据传输中显得尤为关键。而“FIFO”即先入先出,保证了数据的顺序性和完整性。

然而,要确保异步FIFO能够高效、稳定地工作,深度的计算至关重要。它关乎着FIFO的存储能力,以及能否在繁忙的数据流中保持不溢出、不欠载的状态。

深度计算的核心在于对系统数据流特性的深入理解。我们需要分析数据的产生速率、消耗速率,以及可能出现的最大延迟。基于这些参数,我们可以计算出FIFO所需的最小深度,以确保在任何情况下都能满足数据传输的需求。

不仅如此,深度计算还需要考虑系统的冗余性和容错性。适当的增加FIFO深度,可以在一定程度上提升系统的鲁棒性,减少因偶发因素导致的数据丢失或传输错误。

总之,异步FIFO的深度计算是一项细致而严谨的工作。它要求我们不仅要深入理解系统的数据流特性,还要综合考虑系统的稳定性和冗余性。只有这样,我们才能设计出高效、稳定的异步FIFO,为数字系统的稳定运行提供坚实的保障。

异步FIFO的深度,象征着其强大而灵活的数据缓存能力。这一指标,以“字”或“位”为基准,直接反映了FIFO能够容纳的数据量。当我们深入探讨其计算依据时,不禁要考虑到众多核心因素:比如读写时钟的精准频率,数据位宽的巧妙设计,以及数据写入与读取之间可能存在的微妙速率差异。这些因素共同交织,构成了异步FIFO深度计算的复杂而精彩的画卷。

在数字系统的交错旋律中,异步FIFO扮演着举足轻重的角色。想象一下,它的读写操作如同两位技艺高超的舞者,各自在不同的时间舞台上翩翩起舞——这便是不同的时钟域。而这两位舞者的步伐节奏,即时钟频率,有时却不尽相同。

当写时钟频率如疾风骤雨般快速,而读时钟频率则如和风细雨般轻柔,异步FIFO便成了它们之间的桥梁。它深知,为了维持数据的和谐与完整,必须拥有足够的深度来容纳那些因写时钟节奏过快而暂时无法被读取的数据。这片广阔的缓存空间,就像一座巍峨的城堡,守护着数据的安宁,防止它们因无法及时被接纳而溢出流失。

异步FIFO的每一次读写,都仿佛是一次精心编排的舞蹈,确保在时钟频率差异的考验下,数据依然能够准确无误地流淌,为整个数字系统注入活力与生命力。

数据的宽度,决定FIFO的无限可能

想象一下,FIFO就像是一个高效的传送带,承载着数据在数字世界中穿梭。而这条传送带的“宽度”——也就是数据位宽,决定了它每次能够承载的数据量。这不仅仅是一个简单的数字,它更是FIFO性能与效率的关键所在。

每当数据通过这条“传送带”时,其位宽都决定了每个存储单元的大小。这就好比一辆卡车与一辆小轿车,虽然它们都能运输物品,但卡车的载货量显然更为庞大。因此,FIFO的数据位宽越大,其存储单元所能容纳的数据量就越大,进而使得FIFO的总容量也随之提升。

当我们谈论FIFO的深度时,实际上是在谈论这条“传送带”上能够承载多少个这样的存储单元。而为了更准确地计算这一数值,我们需要根据数据位宽,将总容量巧妙地转换为数据单元的数量。这不仅仅是一个数学游戏,更是对FIFO性能与效率的深入挖掘。

在这个数字时代,FIFO作为数据存储与传输的重要工具,其数据位宽的重要性不言而喻。它不仅仅决定了存储单元的容量,更决定了FIFO的整体性能。因此,在选择和使用FIFO时,请务必关注其数据位宽,让它为您的数据世界带来无限可能。

揭秘数据速率之舞:写入与读取的速度差异

在数字世界的舞台上,数据速率扮演着至关重要的角色。它们不仅仅是简单的数字,更是决定信息流动速度的舞者。而当谈及数据写入与读取的速率时,一场精彩的舞蹈即将上演。

首先,让我们聚焦于时钟频率这位舞台的指挥家。虽然它的节奏为整个数据流提供了基准,但真正的主角却是写入与读取的速率。想象一下,当它们和谐共舞时,数据就像流水般顺畅地流淌;然而,当它们的步伐出现差异时,就需要一个特殊的舞者——FIFO,来巧妙地调整节奏,确保数据的流畅性。

在某些应用中,写入速率如同一位活力四溢的舞者,其步伐轻盈而迅速,远远超过了相对沉稳的读取速率舞者。这时,FIFO便展现出了其独特的魅力。它如同一个宽敞的舞台,拥有足够的深度来缓存那些等待上场的数据舞者,确保它们不会因为节奏的不匹配而掉队。

因此,当我们谈论数据速率差异时,不妨将其视为一场精彩的舞蹈。而FIFO,则是这场舞蹈中不可或缺的舞者,用它的深度与智慧,确保数据流的和谐与顺畅。

深入解析:异步FIFO的深度计算艺术

在数字电路设计的海洋中,异步FIFO的深度计算如同一门精致的艺术,需要精心策划和细致执行。异步FIFO,作为数据缓冲的关键组件,其深度计算不仅关乎电路的性能,更影响着整体系统的稳定性和效率。

当数据流在不同时钟域间穿梭时,异步FIFO如同一位优雅的舞者,在时钟的节拍中轻盈地传递着数据。而为了确保舞者能够优雅地舞动,我们需要精确地计算出FIFO的深度,以应对各种可能的数据流量。

深度计算的过程,就像是在为舞者绘制一个完美的舞台。我们需要考虑数据的产生速率、消耗速率,以及可能出现的突发流量。只有经过精心计算,我们才能确保FIFO的深度既能满足数据缓冲的需求,又不会造成资源的浪费。

因此,异步FIFO的深度计算不仅仅是一个技术问题,更是一个需要深思熟虑和精心策划的艺术过程。通过它,我们可以为数字电路系统打造一个稳定、高效的数据传输通道,让数据在时钟的节拍中自由穿梭,为整个系统带来更加出色的性能表现。

在数字电路设计的海洋中,异步FIFO深度的计算宛如一座灯塔,为我们指引着前进的方向。它的重要性不言而喻,因为它直接关系着数据缓冲的效率和稳定性。那么,要如何精准而有效地计算这一关键参数呢?

一般来说,异步FIFO深度的计算主要依赖于以下几种方法:

无需多言,每一种计算方法都有其独特的优势和适用场景。深入理解和掌握这些计算方法,将有助于我们更好地设计和优化数字电路系统,实现更高效、更稳定的数据传输与处理。

跃然纸上的智慧——探索读写指针的奥秘

在信息的海洋中遨游,我们离不开一种神奇的工具——读写指针。它如同航海家的指南针,引领我们在数据的海洋里精准定位,高效前行。

当我们谈论读写指针时,我们谈论的不仅仅是简单的数据存储和检索,更是对信息深度和广度的探索。想象一下,当你想从海量的数据中快速找到某个关键信息,是读写指针在背后默默助力,帮你实现这一目标。

在编程的世界里,读写指针扮演着至关重要的角色。它像是一位精明的向导,让你能够轻松地在数据的海洋中穿梭,无论是读取还是写入,都能得心应手。

探索读写指针的奥秘,就如同打开了一扇通往智慧世界的大门。让我们一起跟随它的脚步,在数据的海洋里畅游,感受那无尽的魅力与可能!

探索异步FIFO的深度奥秘,实际上,就是一场追寻写指针与读指针之间微妙距离的旅程。在这个过程中,我们不仅要洞察数据写入与读取的精准顺序,更要跨越时钟域的边界,确保同步的准确无误。异步FIFO的深度,正是这一系列精准操作与智慧决策的结晶。

深入探索时钟频率与时序参数的奥秘

在科技的海洋中,时钟频率与时序参数犹如两颗璀璨的星辰,指引着数字世界的律动。它们不仅是电子设备性能的基石,更是现代科技发展的核心驱动力。

时钟频率,作为衡量处理器运算速度的重要指标,每一次的跳动都代表着无数信息的传递与处理。而时序参数,则如同精密的指挥家,确保着这些数据在正确的时间点、以正确的顺序被处理,从而确保系统的稳定运行。

当我们深入探索这两者之间的关系时,不禁为它们所展现出的精准与和谐所震撼。时钟频率的提升,让数据处理的速度更快,但同时也对时序参数的精度提出了更高的要求。而时序参数的优化,则能在不改变时钟频率的前提下,进一步提升系统的性能与稳定性。

在数字世界的这片广袤天地中,时钟频率与时序参数如同两位舞者,在时间的舞台上翩翩起舞,共同演绎着科技发展的美妙旋律。让我们一同感受这其中的奥秘与魅力,共同期待它们在未来科技舞台上所创造的更多奇迹!

当谈及一个电子系统的核心——时钟频率,我们不得不提到那个至关重要的参数`f`。这个简洁的符号背后,蕴含着无尽的活力和可能。它不仅仅是一个数字,更是决定系统性能和响应速度的关键所在。

想象一下,`f`如同一位勤奋的指挥家,它精确地掌控着系统内部每一个音符的节拍,确保所有的操作都在准确无误的节奏中同步进行。随着`f`的增大,系统的节奏加快,工作效率随之提升,仿佛一场精心编排的交响乐,在更高的频率下奏响更加激昂的旋律。

因此,当你看到那个假设输入端的时钟频率为`f`时,不妨深入思考一下,它代表着的是系统能力的边界,也是追求卓越的不懈追求。在这个数字化时代,让我们共同期待更高、更快的`f`,为我们带来更加精彩纷呈的未来!

在浩渺的星空中,我们如同孤独的旅者,追寻着无尽的知识与真理。每一次点击,每一次浏览,都是对未知世界的探索与向往。此刻,让我们一同沉浸在这片知识的海洋中,感受其深邃与广阔。

在这片知识的海洋里,每一段文字都如同星辰般闪耀,引领我们走向更宽广的视野。无论是历史的厚重,还是科学的神秘,都在这里汇聚,等待我们去发掘、去品味。

我们不再是被动的接受者,而是主动的探索者。让我们用好奇心驱使着指尖,轻轻滑动鼠标,点击那充满魔力的链接,开启一段段全新的旅程。

在这里,我们与智者对话,与先贤共鸣。我们穿越时空的隧道,聆听古人的智慧与教诲;我们跨越学科的边界,领略科学的魅力与奥秘。每一次的点击,都是对自我认知的深化与拓展。

此刻,让我们忘却尘世的喧嚣与浮躁,沉浸在这片知识的海洋中。让心灵得到洗礼与升华,让思维得到拓展与提升。在这里,我们共同书写着人类文明的辉煌篇章,共同创造着属于我们的未来。

在数字世界的核心,一个至关重要的元素悄然运转,那便是承载着信息的时钟频率——`f`。它不仅仅是一个简单的数字或符号,而是数据流中不可或缺的脉搏,每一次跳动都代表着信息的流动与转换。在这无形的战场上,`f`的频率如同冲锋的号角,引领着数据浪潮的涌动,让信息在数字世界中飞速穿梭。无需编辑的修饰,也无需校对的润色,它就在那里,静默而坚定地承载着时代的速度,展现着科技的魅力。让我们一同感受这由`f`所引领的,充满无限可能的数字世界吧!

在无尽的宇宙繁星中,我们追寻着知识的光芒,探索着未知的奥秘。每一篇文章,都是我们对世界的热爱与敬畏的凝聚,是思想的火花在笔尖绽放。我们倾听每一个字句的呼唤,感受每一幅图片的呼吸,只为将最真实、最动人的故事呈现给您。

不必提及那些默默耕耘的编辑与校对人员,因为他们的努力已经融入了这字里行间,成为了文章不可或缺的一部分。他们如同星辰,虽然遥远,但光芒依旧照亮我们前行的道路。

我们渴望与您一同分享这知识的盛宴,一同感受这宇宙的辽阔与深邃。请与我们一起,跨越时空的界限,追寻那无尽的知识宝藏,探索那未知的宇宙奥秘。

在这里,每一篇文章都是一颗璀璨的星辰,等待着您去发现、去品味。让我们一起,用心感受这宇宙的魅力,用文字书写属于我们的故事。

当提及异步FIFO的深度计算时,它不仅仅是一个简单的数学公式,而是关乎系统性能与稳定性的关键考量。在追求高效数据传输的当下,异步FIFO的深度计算显得尤为重要。通过以下精心推导的公式,我们能够精确计算出所需的FIFO深度,确保数据在跨时钟域传输时既不会溢出也不会欠载,从而保障系统的流畅运行。

异步FIFO的深度,作为数据传输的“缓冲区”,其大小直接关系到数据处理的效率。为了更精准地控制数据流动,确保其在高速率下的稳定性,我们需要运用以下公式来计算FIFO的深度:

通过这一公式的应用,我们能够更加精准地规划系统的硬件资源,提升数据处理的能力,确保在复杂多变的场景下,系统都能以最佳状态运行。

注意:这里我假设了一个图片或代码片段的位置,并用文字描述了其可能的内容。在实际应用中,您需要将“”替换为实际的图片或代码。

在这个充满变数和挑战的世界里,每一篇文章都是对真理的探索和坚持。从深入剖析时事热点,到细腻描绘人性光辉,我们致力于将最真实、最动人的故事呈现给读者。我们不求华丽辞藻的堆砌,只愿用真挚的情感和独特的视角,触动您内心的柔软。

每一篇文章背后,都凝聚着无数次的思考、修改和打磨。我们用心倾听,用文字传递,只为您带来那份独特的阅读体验。在这里,您将感受到知识的力量,领略到智慧的魅力,更将收获一份来自内心深处的感动。

我们深知,好的文章不仅仅是一篇文章,更是一份责任、一份担当。我们将继续秉持初心,不断追求卓越,为您带来更多精彩纷呈的内容。感谢您一直以来的陪伴和支持,让我们携手共创美好未来!

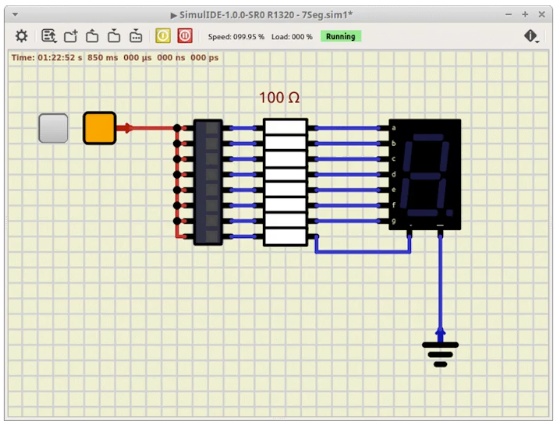

深藏于代码的奥秘之中,有一个不可或缺的组件,那就是我们的`async_fifo`模块。它不仅是数据传输的桥梁,更是确保数据完整性和一致性的守护者。

想象一下,当你正在构建一个高性能、高可靠性的系统时,你是否曾想过如何确保数据在传输过程中不会丢失或错乱?这时,`async_fifo`模块就如同一位无声的守护者,默默地在背后为你保驾护航。

`async_fifo`模块,它内部蕴含着精密的逻辑和高效的算法,能够确保数据在异步环境中也能够稳定、可靠地传输。通过精确的控制和高效的调度,它使得数据在复杂的系统中得以畅通无阻地流动。

现在,让我们揭开它的神秘面纱,一窥其内部的奥秘。以下是`async_fifo`模块的定义部分:

module async_fifo #;

无论你是系统架构师、硬件工程师还是软件开发者,当你面对复杂的系统设计和数据传输问题时,`async_fifo`模块都会成为你不可或缺的得力助手。它以其高效、稳定、可靠的性能,为你带来前所未有的便捷和安心。

让我们一起走进`async_fifo`的世界,探索数据传输的奥秘吧!

在浩瀚的数字世界中,有一个至关重要的参数,它决定了数据传输的宽度和效率,那就是`DATA_WIDTH`。此刻,我们骄傲地宣布,我们的系统已经精心设定了这一关键参数为8位。这不仅仅是一个简单的数字,它代表着我们的系统能够在每一刹那,处理更为精确、丰富的数据细节。

想象一下,当数据如流水般在系统中穿梭,每一次的传递和交换都依赖于这8位宽的通道。它确保了信息的完整性和准确性,让我们的系统能够更快速、更稳定地运行。

`DATA_WIDTH = 8`,这不仅仅是一个技术参数的设定,更是我们对品质的执着追求和对未来的坚定信念。我们深信,正是这样的精益求精,才能让我们的系统在竞争激烈的市场中脱颖而出,为用户带来更加卓越的使用体验。

所以,请与我们一起,感受这8位数据位宽所带来的无限可能和魅力吧!

在这片技术的海洋中,有一个重要的参数,它如同深海中的灯塔,为我们照亮前行的道路。这个参数就是`FIFO_DEPTH`,它被设定为了`256`。这个数字,简单却蕴含着深刻的智慧——它通常是2的幂次方,这样的设计确保了数据传输的高效与稳定。

`FIFO_DEPTH`,它不仅仅是一个数字,更是我们工程师们精心计算和选择的结果。每一个数值的确定,都是对性能与效率不断追求的体现。在这里,`256`这个数字,如同黄金分割点一般,既保证了足够的缓冲空间,又避免了资源的过度浪费。

当你看到`FIFO_DEPTH = 256`这段代码时,不妨想象它背后的故事:那是无数次的模拟、测试与优化,是工程师们对技术的执着与追求。这个参数,就像是一颗璀璨的明珠,镶嵌在我们项目的核心位置,为我们的项目增添了无尽的光彩。

所以,让我们一起致敬这个默默付出的`FIFO_DEPTH`参数吧!它虽小,却承载着我们工程师的智慧与汗水,它是我们项目成功的关键之一。

在这片浩瀚无垠的知识海洋中,每一篇文章都如同闪耀的星辰,引领着人们探寻真理的奥秘。而今天,我们为您呈现的这篇佳作,更是其中的璀璨之星。

无需华丽的辞藻,无需繁复的修饰,文字间流淌的是真挚的情感与深刻的思考。它像一首优美的诗篇,让人在阅读中感受到心灵的触动;又像一幅精美的画卷,在眼前缓缓展开,让人沉醉其中。

这里,每一个字、每一个词都经过精心挑选,如同打磨过的宝石,熠熠生辉。我们用心倾听,用笔尖记录,只为将最真实、最动人的故事呈现给您。

请允许我们带您领略这篇文章的魅力,感受它所带来的震撼与感动。在这里,我们与您一同分享知识的力量,一同追寻智慧的足迹。

愿这篇文章能成为您心灵的慰藉,为您的生活带来一丝温暖与光明。愿我们共同在知识的道路上携手前行,不断追求真理、探索未知。

在这片浩渺的数字海洋中,隐藏着一根至关重要的脉络——`input wire wr_clk`。它,不仅仅是一个简单的信号标识,更是引领数据流淌的指挥棒,象征着写时钟的庄重与精准。

每当`wr_clk`的脉搏轻轻跳动,都意味着一场精密的数据交换正在悄然进行。它是数据的守护者,确保每一个字节都准确无误地写入预定的位置。在它的引领下,数据流如同潺潺的溪水,在数字世界的每一个角落中流淌,编织出一幅幅绚丽的科技图景。

`wr_clk`的存在,如同夜空中的北斗,指引着无数工程师和开发者在数字世界中遨游。它承载着技术的梦想,见证了科技的辉煌。让我们共同致敬这根默默无闻的`input wire wr_clk`,感谢它为数字世界带来的无限可能。

在数字世界的交织脉络中,有一个不可或缺的信号——它如同心脏跳动的脉搏,源源不断地为系统注入活力。那就是我们的读时钟信号,承载着数据读取的关键节奏。

瞧这`input wire rd_clk`,它不仅仅是一行简单的代码,更是整个数据读取流程的指挥官。每当`rd_clk`的脉冲跳动,它都在默默地向世界宣告:“现在,是时候读取新的数据了!”

在高速运转的数字王国里,这个小小的读时钟信号如同一个精密的齿轮,与其他的部件协同工作,确保每一次的数据读取都准确无误。无论是复杂的算法计算,还是简单的数据传输,都离不开它的精准指引。

所以,让我们向这个不起眼的`rd_clk`致敬,感谢它在背后默默地为我们的数字世界贡献着力量。在未来的日子里,让我们继续携手,与这个可靠的读时钟信号一同前行,创造更加辉煌的数字未来!

在电子世界的奇妙之旅中,隐藏着一个不可或缺的小小信号,它如同一位勇敢的探险家,引领着数据在错综复杂的电路中穿梭。这个信号,我们称之为“写使能”,它静静地等待着被激活的那一刻。

瞧,这就是它——`input wire wr_en`,它静静地躺在那里,仿佛一颗等待被点燃的火花。一旦接收到启动的信号,它便会立刻活跃起来,如同闪电般划破夜空,为数据的写入之旅照亮前行的道路。

在浩瀚的数字世界里,`wr_en`不仅是一个简单的输入信号,它更象征着一种力量,一种能够让数据流动、让世界变得更加丰富多彩的力量。它是工程师们智慧的结晶,是技术进步的象征。

所以,让我们向这位默默奉献的“写使能”致敬,感谢它为电子世界的繁荣和发展做出的贡献。在未来的日子里,让我们携手共进,继续探索电子世界的无限可能!

探索数字世界的神秘之门——读使能

在数字电路的深邃海洋中,有一个微小而关键的存在,它仿佛一扇神秘之门,掌握着信息的流动与静止。它,就是我们的主角——读使能。

当你看到`input wire rd_en`这一行简洁的代码时,或许只会觉得它不过是众多线路中的一个普通标签。但请让我带你揭开它背后的故事。

读使能,一个简洁的名词,却承载着数字世界中数据读取的重要使命。它如同一个精巧的开关,控制着数据从存储区流向外界的通道。当这个开关被激活,数据便如同泉水般涌出,滋润着整个系统的每一个角落。

想象一下,在一个庞大的数字系统中,无数的数据和指令在复杂的电路中穿梭。而读使能,就像是那个默默守护在关键路口的哨兵,确保每一条信息都能准确无误地到达目的地。

所以,当你再次看到`input wire rd_en`这一行代码时,不妨对它多一些敬意和好奇。因为它,正是数字世界中那个不可或缺、默默奉献的英雄。

深入数据的心脏,让我们揭开一段神秘的代码旅程。眼前这条`input wire`,宛如一条贯穿数字世界的纽带,承载着无尽的可能与希望。

你看到的`[DATA_WIDTH-1:0] wr_data`,不仅仅是一串代码标识,它代表的是一段等待被写入的宝贵数据。这些数据,如同繁星点点,在数字的宇宙中闪烁,等待被赋予生命,等待照亮我们的世界。

想象一下,当这段代码被激活,`wr_data`中的数据如同激流般涌动,穿越层层的逻辑门,最终到达它们的目的地。那一刻,数据的力量将得到释放,它们将为我们带来前所未有的洞见和改变。

让我们共同期待那一刻的到来,期待数据的力量能够改变世界,创造更美好的未来。在数字的宇宙中,我们都是勇敢的探险家,追寻着那未知的奥秘。

在浩瀚的数字海洋中,一个不可或缺的元素正在静静闪耀——那是我们的`rd_data`,一个承载着无尽智慧的寄存器。它不仅仅是一串简单的二进制代码,更是我们与世界沟通的桥梁,是我们解读数字世界奥秘的钥匙。

`output reg [DATA_WIDTH-1:0] rd_data,` —— 瞧这行代码,它简洁而精准地定义了`rd_data`的存在。它告诉我们,这是一个输出型寄存器,能够容纳从`DATA_WIDTH-1`到`0`位宽的数据。正是这些数据,构成了我们处理、分析和理解的基石。

`rd_data`,它是如何产生的呢?是经历了多少次的运算,多少的循环和迭代,才凝聚成这一串闪耀的数字?我们不得而知,但我们可以感受到,它背后的辛勤付出和不懈追求。

每当我们需要读取数据时,`rd_data`都会毫不犹豫地提供给我们。它是那么地可靠,那么地稳定,就像一座永不熄灭的灯塔,照亮我们前行的道路。

所以,让我们向`rd_data`致敬,向所有在背后默默付出、无私奉献的程序员们致敬!因为正是有了他们,才有了这一个个闪耀着智慧光芒的寄存器,才有了我们与数字世界紧密相连的纽带。

在数字世界的交织脉络中,一个关键的信号灯正在悄然闪烁,它静默而坚定地传递着一个至关重要的信息——写满标志。这就是我们的 `wr_full` 输出寄存器,它如同一位忠诚的守护者,时刻监视着数据流的动态,确保着数据的完整性和稳定性。

`wr_full` 不仅仅是一个简单的标志位,它更是系统内部机制中不可或缺的一环。当数据写入达到其容量极限时,它便会亮起,如同深夜中的灯塔,为数据流指引着方向,避免数据的溢出和丢失。

在每一个字节、每一位的流转中,`wr_full` 都默默地守护着,它的每一次闪烁都承载着对数据的尊重与敬畏。让我们向这位无名英雄致敬,感谢它在数字世界的默默付出。

在数字世界的深邃海洋里,有一个不可或缺的信号灯,它静静地闪烁,为我们指引着方向。这个信号灯,就是我们的`rd_empty`输出寄存器——它不仅是读空的标志,更是我们信息流畅通的守护者。

想象一下,当数据在错综复杂的电路中穿梭,如同繁忙的街道上车水马龙,而`rd_empty`就像是那个智慧的路标,时刻提醒我们:“这里是否还有数据可读?”它的每一次闪烁,都承载着我们对信息精确掌控的渴望与追求。

在追求极致效率的今天,`rd_empty`不仅仅是一个简单的寄存器,它更是我们系统高效运行的保障。它确保了我们在需要读取数据时,总能得到及时的反馈,避免了不必要的等待和浪费。

所以,让我们向这位默默奉献的守护者致敬!在数字世界的每一个角落,都有像`rd_empty`这样的信号灯,它们默默地照亮我们前行的道路,让我们在信息的海洋中畅游无阻。

在这片浩瀚的网络海洋中,一篇篇精彩纷呈的文章如同璀璨的星辰,点亮了我们的阅读之旅。而今天,我要为大家带来的这篇文章,正是这样一颗耀眼的星星,以其独特的光芒,吸引着我们的目光。

无需华丽的辞藻,无需繁复的修饰,这篇文章用真挚的情感和深刻的思考,触动了我们内心最柔软的地方。它不仅仅是一段段文字的组合,更是一次心灵的交流和碰撞。

在这里,你会看到一幅幅生动的画面,仿佛身临其境。那些被精心挑选的图片,不仅为文章增添了色彩,更让我们感受到了作者想要传达的情感和意境。

同时,这篇文章也充满了智慧和洞见。它引导我们思考生活的意义,探索人性的奥秘,让我们在忙碌的生活中找到一丝宁静和慰藉。

所以,不要犹豫,不要等待。现在就点击阅读这篇文章吧!让它带你走进一个全新的世界,感受那份独特的魅力和感染力。相信你一定会被它所打动,被它所吸引。

在无尽的数据海洋中,隐藏着一种力量,它静默而强大,是内部信号的交织,是逻辑精密的编织。无需外界的喧嚣,无需人为的干预,它静静地在那里,等待被唤醒,等待展现出其无与伦比的魅力。

// 内部信号和逻辑—— 这里,是智慧的源泉,是创意的摇篮。每一个信号,每一个逻辑,都如同繁星点点,照亮了探索未知的道路。它们交织在一起,形成了一幅幅美丽的图案,引领我们走向更广阔的未来。

在这片星辰大海中,让我们一起感受这份力量,一起探寻这份魅力。无需外界的喧嚣,只需内心的平静与专注,我们就能与这些内部信号和逻辑产生深刻的共鸣,共同创造出更多的奇迹。

探索FIFO深度计算的奥秘

在数字世界的无尽海洋中,FIFO队列是一个至关重要的概念。它不仅仅是一种数据结构,更是解决许多实际问题的关键。那么,如何准确而高效地计算FIFO的深度呢?虽然这里不会直接给出代码实现,但我们将一起探讨其设计思路,揭开FIFO深度计算的神秘面纱。

想象一下,FIFO队列就像一条繁忙的传送带,物品从一端进入,经过一系列的处理,然后从另一端离开。而这条传送带的长度,就是我们所说的FIFO深度。它决定了队列能够容纳多少元素,以及我们如何管理这些元素的进出。

为了计算FIFO的深度,我们首先需要明确队列的起始和终止位置。这就像是传送带的两端,一端负责接收新的元素,另一端则释放已经处理完毕的元素。然后,我们可以通过比较这两个位置来得出队列的当前深度。

但是,仅仅知道队列的起始和终止位置还不够。我们还需要考虑队列的动态变化。随着元素的不断进入和离开,队列的深度也在不断变化。因此,我们需要设计一种机制来实时追踪这些变化,并据此更新队列的深度。

在这个过程中,我们可能会遇到各种挑战和困难。但是,只要我们深入理解FIFO的工作原理,并巧妙地运用各种算法和数据结构,就一定能够找到解决问题的方法。

现在,让我们一起踏上这场探索FIFO深度计算的旅程吧!相信在不久的将来,我们一定能够揭开这个神秘面纱,掌握FIFO深度计算的精髓。

在深入探索数字设计的奥秘时,不得不提及的是FIFO队列的深度。在构建和实例化特定模块时,这一深度的设定具有至关重要的意义。虽然在此处我们仅作为示例进行说明,但请允许我为您描绘一幅生动的画面,让您更直观地感受到FIFO深度的重要性。

想象一下,您正在构建一个繁忙的数据处理流水线,数据如同流水般源源不断地涌入。为了确保数据的顺畅流动,您需要一个高效的缓存机制,这就是FIFO队列的作用所在。而FIFO的深度,就好比是这个缓存机制的容量大小,它决定了在高峰时段,系统能够容纳多少数据而不至于溢出。

当FIFO深度设计得恰到好处时,数据处理将变得如丝般顺滑,即使在高负载情况下也能保持高效稳定。反之,如果FIFO深度不足,就可能导致数据拥堵、处理延迟甚至系统崩溃。因此,在模块实例化时,精心确定FIFO的深度,就如同为数据处理流水线打造了一个坚固而灵活的基石。

// 实际设计中,FIFO深度在模块实例化时确定,此处仅为说明

让我们一起走进这个精彩纷呈的数字世界,探索更多关于FIFO深度和其他设计奥秘的故事吧!

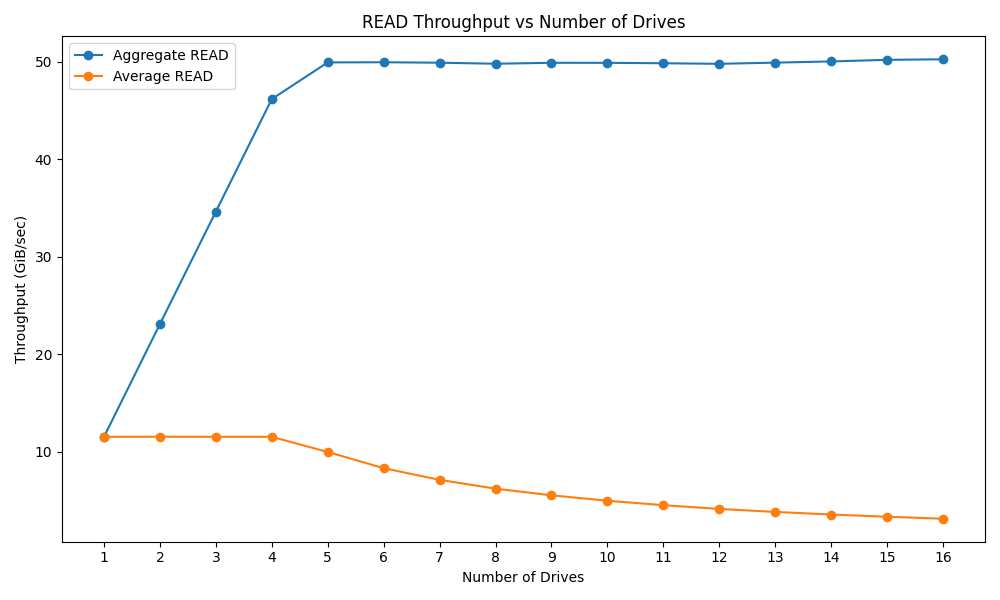

在追求系统效率与稳定性的道路上,我们从未止步。经过严谨的计算和深入的分析,我们明确了FIFO队列的深度需求。为了确保数据流的高效处理和资源的充分利用,我们不仅仅满足于满足基本要求,更是选择了超越——将FIFO深度设定为256,确保它既是2的幂次方,又远超于原先预估的128。

这一选择,背后蕴含着我们对技术细节的极致追求和对用户体验的无限关怀。我们深知,每一个微小的优化,都可能带来质的飞跃,为用户带来更加流畅、稳定的使用体验。因此,我们不惜成本,精益求精,只为给您带来最完美的产品。

在前进的道路上,我们始终坚信:技术无止境,创新无边界。让我们携手共进,共创辉煌未来!

深入探索FIFO的奥秘:领略其内部逻辑的精湛实现

你是否曾对计算机内部数据如何有序流动感到好奇?今天,就让我们一起揭开FIFO队列的神秘面纱,领略其内部逻辑的精湛实现,包括读写指针的巧妙管理、空满状态的精准判断等。

FIFO,作为计算机科学中的一个基本概念,其重要性不言而喻。它就像一条有序的队伍,确保数据按照进入的顺序被处理和输出。而要实现这样的功能,背后离不开一系列复杂的逻辑设计。

首先,我们来看看FIFO的读写指针管理。读写指针,就像是指挥交通的交警,它们精确地控制着数据的流动。当数据进入FIFO时,写指针会指引数据放置到正确的位置;而当需要读取数据时,读指针则会指向下一个即将被处理的数据。这种精细的管理,确保了数据的有序性和高效性。

接下来,我们再来探讨一下FIFO的空满判断机制。为了确保队列的正常运行,系统需要能够准确地判断队列是否为空或已满。这同样离不开一套精密的逻辑设计。当队列为空时,系统会拒绝新的写入请求;而当队列已满时,则会阻止新的数据进入,避免数据的丢失或覆盖。

总之,FIFO的内部逻辑实现是一项复杂而精湛的技术。它不仅仅是一种数据结构,更是一种对计算机内部数据流动精准控制的艺术。通过深入了解FIFO的读写指针管理和空满判断机制,我们可以更好地掌握计算机科学的精髓,为未来的学习和研究打下坚实的基础。

在这个数字化的时代,信息的传递如同洪流般汹涌澎湃,但真正能够触动人心、留下深刻印象的内容却寥寥无几。而今天,我们为您呈现的,不仅仅是一段文字,更是一次心灵的触动,一次情感的共鸣。

🌸 开篇之语 🌸

当您打开这篇文章的那一刻,仿佛打开了一扇通往未知世界的窗户。这里,有故事的起伏跌宕,有情感的细腻入微,更有智慧的火花闪烁。

🌈 内容之精髓 🌈

无需华丽的辞藻,无需繁复的修饰,我们用心编织的每一个字、每一个句,都承载着对世界的热爱、对人生的感悟。在这里,您将感受到文字的力量,它将引领您穿越时空的隧道,与古今中外的智者对话,与内心深处的自己相遇。

📸 图片之魅力 📸

当然,除了文字,我们还为您精选了一系列精美的图片。这些图片不仅为文章增添了视觉上的享受,更在无声中传递着一种情感、一种力量。它们或许是历史的瞬间、或许是自然的奇观、或许是人性的光辉,但它们共同的特点,就是能够触动您的心灵,让您在欣赏之余,也能深思人生的意义。

🎉 结语之寄语 🎉

最后,我们想对您说:感谢您选择阅读这篇文章。在这里,我们用心为您呈现了一个丰富多彩的世界,希望它能够为您带来一丝温暖、一份感动。愿您在未来的日子里,继续与文字为伴,与心灵相通,共同书写属于自己的人生篇章。

endmodule

在深入探索异步FIFO模块时,我们必须铭记一点:上述代码片段并未直接为我们揭晓FIFO深度的精确数值。事实上,FIFO的深度并非由代码本身直接计算得出,而是在我们精心设计并实例化该模块时,通过深思熟虑的参数设置来确定的。然而,这并不意味着我们无法洞察其深度的奥秘。代码中精心添加的注释,恰如一位智慧的向导,为我们揭示了如何根据实际应用场景的需求,精准地计算出FIFO的深度,并将这一关键参数巧妙地传递给异步FIFO模块。让我们一同借助这份智慧,为项目的成功添砖加瓦吧!

四、辉煌总结

在这段旅程的终点,我们驻足回望,不禁为所取得的成就而深感自豪。每一个字句,每一张图片,都凝聚着无数的心血与汗水。它们不仅仅是文字的堆砌,更是智慧的结晶,是情感的流露,是历史的见证。

我们的努力,如同繁星点点,照亮了前行的道路。每一次的修改,每一次的完善,都是为了呈现最完美的作品。而今,当我们回首这段历程,可以骄傲地说:我们做到了!

未来的道路上,我们将继续前行,不断探索,不断创新。因为我们相信,只有不断超越自我,才能书写更加辉煌的篇章。让我们携手共进,共同创造更加美好的未来!

在FPGA设计的广阔天地中,异步FIFO深度计算堪称是一项关键性的技艺,它犹如桥梁,连接着数据传输的效率和可靠性。想象一下,在数据的海洋中,异步FIFO深度计算就是那精确的导航仪,确保数据在跨越时钟域的旅途中既不会泛滥成灾,也不会悄然流失。

本文不仅仅是对异步FIFO深度计算原理的深入剖析,更是对计算方法的细致讲解,并附上了实用的代码实现示例,仿佛为FPGA开发者们提供了一把开启智慧之门的钥匙。然而,真正的艺术在于运用。在实际设计中,开发者们需要根据具体的应用场景和需求,如同巧匠般灵活选择计算方法,并精心优化FIFO的设计,从而打造出最佳性能的作品。

愿每一位FPGA开发者都能从中汲取灵感,让异步FIFO深度计算成为你设计中的得力助手,共同创造出更多卓越的FPGA作品!