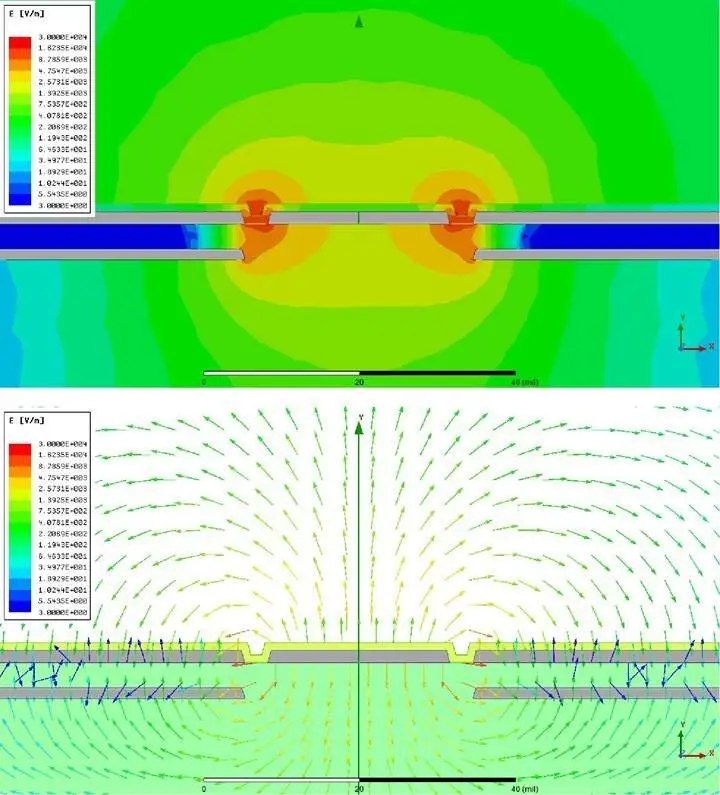

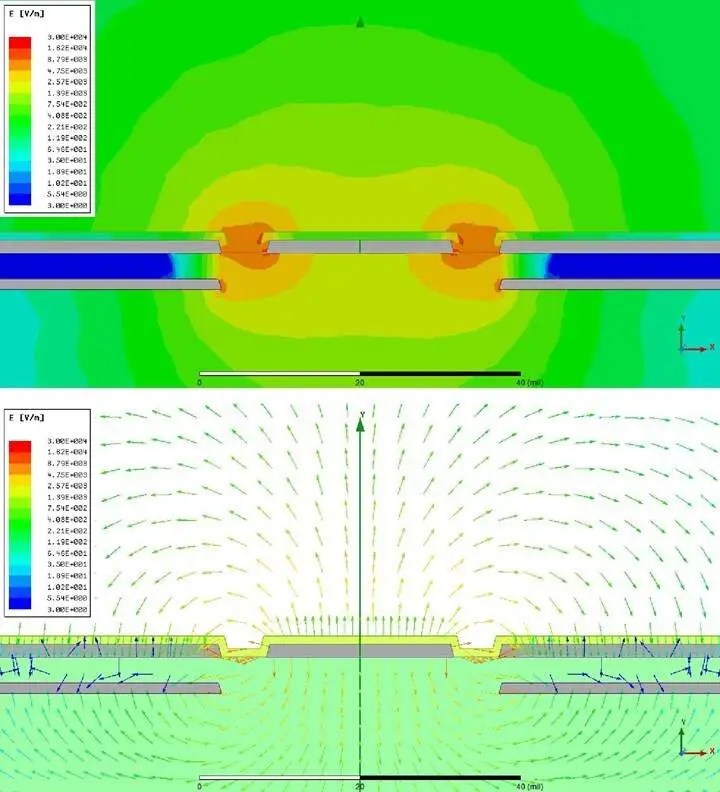

下图显示了不同接地平面切口宽度的模拟 E‐Field 图以及原始 PCB 设计。这些 E‐Field 图用于确认结构设计正确并发现任何问题区域。例如,在具有较小宽度的第 2 层接地平面切口的模拟中,可以看到共面迹线的 E‐Field 与第 2 层接地平面强烈耦合,从而降低了迹线的阻抗。

每种配置将呈现两个图。E‐场强图显示电介质(FR4、阻焊层和走线上方的空气)中 E‐场的图表,颜色编码以指示场强。矢量图以矢量格式显示 E‐场。这也是颜色编码以反映场强。

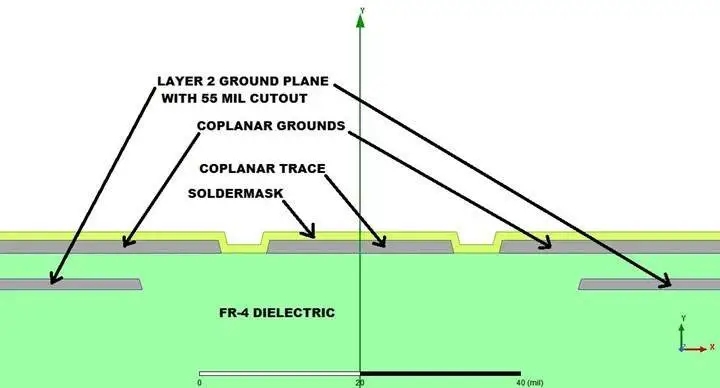

下图显示了在 Ansoft Q2D 中建模的 GCPW,其中标出了组成结构。查看 E‐field 图时,使用此图来确定方向。第 3 层的返回接地平面未显示在该图中,也未显示在 E‐field 图中。

在 Ansoft Q2D 中建模的 GCPW

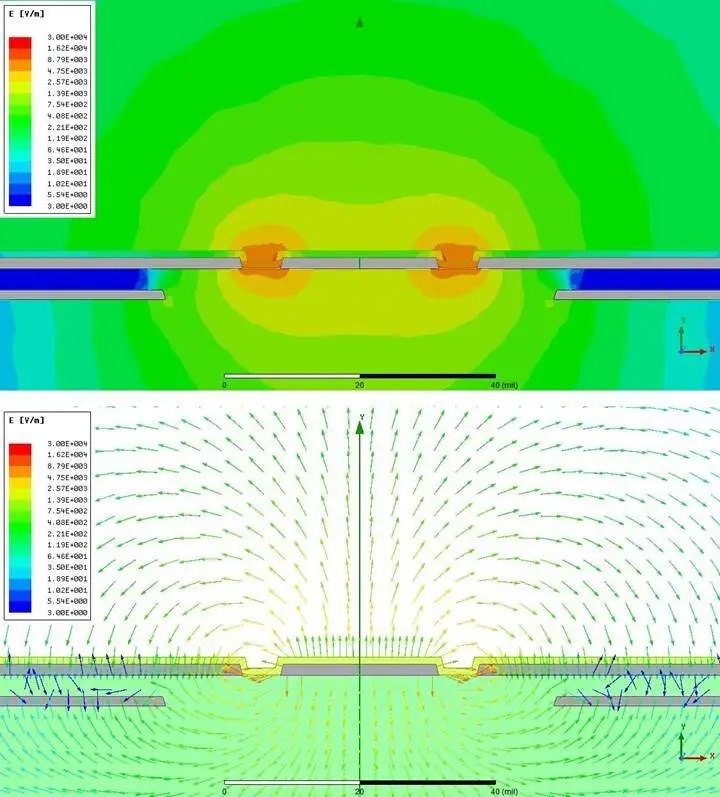

原始设计:3 mil 共面间隙,30 mil 第 2 层接地平面间隙:下图显示了原始设计中的 E‐Field,共面间隙为 3‐mil,第 2 层接地平面间隙为 30‐mil。共面走线与第 2 层接地平面之间的耦合非常强。这种强耦合加上太小的共面间隙导致模拟的共面阻抗为 36.5 欧姆。

原始设计:3 mil 共面间隙,30 mil 第 2 层接地平面间隙

错误设计:5.7 mil 共面间隙,35 mil 第 2 层接地平面间隙:下图显示了阻抗优化的 5.7 mil 共面间隙设计的 E‐Field,但第 2 层接地平面的间隙宽度为 35 mil。这说明了(相对常见的)情况,即设计人员使用正确的共面间隙,但错误地将第 2 层接地间隙实现为与总共面接地间隙(35 mil)相同的宽度。如我们所见,从共面走线到第 2 层接地平面的耦合相当强,这导致模拟的共面阻抗为 46.5 欧姆。

错误设计:5.7 mil 共面间隙,35 mil 第 2 层接地平面间隙

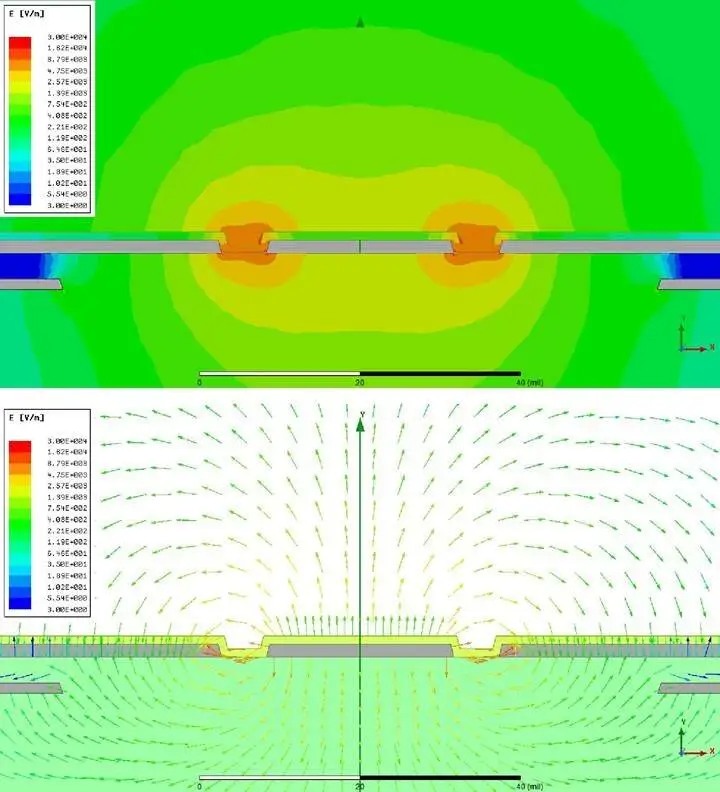

优化设计:5.7 mil 共面间隙,58 mil 第 2 层接地平面间隙:下图显示了阻抗优化的 5.7 mil 共面间隙和第 2 层接地平面中 58 mil 宽间隙的设计的 E‐Field。L2 接地平面间隙优化扫描显示,第 2 层接地平面中大于 58 mil 的间隙不会显著影响阻抗;因此,接地平面切口设置为 58 mil。

在这种配置中,与第 2 层接地平面的耦合很小,模拟阻抗为 49.9 欧姆。

优化设计:5.7 mil 共面间隙,58 mil 第 2 层接地平面间隙

大接地平面切口:5.7 mil 共面间隙,75 mil 第 2 层接地平面间隙:下图显示了具有阻抗优化的 5.7‐mil 共面间隙和第 2 层接地平面中 75‐mil 宽间隙的设计的 E‐Field。该图显示,如果第 2 层接地平面间隙加宽超过 58 mil,L2 接地平面耦合不会显著减少。但这种宽接地平面间隙可能会干扰 PCB 上的其他布线。

在这种配置中,与第 2 层接地平面的耦合非常低,模拟阻抗为 50.0 欧姆。

大型接地平面切口:5.7 mil 共面间隙,75 mil 第 2 层接地平面间隙

结论

免费阻抗计算工具通常功能有限。它们可能允许您或不允许您对凹蚀或阻焊层进行建模,并且它们通常不适合对多层几何结构中各层之间的场相互作用进行建模。

对于多层堆叠上的某些接地共面配置,共面接地参考平面可能是共面迹线下方的两个或更多个 PCB 层。这需要在位于接地平面参考层上方的那些层上的共面迹线下方设置一个铜禁区。试图直观地估计该铜禁区的最佳尺寸充其量是困难的。低估禁区的尺寸可能会导致不可预见的电磁场相互作用,而高估禁区的尺寸可能会导致 PCB 设计上宝贵的布线面积不必要地损失。

一些设计人员使用众多可用的传输线工具之一来使其走线的阻抗“足够接近”,然后他们依靠他们的工厂使用商业阻抗计算器(例如 Polar)来计算正确的几何形状并在蚀刻电路板时拨入阻抗。不幸的是,这种方法无法捕捉 PCB 结构之间无意耦合的问题,因为工厂不使用 PCB 上的实际走线来测量电路板制造过程中的阻抗。相反,工厂使用蚀刻有设计人员的走线几何形状的测试试样。这些测试试样不会复制 PCB 设计上发生的与附近结构的无意耦合。因此,工厂将无法补偿这些相互作用,并且电路板上的 PCB 走线的阻抗将不正确,即使测试试样具有正确的阻抗。

如果您正在设计接地共面波导到您的电路板上,那么您会希望第一次就做好。大多数 Wi-Fi 和蓝牙设计在电路板启动时似乎工作正常,即使天线馈线严重不匹配。但是,在您已经宣布胜利之后,糟糕的设计几乎总会在范围测试或数据完整性测试中显现出来。