在现代电子设计自动化(EDA)领域,Verilog作为一种硬件描述语言(HDL),被广泛应用于数字电路和系统级设计。Verilog的模块化设计思想是其强大功能的核心,而例化(instantiation)则是实现这一思想的关键步骤。本文将深入探讨Verilog中的例化概念,通过实例说明如何在设计中有效地使用例化,以及它如何促进设计的可重用性、可读性和可维护性。

一、Verilog例化的基本概念

Verilog例化是指在一个模块内部引用(或“实例化”)另一个模块的过程。这种机制允许设计师将复杂的系统分解成多个更小、更易于管理的部分,每个部分都可以作为一个独立的模块进行设计、测试和验证。然后,这些模块可以通过例化的方式组合在一起,形成完整的系统。

二、Verilog例化的语法

在Verilog中,例化一个模块的基本语法如下:

verilog

模块名 实例名 (

.端口名1(连接信号1),

.端口名2(连接信号2),

...

.端口名N(连接信号N)

);

其中,“模块名”是被例化的模块的名称,“实例名”是当前例化实例的唯一标识符,“端口名”和“连接信号”分别对应被例化模块的端口和当前模块中用于连接这些端口的信号。

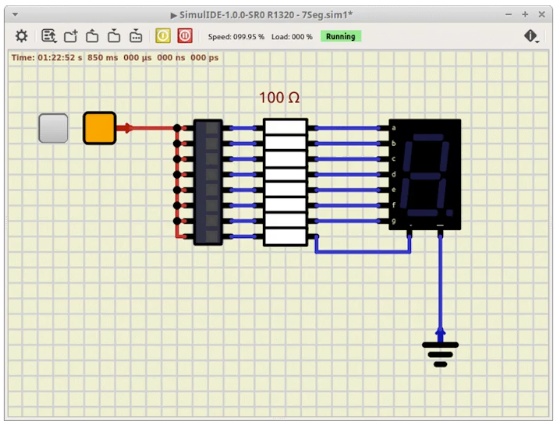

三、Verilog例化的实际应用

以设计一个简单的加法器系统为例,我们可以将其分解为两个模块:一个4位加法器模块和一个顶层模块。4位加法器模块负责执行具体的加法运算,而顶层模块则负责例化加法器模块,并提供必要的输入和输出端口。

4位加法器模块设计:

verilog

module adder4bit (

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

// 加法器逻辑实现

assign {cout, sum} = a + b + cin;

endmodule

顶层模块设计:

verilog

module top_module (

input [3:0] a,

input [3:0] b,

input cin,

output [3:0] sum,

output cout

);

// 例化4位加法器模块

adder4bit u1 (

.a(a),

.b(b),

.cin(cin),

.sum(sum),

.cout(cout)

);

endmodule

在顶层模块中,我们通过adder4bit u1语句例化了一个名为u1的4位加法器实例,并通过端口映射将顶层模块的输入和输出端口与加法器模块的相应端口连接起来。

四、Verilog例化的优势

模块化设计:例化机制使得设计师可以将复杂的系统分解成多个模块,每个模块都可以独立地进行设计、测试和验证,从而降低了设计的复杂性。

可重用性:一旦一个模块被设计并验证为正确,它就可以在不同的设计中被重用,无需从头开始设计。

可读性和可维护性:通过将系统分解为多个模块,并清晰地展示它们之间的连接关系,例化提高了设计的可读性。同时,如果需要修改某个模块的功能或修复错误,只需关注该模块本身,而无需对整个系统进行大规模的修改。

层次化设计:例化支持层次化设计,允许设计师在顶层模块中组合多个子模块,形成更复杂的系统。这种设计方式有助于设计师在抽象层次上理解和管理系统。

五、结论

Verilog例化是构建模块化设计的基石,它使得设计师能够将复杂的系统分解成多个更小、更易于管理的部分,并通过组合这些部分来形成完整的系统。通过有效地使用例化,设计师可以提高设计的可重用性、可读性和可维护性,从而加速设计过程并提高设计质量。随着EDA技术的不断发展,Verilog例化将在未来的数字电路和系统级设计中发挥越来越重要的作用。