准备工作

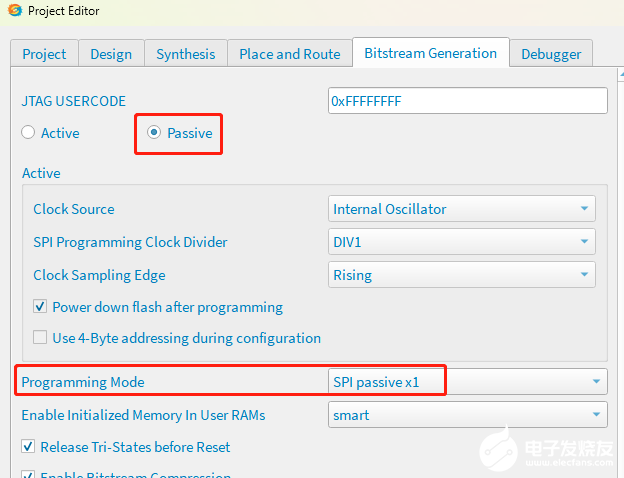

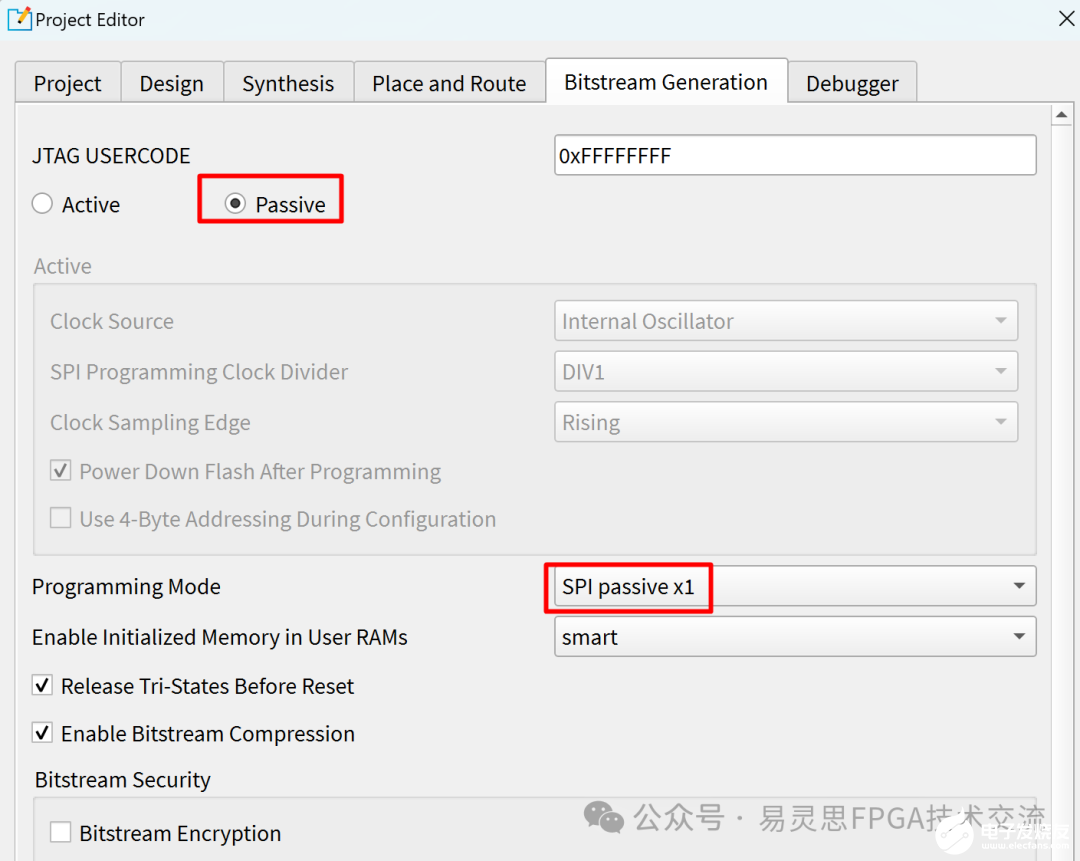

PS模式首先要把Bitstream Generation中的

(1)JTAG模式选择为Passive

(2)根据PS的位宽选择相应的Programming Mode.

(3)生成相应的下载文件。注意修改Bitstream生成模式时,不需要进行工程的全编译,只需运行最后一步数据流生成即可。

PS配置启动过程

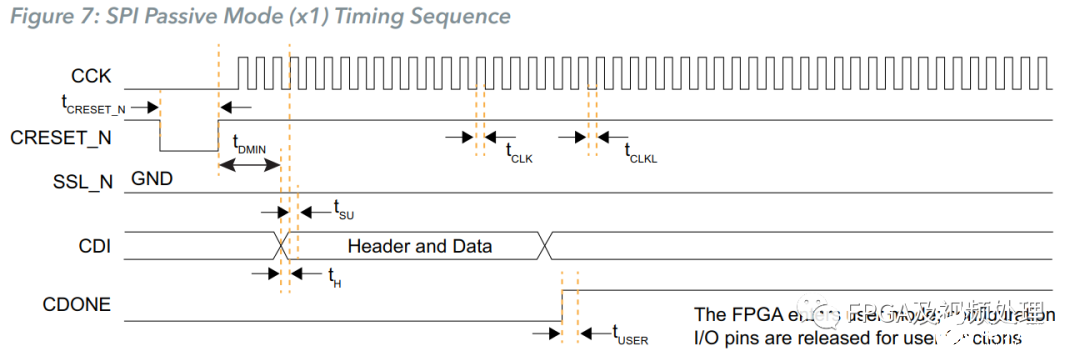

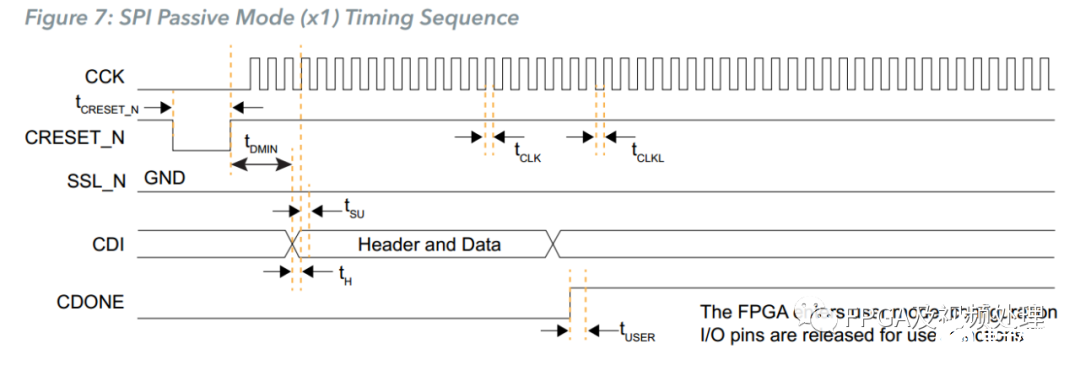

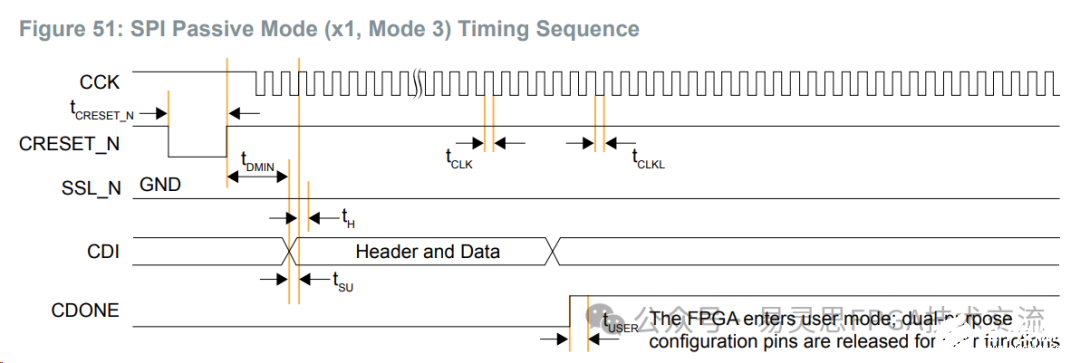

这里以X1模式为例,PS的配置过程如下:

(1)在启动配置之前要先把CRESET_N拉低tCRESET_N,然后拉高;

(2)在CRESET_N拉高之后,要等待tDMIN,才可以发送同步码,这期间可以翻转CCK;下面就是同步码。

(3)发送同步码,数据与时钟为上升沿触发;要求外部处理器连续发送数据直到数据完成,发送每个字节中间要有等待时间;

(4)数据发送完成后,继续发送CCK时钟100周期,或者一边发送一边检测CDONE,直到CDONE为高。实际上也确实有客户因为没有拉时钟而启动不了的情况。

控制信号处理

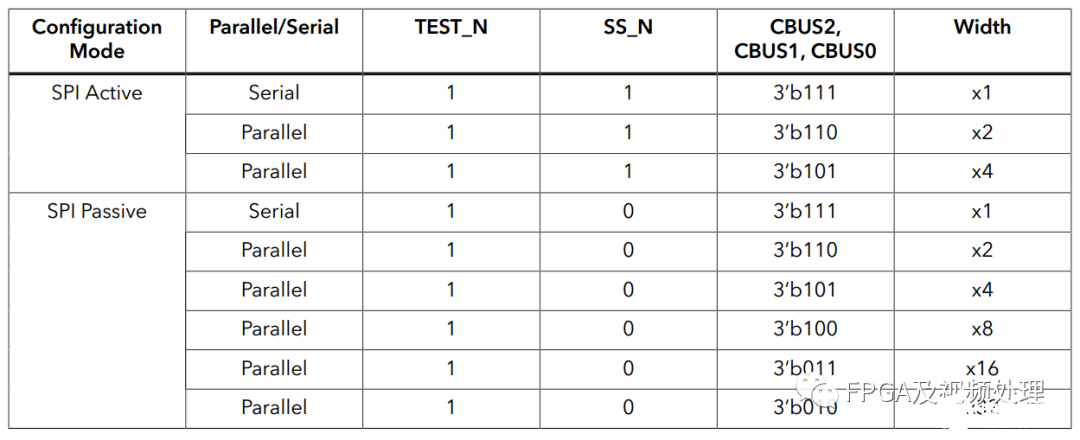

易灵思Trion FPGA的配置模块主要由CBUS[2:0]、SS_N和TEST_N,CSI几个信号控制。FPGA进入用户模式前不要对这几个信号进行翻转。

目前易灵思的Programmer工具只支持PS x1模式,所以如果实在找不配置失败的原因,可以通过逻辑分析仪来分析数据差异。x2和更高位宽需要通过外部微处理器,如MCU来操作。

这里需要注意的是在配置过程中,控制信号不要进行翻转,目前看到的现象是在多次配置过程中,在连续两次配置过程中,由于CSI翻转造成第二次配置失败。

应用案例

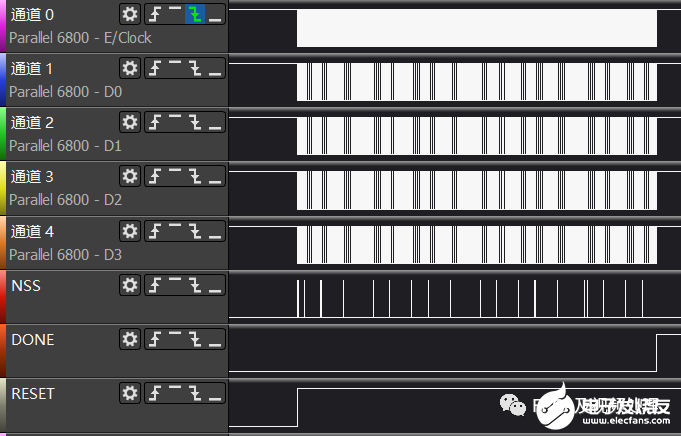

目前T20F169测试PS x4模式。时钟为30MHz,tCRESET_N拉低790ns,tDMIN为2us,数据配置完成后又继续发送时钟100个以上。可以启动。用时104ms

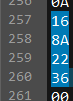

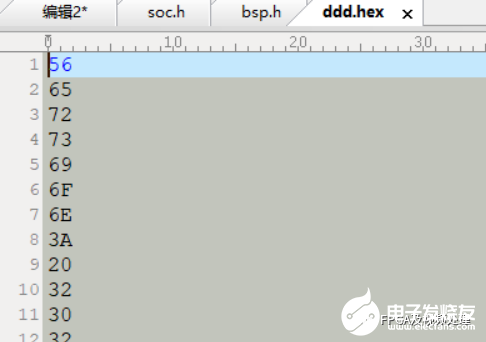

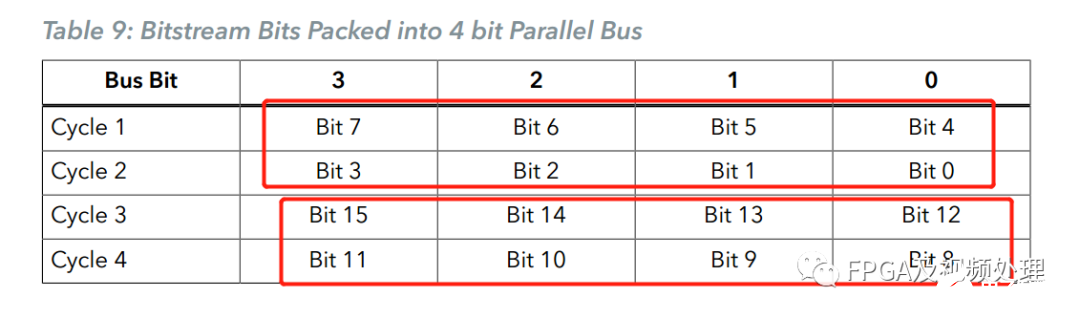

另外要提下数据顺序问题,实际在发送过程是依次发送的。且第个字节从高位先发送。

整体配置过程波形如下,SS_N有时会有很多毛刺,时钟之间也会有一些持续拉高的时间,但都不影响 。

在发送数据每个字节间要加点延时。

Ti180注意事项

上电要求SPI为Mode3模式,也就是CCK上电要为高。其余注意事项请参考相关文档。

如果经过以上的操作还不能正常进行ps的操作。我们还可以进行对比:

这里以Ti60F225为例:

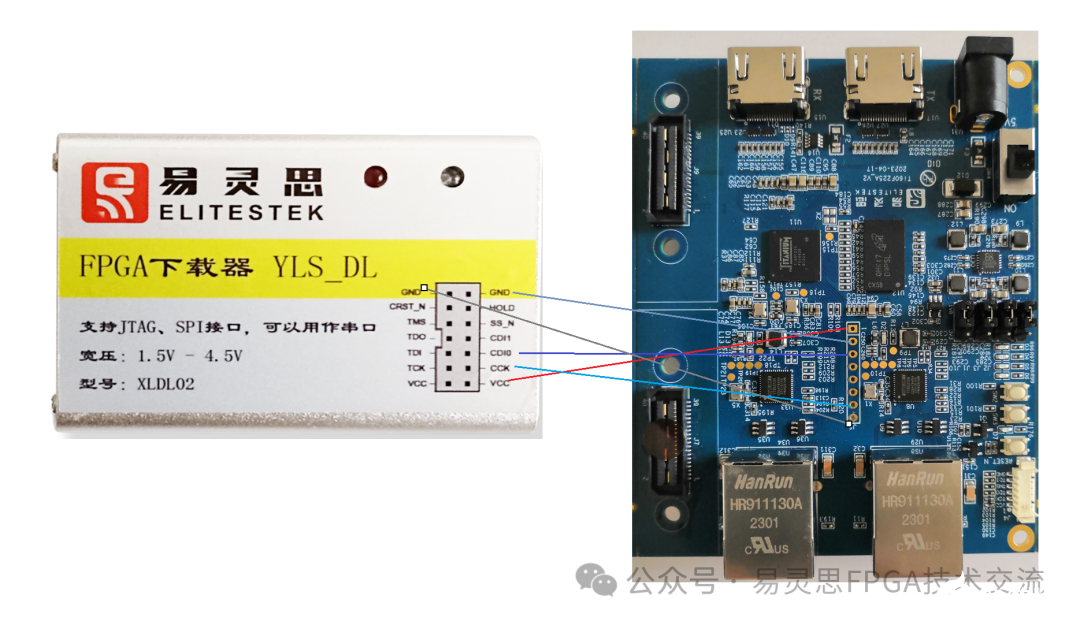

(1)硬件连接

Demo板预留了J6排针座。

| J6 | FPGA Pin Name | Pin Num. | Bank | Bank电压 |

| J6.1 | VCCIO1A | - | - | 1.8V |

| J6.2 | GPIOL_P_01_SSL_N | P1 | 1A | 1.8V |

| J6.3 | GPIOL_P_03_CDI0 | M1 | 1A | 1.8V |

| J6.4 | GPIOL_N_03_CDI1 | L1 | 1A | 1.8V |

| J6.5 | GPIOL_P_04_CDI2 | H5 | 1A | 1.8V |

| J6.6 | GPIOL_N_04_CDI3 | H4 | 1A | 1.8V |

| J6.7 | GPIOL_N_01_CCK | N1 | 1A | 1.8V |

| J6.8 | GND | - | - | - |

在上电之前,把demo板信号下下载器的对应信号连接

J6.1<->YLS.DL.VCC

J6.2<->YLS_DL.GND //SSL_N为低,复位释放后进入PS模式。

J6.3<->YLS_DL.CDI0

J6.7<->YLS_DL.CCK

J6.8<->YLS_DL.GND

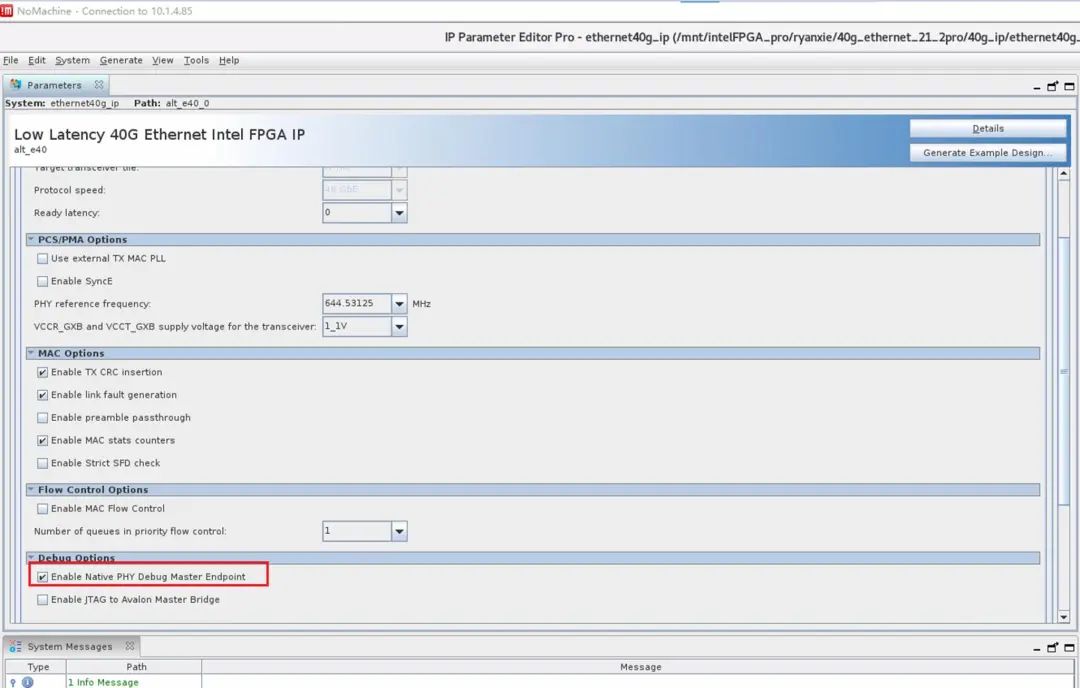

(2)生成PS数据流。在Project Editor->Bitstream Generation中把模块选择成Passive x1模式,重新生成数据流。

注意不需要全编译,只需要重新生成数据流即可。

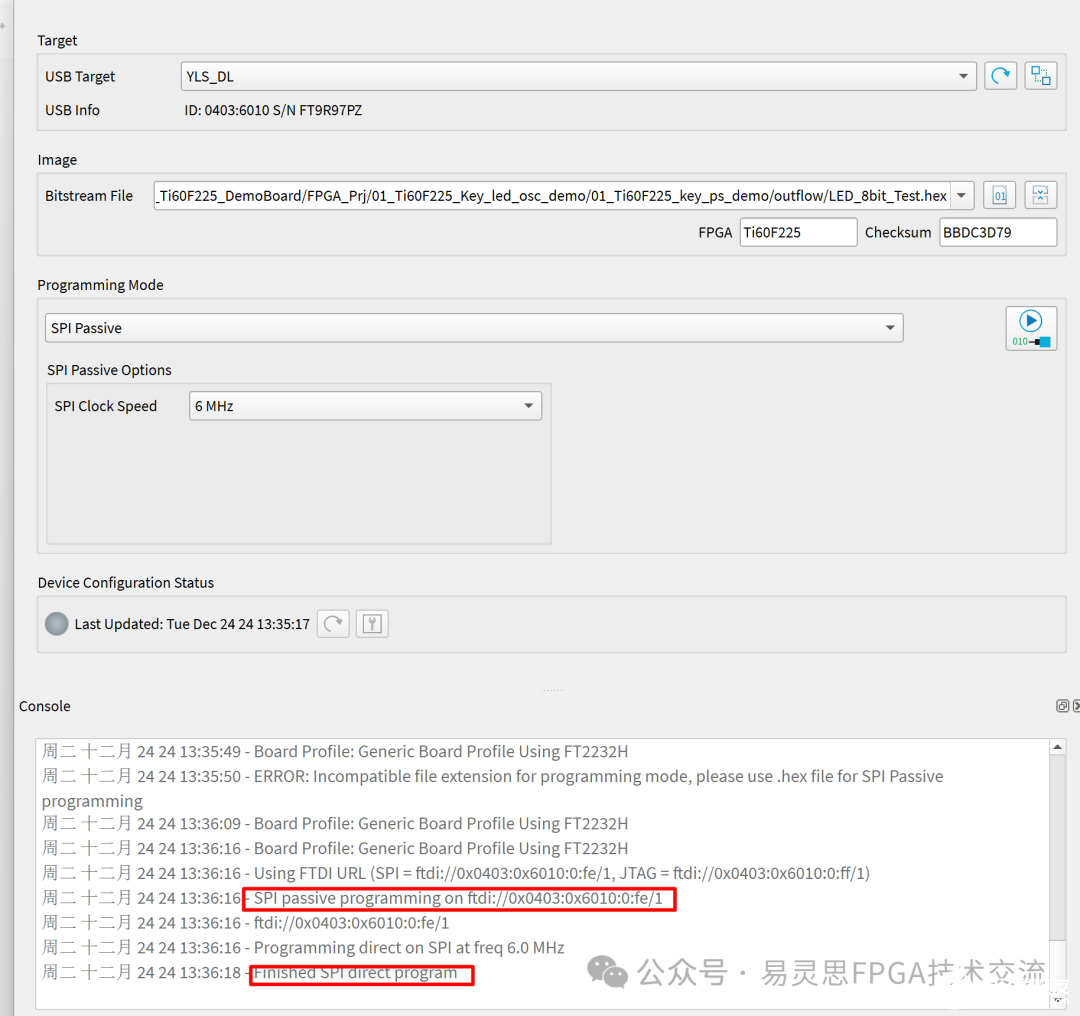

(3)配置程序。文件生成后,对demo板上电,然后在programmer中选择SPI Passive模式,下载即可。如果配置成功会有下面的提示。当然也可以查看程序的运行情况来确认。

审核编辑 黄宇