第一节 概述

时钟树的概念可以类比于人体的心脏和血液循环系统。就像心脏通过周期性的收缩将血液泵向身体各处一样,MCU的运行依赖于周期性的时钟脉冲来驱动。这些脉冲通常由外部晶体振荡器提供时钟输入,并最终转换为多个外部设备的周期性运作。这种时钟“能量”的传递路径类似于大树的养分由主干流向各个分支,因此被称为时钟树。

STM32内部也是由多种多样的电路模块组合在一起实现的。当一个电路越复杂,在达到正确的输出结果前,它可能因为延时会有一些短暂的中间状态,而这些中间状态有时会导致输出结果会有一个短暂的错误,这叫做电路中的“毛刺现象”,如果电路需要运行得足够快,那么这些错误状态会被其它电路作为输入采样,最终形成一系列的系统错误。为了解决这个问题,在单片机系统中,设计时以时序电路控制替代纯粹的组合电路,在每一级输出结果前对各个信号进行采样,从而使得电路中某些信号即使出现延时也可以保证各个信号的同步,可以避免电路中发生的“毛刺现象”,达到精确控制输出的效果。

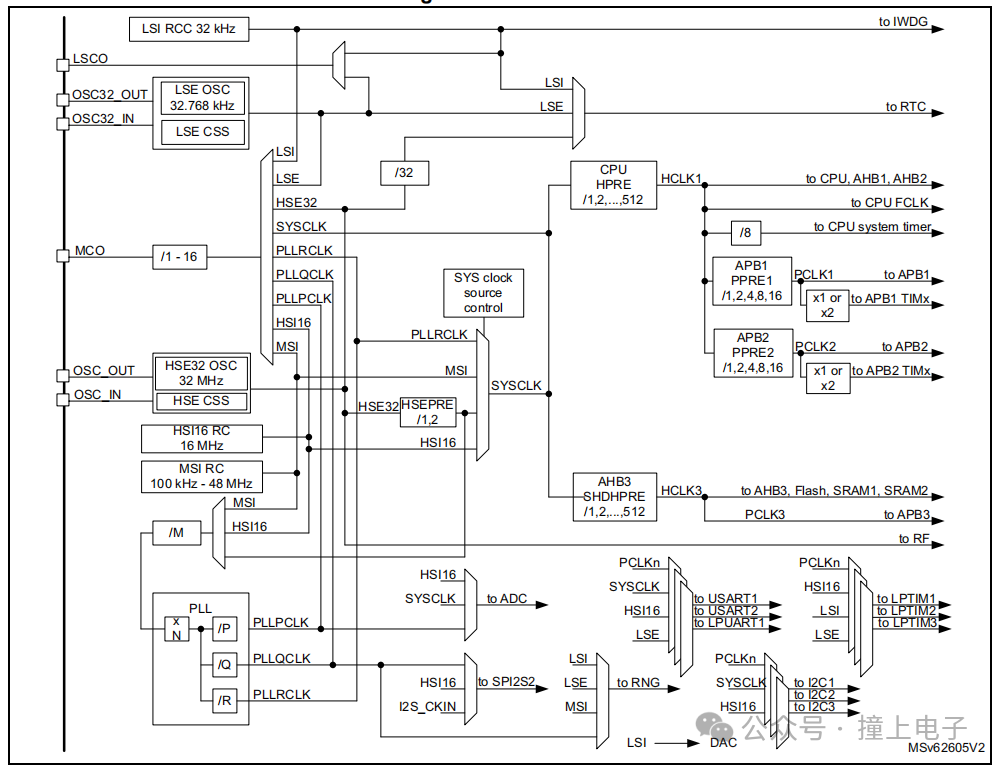

由于时序电路的重要性,因此在MCU设计时就设计了专门用于控制时序的电路,在芯片设计中称为时钟树设计。由此设计出来的时钟,可以精确控制我们的单片机系统。对于STM32WLE5,正常工作的主频可以达到48Mhz,但并不是所有外设都需要系统时钟这么高的频率,比如看门狗以及RTC只需要几十Khz的时钟即可。同一个电路,时钟越快功耗越大,同时抗电磁干扰能力也会越弱,所以对于较为复杂的MCU一般都是采取多时钟源的方法来解决这些问题。

STM32本身非常复杂,外设非常的多,为了保持低功耗工作,STM32的主控默认不开启这些外设功能。用户可以根据自己的需要决定STM32芯片要使用的功能,这个功能开关在STM32主控中也就是各个外设的时钟。

第二节 时钟源

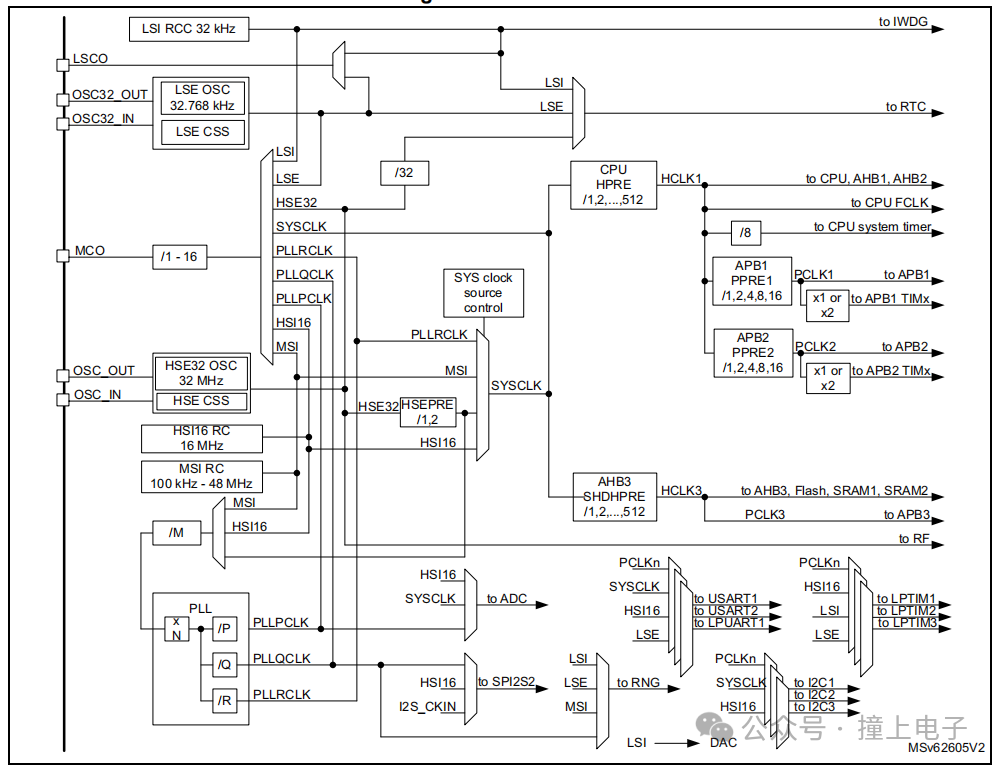

对于STM32,输入时钟源主要包括HSI,HSE,LSI,LSE。其中,从时钟频率来分可以分为高速时钟源和低速时钟源,其中HSI和HSE是高速时钟,LSI和LSE 是低速时钟。从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的方式获取时钟源,其中HSE和LSE是外部时钟源;其他是内部时钟源,芯片上电即可产生,不需要借助外部电路。两个外部时钟源建议使用外部晶振产生,这样的时钟精度高且稳定。

以下是各时钟源的说明:

1,高速外部振荡器HSE (High Speed External Clock signal):外接石英/陶瓷谐振器,频率为4MHz~32MHz。

2,低速外部振荡器LSE (Low Speed External Clock signal):外接32.768kHz石英晶体,主要作用于RTC和IWDG的时钟源。

3,高速内部振荡器HSI(High Speed Internal Clock signal):由内部RC振荡器产生,频率为16MHz。

4,低速内部振荡器LSI(Low Speed Internal Clock signal):由内部RC振荡器产生,频率为31~32kHz。

芯片上电时默认由内部的HSI时钟启动,如果进行了硬件和软件的配置,芯片才会根据配置调试尝试切换到对应的时钟源

第三节 锁相环

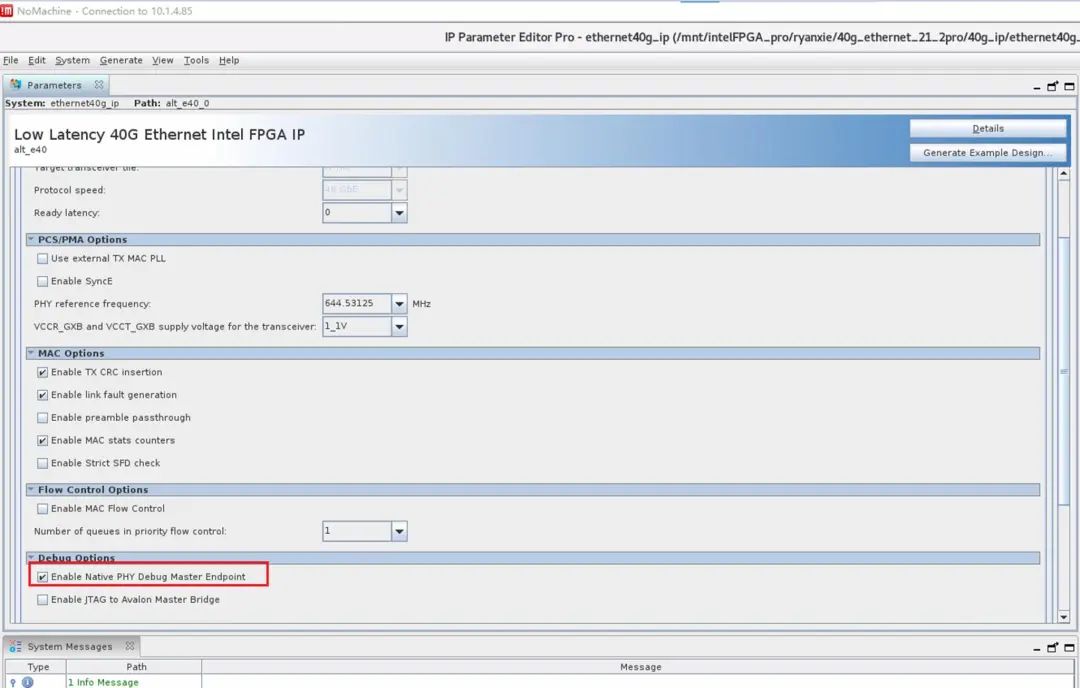

锁相环是自动控制系统中常用的一个反馈电路,在STM32主控中,锁相环的作用主要有两个部分:输入时钟净化和倍频。前者是利用锁相环电路的反馈机制实现,后者我们用于使芯片在更高且频率稳定的时钟下工作。如图所示:

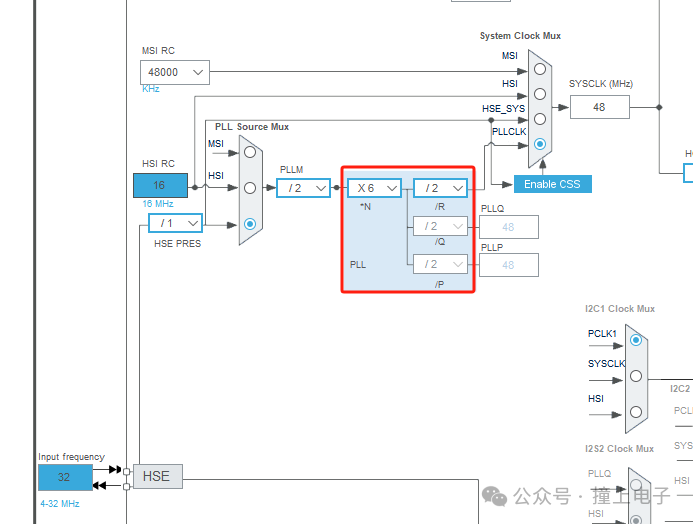

PLL时钟的时钟源要先经过一个分频系数为PLLM的分频器,然后经过倍频系数为N的倍频器出来之后的时候还需要经过一个分频系数为P或者Q或者R的分频器分频之后,最后才生成最终的主PLL时钟。

例如我们的外部晶振选择32MHz。同时我们设置相应的分频器PLLM=8,倍频器倍频系数N=6,分频器分频系数R=2,那么PLL输出高速时钟PLLP为:32MHZ/2*6/2,即48MHZ。

第四节 系统时钟

STM32的系统时钟SYSCLK为整个芯片提供了时序信号。讲解PLL作为系统时钟时,讲到了如何把主频通过PLL设置为48MHz。从时钟树图可知,AHB、APB1、APB2、内核时钟等时钟通过系统时钟分频得到。根据得到的这个系统时钟,下面我们结合外设来看一看各个外设时钟源:

可以看到,系统时钟输入源可选时钟信号有外部高速时钟HSE32、内部高速时钟HSI16、经过倍频的PLLCLK和MSI。这里选择PLLCLK作为系统时钟,此时系统时钟的频率为48MHz。之后变成APB1,APB2和APB3。

第五节 时钟输出

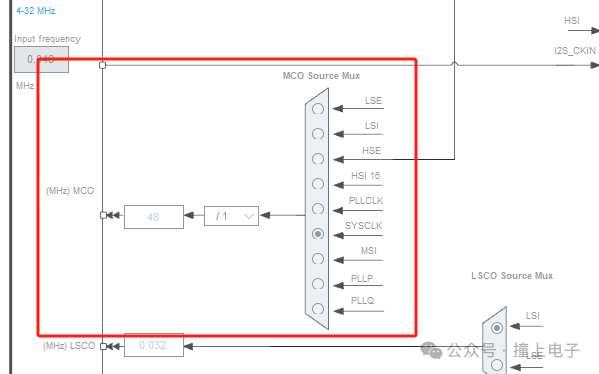

MCO时钟输出的作用是为外部器件提供时钟。STM32允许通过设置,通过MCO引脚输出一个稳定的时钟信号。

MCO时钟输出的时钟来源从上向下依次为:LSE,LSI,HSE,HSI,PLLCLK,SYSCLK,MSI,PLLP和PLLQ。