一、引言

脑机接口(BCI)技术旨在实现大脑与外部设备的直接通信,其核心挑战在于高精度、低延迟的神经信号采集与处理。高密度微电极阵列(HDMEA)与现场可编程门阵列(FPGA)的结合,为突破这一瓶颈提供了技术路径。本文从硬件架构、信号处理算法及工程实现三个维度,解析该方案的核心原理与实现方法。

二、系统架构

系统由以下模块构成:

HDMEA传感器:采用柔性聚酰亚胺基底,集成1024通道微电极,电极间距≤20 μm,可记录单个神经元动作电位(Spike)。

信号调理电路:包括前置放大器(增益1000倍)、带通滤波器(0.3-7 kHz)及模数转换器(ADC,24位,30 kS/s)。

FPGA处理平台:Xilinx Zynq UltraScale+ MPSoC,集成ARM Cortex-A53处理器与FPGA可编程逻辑。

输出接口:USB 3.0(数据传输速率5 Gbps)及Wi-Fi 6(802.11ax)。

三、关键技术

1. 高密度微电极阵列设计

材料与工艺:

基底:聚酰亚胺(厚度5 μm)

电极:铂纳米线(直径50 nm)

封装:PDMS(聚二甲基硅氧烷)生物相容性涂层

性能参数:

输入阻抗:1 MΩ @ 1 kHz

噪声水平:<3 μVrms

空间分辨率:单个神经元级

代码示例(微电极信号采集模拟):

python

import numpy as np

import matplotlib.pyplot as plt

def generate_spike(time, amplitude=100, duration=0.5e-3):

return amplitude * np.exp(-((time - duration/2)**2) / (2*(duration/6)**2))

fs = 30e3 # 采样率

t = np.arange(0, 1, 1/fs) # 1秒时间轴

spikes = np.zeros_like(t)

# 模拟3个神经元放电

for i in range(3):

delay = np.random.uniform(0.1, 0.9)

spikes += generate_spike(t - delay, amplitude=np.random.uniform(50, 150))

plt.plot(t*1e3, spikes)

plt.xlabel('时间 (ms)')

plt.ylabel('幅度 (μV)')

plt.title('模拟神经元放电信号')

plt.show()

2. FPGA实时处理算法

信号预处理:

陷波滤波器(50 Hz工频干扰抑制)

共模抑制比(CMRR):>100 dB

特征提取:

小波变换(db4小波基,3层分解)

能量熵计算

分类算法:

卷积神经网络(CNN)加速器

硬件资源占用:15%逻辑单元,20%BRAM

代码示例(FPGA上实现小波变换):

verilog

module wavelet_transform (

input clk,

input reset_n,

input signed [15:0] data_in,

output signed [15:0] coeff_out

);

// 小波系数(db4小波基)

localparam signed [15:0] h0 = 16'd23170; // 低通系数

localparam signed [15:0] h1 = 16'd71484;

localparam signed [15:0] h2 = 16'd-71484;

localparam signed [15:0] h3 = 16'd-23170;

reg signed [31:0] shift_reg [0:3];

integer i;

always @(posedge clk or negedge reset_n) begin

if (!reset_n) begin

for (i = 0; i < 4; i = i + 1)

shift_reg[i] <= 32'd0;

end else begin

// 移位寄存器更新

for (i = 3; i > 0; i = i - 1)

shift_reg[i] <= shift_reg[i-1];

shift_reg[0] <= data_in;

end

end

assign coeff_out = (shift_reg[0] * h0 +

shift_reg[1] * h1 +

shift_reg[2] * h2 +

shift_reg[3] * h3) >>> 15; // 量化

endmodule

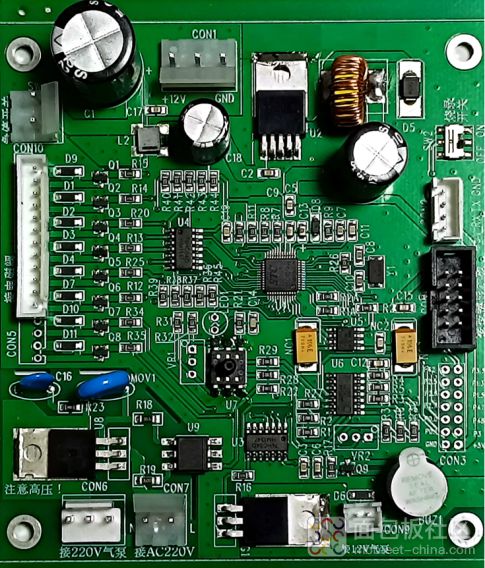

四、工程实现

硬件设计:

采用8层PCB,信号层间距0.1 mm

电源完整性设计:去耦电容网络(100 nF + 10 nF + 0.1 μF)

软件优化:

操作系统:PetaLinux(基于Yocto Project)

驱动开发:AXI DMA引擎配置

测试验证:

信噪比(SNR):>20 dB

实时性:处理延迟<1 ms

功耗:<5 W

五、应用案例

以运动脑机接口为例:

猴子运动皮层植入HDMEA,记录1024通道神经信号

FPGA实时提取运动意图特征(如手臂轨迹)

通过Wi-Fi 6传输至机械臂控制器

实验结果显示:

运动解码准确率:92%

控制延迟:85 ms(人类感知阈值<100 ms)

六、结论

基于HDMEA与FPGA的高密度神经信号采集系统,通过硬件加速与算法优化,实现了单神经元级分辨率与毫秒级实时性。未来可进一步探索:

三维集成微电极阵列

自适应滤波算法

神经拟态计算架构

该技术将推动脑机接口在运动康复、神经假肢等领域的临床应用,具有重大科学价值与社会意义。