我们在AMD FPGA和SoC中创建的设计实现了复杂的功能,例如电机控制,图像处理,机器学习或信号处理。

像任何行业帮助开发可编程逻辑应用程序一样,我们使用标准接口来实现重用和简化设计。在FPGA开发中最流行的接口是Arm可扩展接口(AXI),它为开发人员提供了一个完整的高性能,如果需要的话,还可以缓存相干存储器映射总线。

AXI是为管理者(事务的发起者)和下属(事务的响应者)之间的高速突发传输而设计的。AXI内存映射总线提供以下通道

•地址写—待写的地址数据,保护模式

•写通道-写数据突发

•写响应-完成数据爆发后的写状态

•Address Read -要读取的地址,保护模式

•读取通道-读取数据突发

虽然AXI通常在一个管理者和多个下属之间连接,但AXI是一个点对点协议。为了将单个经理连接到多个下属,我们需要使用实现交叉开关的AXI互连。

对于许多应用程序,使用了AXI的精简版本,它提供了称为AXI Lite的单节拍读写访问。

当您第一次接触FPGA设计时,使用AXI可能是一个挑战,并且我们通常使用处理器来配置AXI网络上的外设。

然而,通过UART从外部到FPGA访问AXI网络的能力对于板启动和使设备在最终开发中相互通信非常重要。

在Adiuvo,我们开发了一个简单的协议,可以从SPI, I2C或UART接口,并将实现对AXI网络的读写访问。我们开发的IP提供了进行突发传输的能力,但是对于这个应用程序,我们将研究如何在每个方向上进行AXI Lite传输。

这种方法非常有用,因为您可以非常简单地从外部访问AXI网络,并且在板启动期间确定寄存器设置等,这对软件可能很有用。它还可以在系统开发中实现从MCU到小型FPGA的简单接口。

这个概念

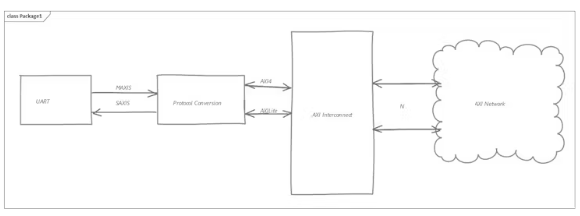

其实现背后的概念是模块化的,将通信接口与协议和AXI转换分离开来。通过这种方式,可以根据具体情况使用不同的通信模块。

在这种情况下,UART的通信接口将使用AXI流发送和接收信息。协议块将AXI流字节转换为AXI Lite命令,反之亦然。

然后,这个协议块可以连接到AXI互连,从而可以访问所有连接的AXI外围设备。

该协议

为了能够进行传输,我们需要有一个定义好的协议,该协议能够将大量字节转换为AXI读或写命令。

•写操作码- 1字节,值0x09

•读操作码- 1字节,值0x05

•地址- 4字节AXI交互的地址

•长度- 1字节,对于AXI Lite实现总是1

•有效载荷-要写的字或接收的数据,为AXI Lite读取或写入提供4字节

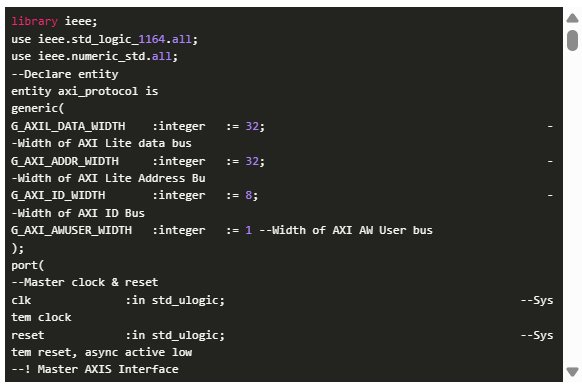

•要创建此解决方案,我们需要创建两个自定义IP块AXIS UART和协议块

The UART

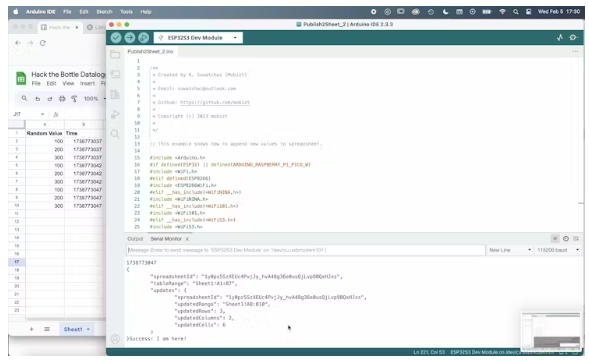

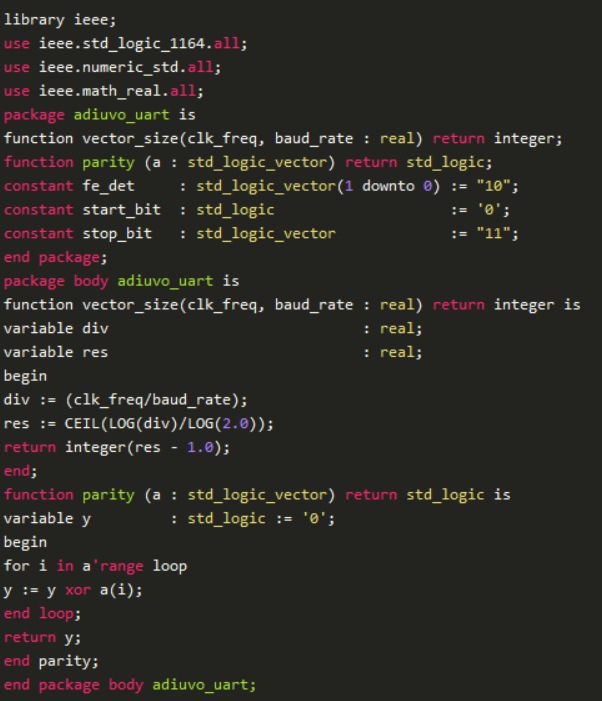

AXIS UART的代码如下-这个UART没有协议,需要2个停止位。

而所需的包裹是

AXIS协议

实现AXI协议的代码可以在下面看到——如果你像Adiuvo那样生产它,AXI状态机可以被写进一个过程来简化调用。

然后可以将这些模块集成到新的Vivado项目中。

Vivado项目

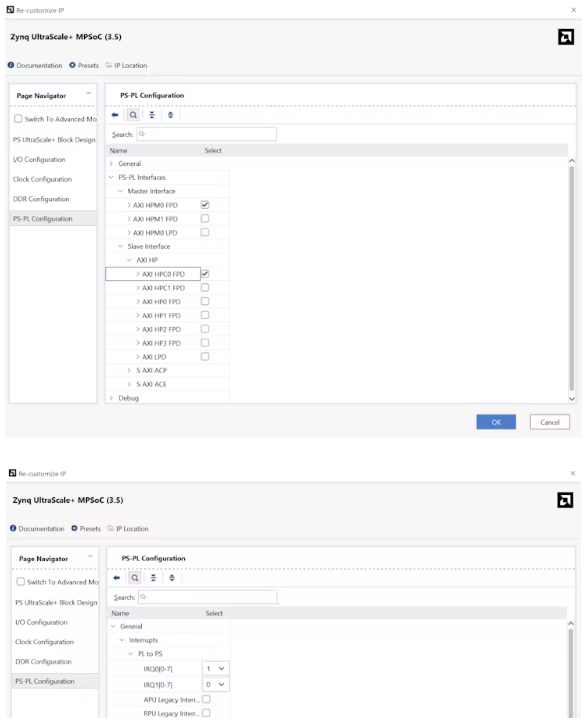

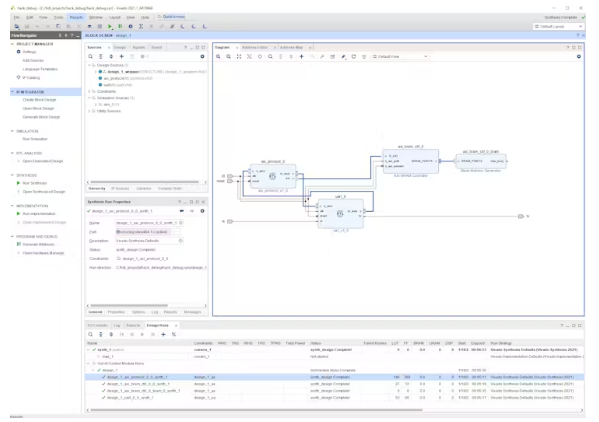

对于这个Vivado项目,我将针对连接到其IO载波卡的MicroZed板,尽管这种方法可以与任何AMD SoC或FPGA一起使用。

我们还可以将上述UART和Protocol的文件添加到项目中。

一旦项目开放,我们需要将UART和协议块添加到块设计中。

还添加了AXI BRAM控制器和BRAM,最终的图应该如下所示:

生成输出产品,我们就可以用cocotb来模拟设计了。

COCOTB模拟

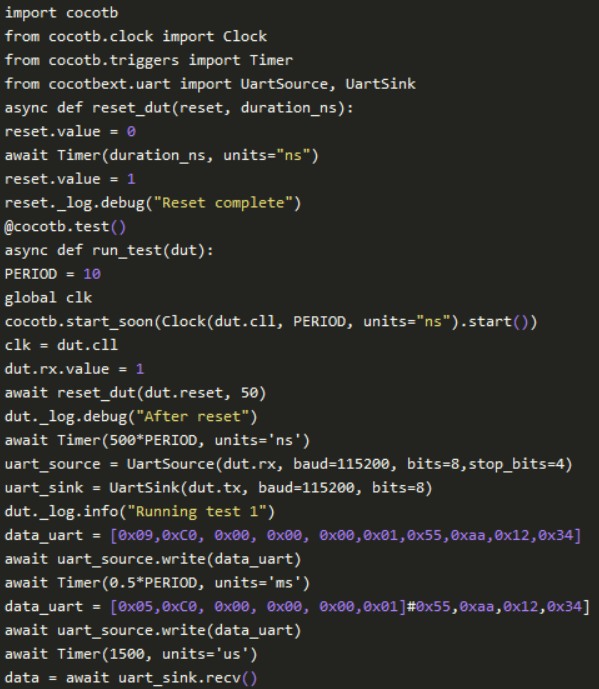

Cocotb允许我们使用Python模拟设计,如果您不确定如何设置Cocotb,请参阅我的博客

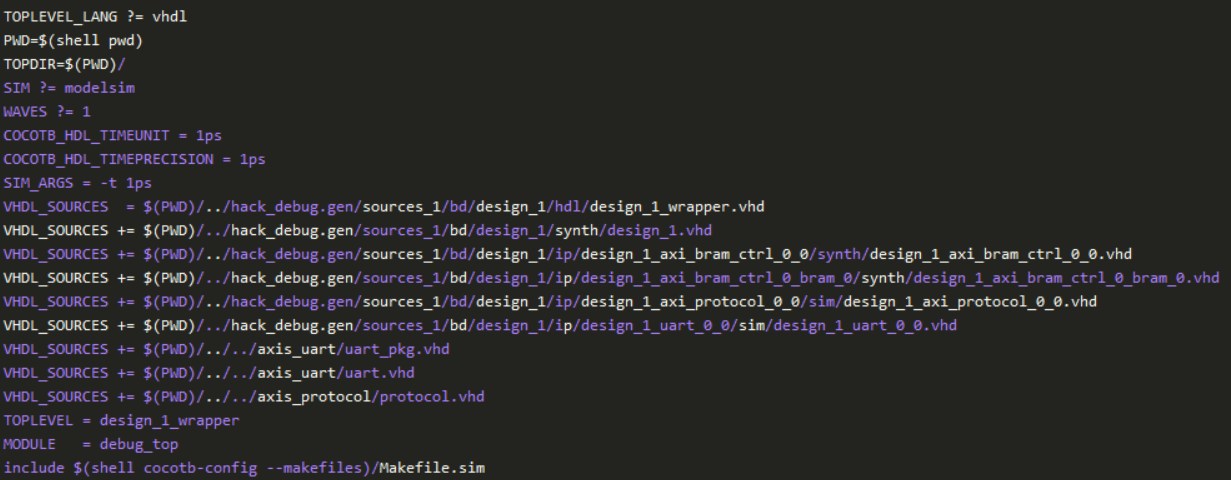

在cocotb中,我们需要一个python刺激文件和一个make文件,它可以拉入所有构建对象。

python刺激文件如下所示

当make文件看起来像-时,您需要将项目名称的路径更新到它们在系统中的位置

一旦模拟显示通过并报告通过UART编写的信息,我们就可以构建应用程序并在硬件上进行测试。

为了在硬件上构建它,我将处理器核心插入到块设计中,以启用PS时钟和复位。

更新后的框图如下所示

硬件测试

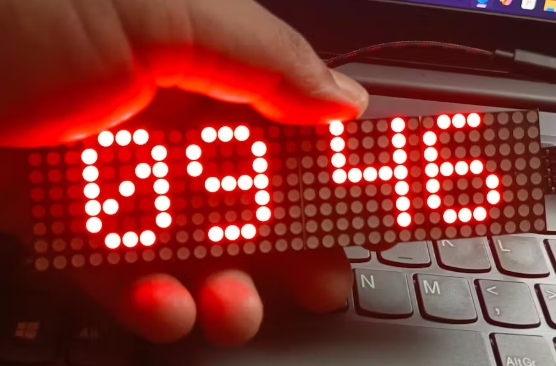

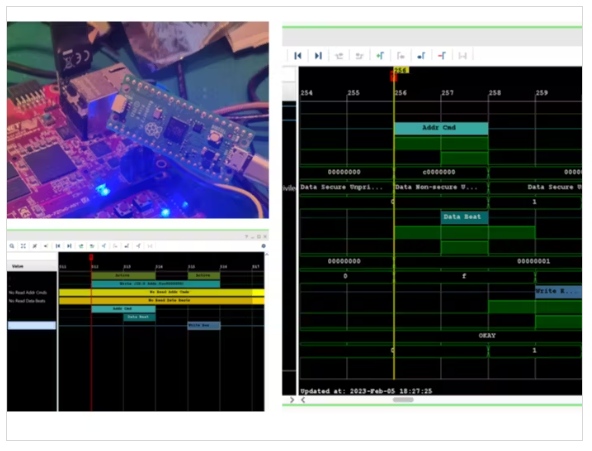

我们可以使用任何LOGIC LEVEL UART来测试设计,但是,我在办公室里有几个RPi PICO,它们可以制作出色的USB到UART转换器,并使我能够在PICO本身上编写应用程序。

为此,我将Pico上UART 0上的TX和RX引脚连接到FPGA RX和TX引脚。记住也要连接接地,这样它们就有一个共同的参考。

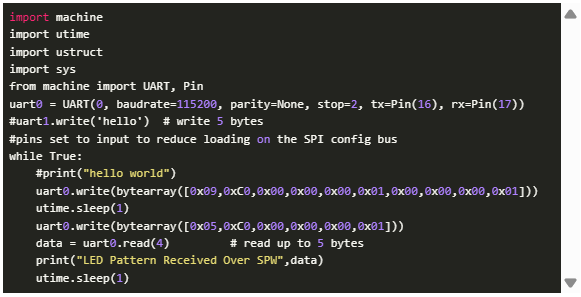

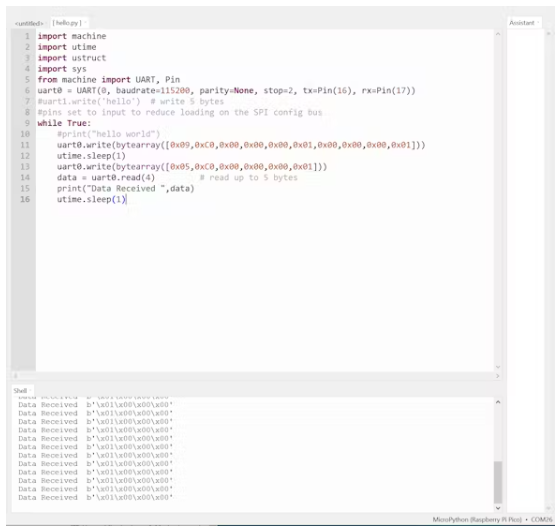

该应用程序是使用micro python在Pico上创建的

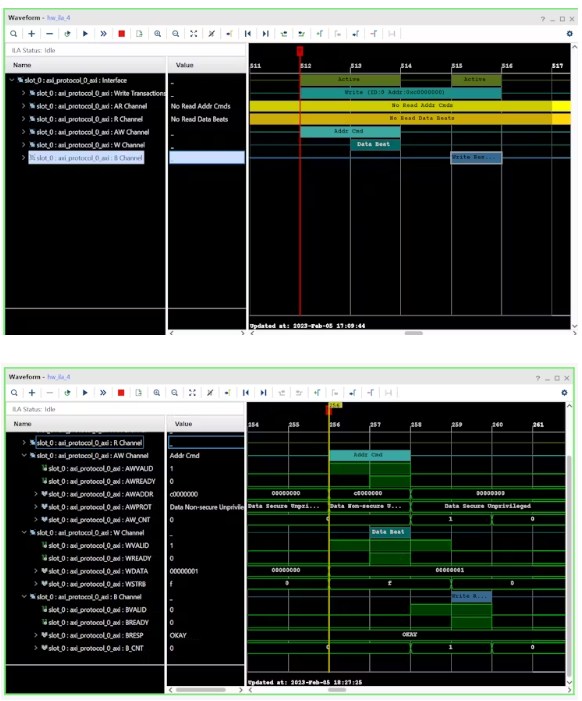

当运行我添加到调试设计中的System ILA时,我们可以清楚地看到协议块对AXI块RAM控制器执行的读写操作

我们可以看到数据在anthony中被读回

结论

我们可以使用一个简单的接口,如UART / SPI/ I2C来提供对AXI网络的访问。当调试设计或使小型FPGA连接到小型MCU时,这可以带来很大的好处。

本文编译自hackster.io