参考:UG892 UG835,Vivado集成开发工具为设计者提供了非工程模式下的FPGA设计流程。在Vivado非工程模式下,FPGA开发人员可以更加灵活地对设计过程的每个阶段进行控制,从而进一步提高FPGA的设计效率。

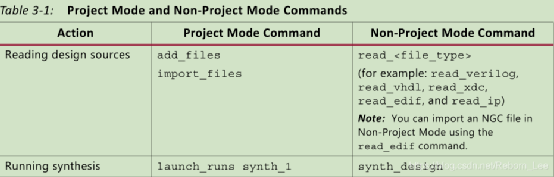

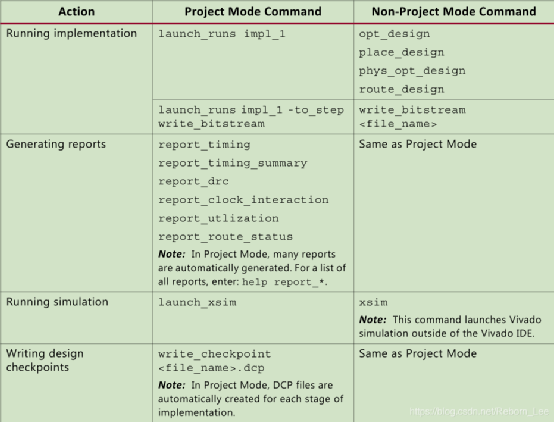

非工程模式下基本命令列表

典型TCL脚本

为了方便读者从整体上了解在Vivado非工程模式下的基本命令的功能,下面将给出用于Vivado设计套件示例的非工程模式TCL脚本,该脚本可以说明使用设计检查点、用于保存设计流程中各个阶段的数据库状态和手工生成各种报告的方法。

通过下面的命令运行该Tcl脚本文件:

vivado -mode tcl –source create_bft_batch.tcl,Vivado集成开发环境分析 3.1 启 动 Vivado集 成 开 发 环 境 当工作在非工程模式时,对于存储器中活动的设计来说,使用下面的命令打开/关闭Vivado集成开发环境。

(l)start_gui,打开Vivado集成开发环境,用于存储器中活动的设计。

(2)stop_gui,关闭Vivado集成开发环境,并且返回“Vivado Design Suite Tcl shell”界面。

在设计过程的每个阶段,设计者均可以打开Vivado集成开发环境,对存储器中保存的当前设计进行分析和操作。在非工程模式下,在Vivado集成开发环境中,一些工程的特性是不可用的,如Flow Navigator、Project Summary,以及源文件的访问、管理和运行。然而,通过Vivado集成开发环境的Tools菜单,可以使用分析及修改约束等很多特性。

需要知道的是,在Vivado集成开发环境中,对存储器中的设计所做的任何变化都会自动应用到下游工具中,这里没有保存的功能。如果设计者想要将约束的变化用于后续的运行,则在Vivado集成幵发的环境的主菜单下,执行菜单命令【File】—【Export】—【Export Constraints】,写到一个新的包含所有XDC文件的文件中。

3.2 打开设计检查点的方法 通过Vivado集成设计环境,设计者可以在保存的设计点上对设计进行分析。通过使用Tcl命令(synth_design、opt_design、power_opt_design、place_design、phys_opt_design和route_deSign),设计者可以在非工程模式下运行一个设计,并且可以在任何阶段保存一个设计。这样,就可以在Vivado集成设计环境中读取设计。设计者可以从一个布线后的设计开始,分析时序,仅通过布局来解决时序问题。然后保存刚才的工作,甚至设计中还没有进行的布线操作。Vivado集成设计环境显示打开设计点的名字。 设计者可以打开、分析和保存设计检查点,也可以将变化保存到新的设计点。

(1)在Vivado集成开发环境下,执行菜单命令【File】->【Save Checkpoint】,保存对当前设计检查点的修改。

(2)在Vivado集成开发环境下,执行菜单命令【File】—【Write Checkpoint】,将设计检查点的当前状态保存到一个新的设计检查点中。

关于具体的每个命令的使用下一节将细致分析。