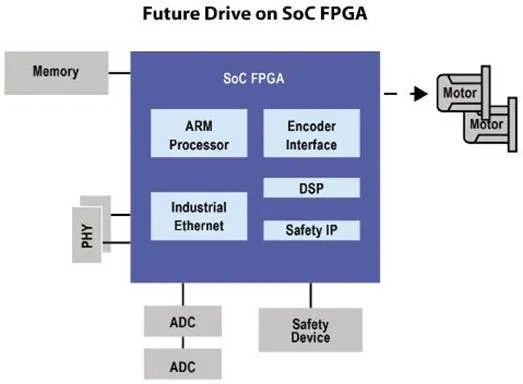

1 概述,HDL(VHSIC Hardware Description Language)是一种硬件描述语言,主要用于描述数字电路和系统的结构、行为和功能。它是一种用于硬件设计的标准化语言,能够帮助工程师们更好地描述和设计数字电路,并且广泛应用于FPGA和ASIC设计中。

在VHDL中,一个设计被描述为一个实体(entity),它包含了输入输出端口的描述。实体也包含了该设计的行为(behavior)的描述。 此外,VHDL还包括了标准库(standard library)和数学运算库(numeric package)等。

VHDL的基本语法包括关键字、标识符、注释、数据类型(如std_logic、integer等)、变量声明、信号声明、过程语句、并行操作符等。

以下是VHDL的一些基本特性和语法:

实体声明(Entity Declaration):实体(entity)是一个设计的接口和规范,描述了设计的输入和输出信号。在实体声明中,可以指定设计的接口和端口类型。

架构(Architecture):架构是实体的行为和功能描述。它包括了组件实例化、信号声明、过程语句等。在架构中,可以描述设计的逻辑和数据流动。

信号(Signal)和变量(Variable):在VHDL中,信号用于描述设计中的数据传输,而变量通常用于描述局部的数据存储。信号和变量的作用在于描述设计中的数据流动和数据处理。

过程(Process):过程描述了设计中的行为和逻辑。过程可以包括对信号和变量的操作、时序逻辑的描述等。

循环(Loop):VHDL中也包括了循环语句,用于描述设计中的重复操作。

总的来说,VHDL是一门强大的硬件描述语言,能够帮助工程师们进行数字电路的设计和描述。通过VHDL,工程师们可以更好地理解和描述设计的结构和行为,从而实现复杂的数字系统设计。虽然VHDL的语法可能对初学者来说有一定的复杂性,但一旦熟悉了其基本特性和语法,将会成为非常有用的工具。

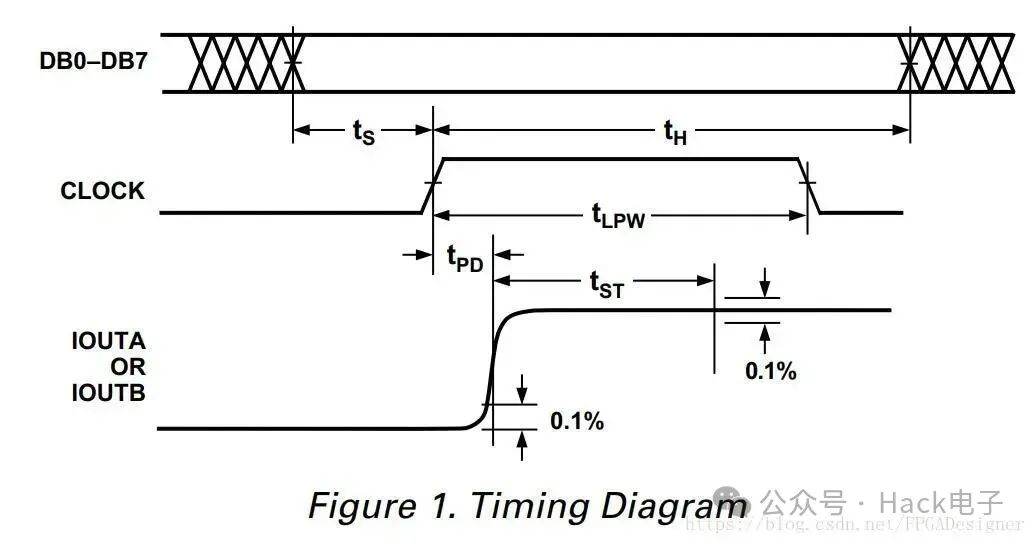

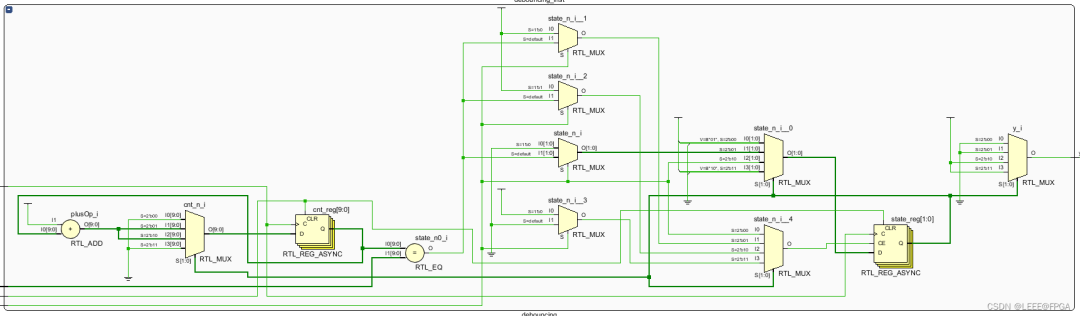

2 样例,按键消抖,设计文件>

按键消抖仿真文件>

3 常用编写,时序逻辑:

在 VHDL 中,时序逻辑指的是描述在特定时钟信号的边沿或状态变化下发生的操作。时序逻辑可以包括使用 rising_edge 或 falling_edge 函数来检测时钟信号的上升沿或下降沿,以及使用 wait for 语句来控制时序行为。下面是一个简单的示例,说明了时序逻辑的基本用法>

在这个例子中,我们定义了一个处理时钟信号 clk 的过程。使用 if rising_edge(clk) then 表示当检测到时钟信号的上升沿时执行操作。在这个逻辑块中,你可以更新寄存器、执行状态转移等与时钟相关的操作。这种时序逻辑的描述允许你根据特定时钟信号的变化来控制设计的行为。

时序逻辑在数字电路设计中非常重要,因为它能够确保设计在特定时钟信号的控制和同步下正确运行。通过使用时序逻辑,可以将设计的行为明确地与时钟信号进行关联,从而实现可靠的同步逻辑。

VHDL组合逻辑:

在 VHDL 中,组合逻辑是指在不涉及时钟信号的条件下,根据输入直接计算输出的逻辑部分。通常,组合逻辑描述了在给定输入条件下的输出行为,而且输出立即对输入进行响应,不依赖于时钟的边沿。以下是一个简单的示例,说明了组合逻辑的基本用法>

在这个例子中,我们创建了一个名为 Mux2x1 的实体,该实体具有三个输入端口 sel、a 和 b 以及一个输出端口 y。在 Behavioral 架构中的处理过程中,我们使用 if 语句来根据输入信号 sel 的值选择输出的值。这是一个典型的组合逻辑,因为输出 y 的值是仅仅依赖于当前输入信号的状态而计算出来的,不涉及时钟或者时序控制。

组合逻辑在数字电路设计中很常见,它描述了电路在给定输入下的输出行为,没有涉及时钟控制或时序逻辑。

case语句:

当需要根据输入的不同值采取不同的操作时,可以使用VHDL中的case语句。下面是一个简单的VHDL case语句的示例>

在这个例子中,我们在一个process中使用了case语句来根据输入的不同情况执行相应的操作。当输入信号input的值满足某个条件时,对应的输出output会被赋予相应的值。 “when others” 表示当输入值不满足前面列举的情况时执行的操作。

这个例子展示了VHDL中使用case语句进行条件判断和执行不同操作的方法。

状态机>

在 VHDL 中实现状态机(state machine)通常是通过组合逻辑和时序逻辑相结合的方式来完成的。状态机描述了一个系统在不同状态下的行为,通常会随着输入信号的变化而转换状态。下面是一个简单的示例,说明了一个基本的有限状态机在 VHDL 中的实现>

在这个例子中,我们创建了一个名为 SimpleFSM 的实体,该实体包括了时钟信号 clk、复位信号 reset、输入信号 input 和输出信号 output。状态机的行为由 state 和 next_state 信号来描述。在第一个 process 中,我们根据时钟信号和复位信号来更新 state 的值,以此来控制状态的转移。在第二个 process 中,我们根据当前的状态和输入信号来计算下一个状态 next_state。这个状态机描述了一个简单的输入序列检测过程,根据输入序列的不同,状态机将在不同的状态间转移。这是一个基本的有限状态机的例子,通过状态的转移来实现不同的行为。

时钟信号编写:

a)占空比为50%

b)非50%占空比

c)差分端口占空比为50%

延时>

循环:

a) loop语句

b) for语句

c)while语句

推荐

-

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

TrendForce集邦咨询: 预估2025年笔电品牌出货成长率将下修至1.4%

2025-05-01

-

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

让英特尔再次伟大,新CEO推动18A提前量产,14A已在路上

2025-05-01

-

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

晶振在网通应用增光添彩:中国移动实现数字乡村大升级

2025-05-01

-

一文解析电磁场与电磁波的区别

一文解析电磁场与电磁波的区别

2025-05-01

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

详解CPU 的大小端模式

详解CPU 的大小端模式

2025-05-01

-

超详细解析!电阻在电路中的作用

超详细解析!电阻在电路中的作用

2025-05-01

最近更新

-

洲明科技再登“中国最具价值品牌500强”

洲明科技再登“中国最具价值品牌500强”

2025-05-21

-

帝奥微AMOLED显示屏电源管理芯片DIO53010简介

帝奥微AMOLED显示屏电源管理芯片DIO53010简介

2025-05-21

-

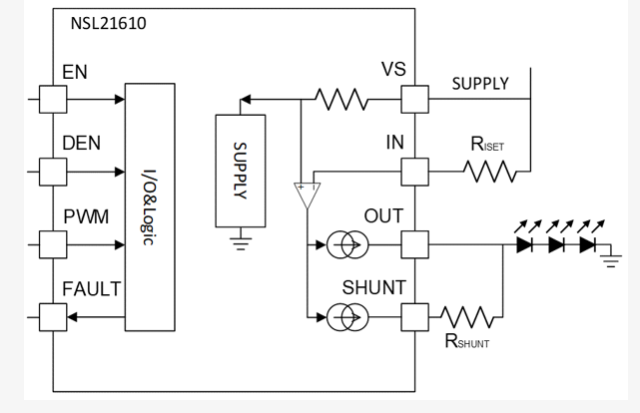

纳芯微LED线性恒流驱动NSL21610 汽车级40V/单通道具备散热加强功能

纳芯微LED线性恒流驱动NSL21610 汽车级40V/单通道具备散热加强功能

2025-05-21

-

极海半导体GALT61120汽车前灯LED矩阵控制芯片荣获AEIF 2025 金芯奖

极海半导体GALT61120汽车前灯LED矩阵控制芯片荣获AEIF 2025 金芯奖

2025-05-21

-

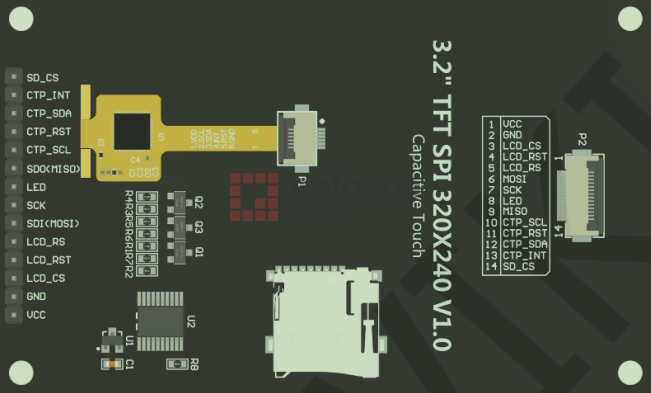

使用恩智浦FRDM LCD模组

使用恩智浦FRDM LCD模组

2025-05-21

-

【CW32模块使用】1.8寸彩色触摸屏

【CW32模块使用】1.8寸彩色触摸屏

2025-05-21

-

正方科技欧荷18S30AH智能电池在大载重无人机中的应用

正方科技欧荷18S30AH智能电池在大载重无人机中的应用

2025-05-21

-

广和通发布5G模组FG390系列

广和通发布5G模组FG390系列

2025-05-21

-

2025年OBC的新趋势:单级拓扑

2025年OBC的新趋势:单级拓扑

2025-05-21

-

谷歌I/O 2025大会前透露:Android 16接入Gemini,智能手机、XR设备升级

谷歌I/O 2025大会前透露:Android 16接入Gemini,智能手机、XR设备升级

2025-05-21