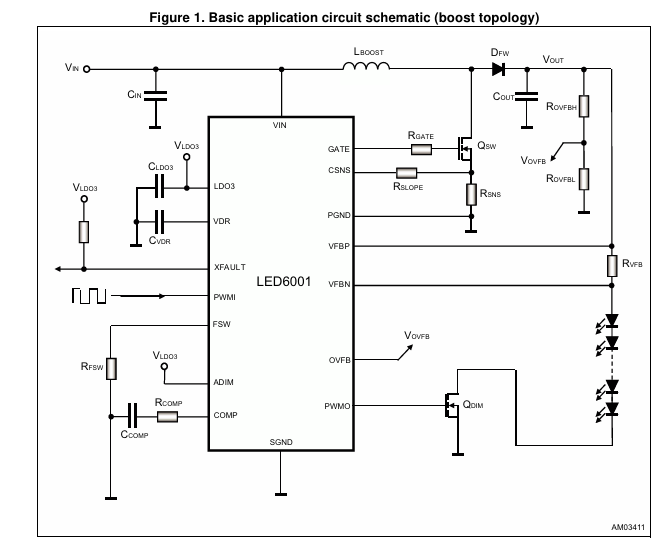

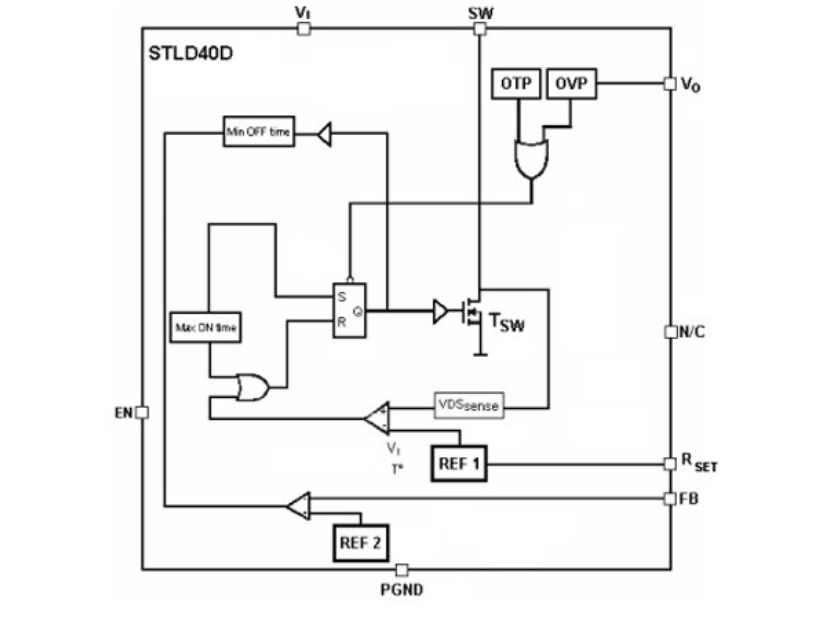

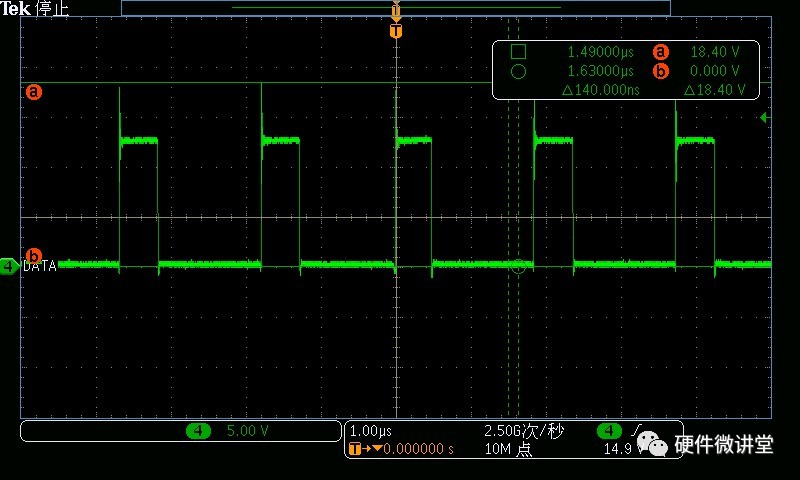

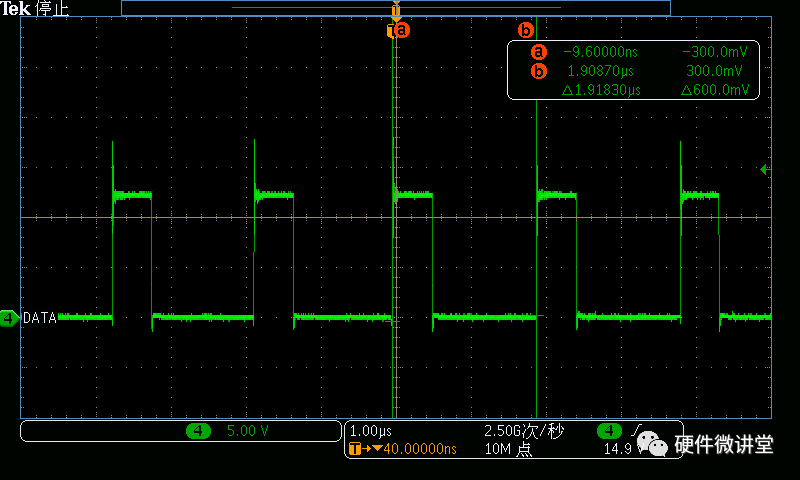

正好手上有一块电源板,一时兴起,点了下SW节点。如下图所示,振铃还是很明显的,最高达到18.4V。

注意:这里的SW振铃不是前面文章中提到的电源DCM模式下的SW振铃,而是上管MOS在导通瞬间的SW振铃。振铃所处位置不同,注意区分。

SW振铃有哪些危害?

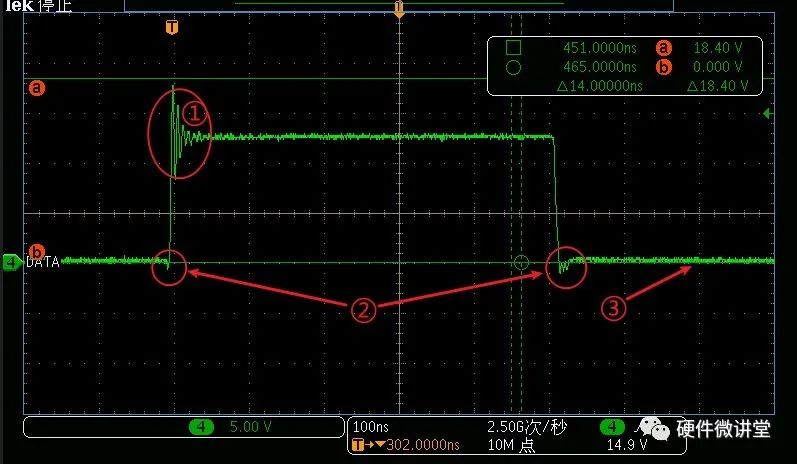

把SW波形适当放大,再看看。

如上图所示,这里面包含的信息还挺多的:

①是振铃;

②是死区时间;

③下管MOS管导通时的压降;

另外,②还可以反映出内置MOS管体二极管的导通压降。

如果要研究这个波形,可以展开讨论的东西太多,今天我们讨论下①。有同学不禁要问,都说振铃不好,那SW振铃有什么危害?

好问题!

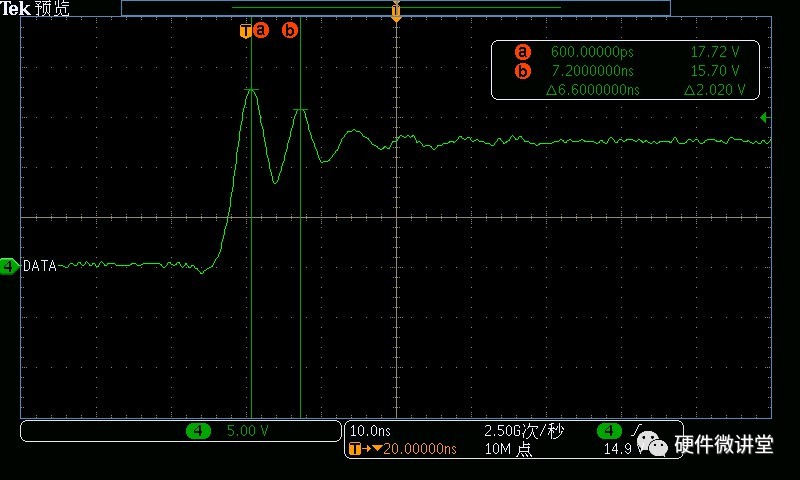

在回答这个问题前,我们不妨把振铃波形展开看一下。

(1)辐射EMI问题。如上图,这里振铃的第一个振荡波形的频率达到151MHz,而我们再看下这个Buck电路的开关频率才520kHz左右,如下图。很明显,振铃的频率远远高于开关频率。频率越高,通过等效天线辐射出去的概率越大,进而会带来EMI辐射问题。

(2)传导EMI问题。SW波形电压发生剧烈跳变,这里面包含很高的dV/dt,会产生高频共模噪声,可以通过寄生电容和参考地流过LISN,进而使得传导测试fail,带来EMI传导问题。

(3)开关管电气应力。从上面图中可以看出,在发生振铃时,SW电压波形最大可以达到18.4V。这无疑给MOS管造成了一定的电气应力。如果振铃电压超出了MOS的耐压值,那么很可能发生MOS源极和漏极击穿的情况。即便不超出要求范围,MOS管长期工作在电气应力下,对其可靠性和寿命也有一定的影响。

SW振铃如何产生?

SW振铃是如何产生的呢?

关于这个问题,网上说法很多。这里我只说下我个人的看法,上管MOS在导通瞬间,SW节点的电位瞬间发生阶跃变化。学过傅里叶变换的同学,这点应该很清楚,这其中蕴含着非常丰富的高频分量。而Buck电路中的寄生电感和寄生电容会形成LC谐振电路,通过其选频特性把高频分量中的特定频率选出来并进行若干倍的放大,再和其他分量进行叠加,表现出来就成为振铃波形。

SW振铃如何抑制?

如何抑制SW振铃?有同学可能会说:增加Snubber电路。

可是你有没有考虑过,为什么Snubber电路可以抑制SW振铃呢?内部逻辑是什么?

如果你不清楚Snubber电路的内部逻辑,你可以继续往下看。如果你已知晓,也可以看下理解是否一致。

在文章开头给出的第5篇《RLC串联谐振的概念,并通过引入恰当阻值的R来扭转系统的阻尼状态,使得整个系统尽快进入临界阻尼和过阻尼状态,并搭建模型进行了一系列仿真。今天我们还用TINA-TI分析下Snubber电路如何抑制SW振铃的。

必要说明:增加Snubber电路只是抑制SW振铃的一种方式,并不是唯一方式。而且这里也只是“抑制”,并不是“消除”。多种方式,多管齐下,效果更优。其他还有什么手段呢?

①减小SW节点面积;

②降低SW开关频率;

③增加展频FSS;

④优化PCB板器件布局;

……上述手段,每一条都可以专门写一篇“小作文”。这里只是提一下,不做展开,感兴趣的同学自行研究内部逻辑。

搭建仿真模型

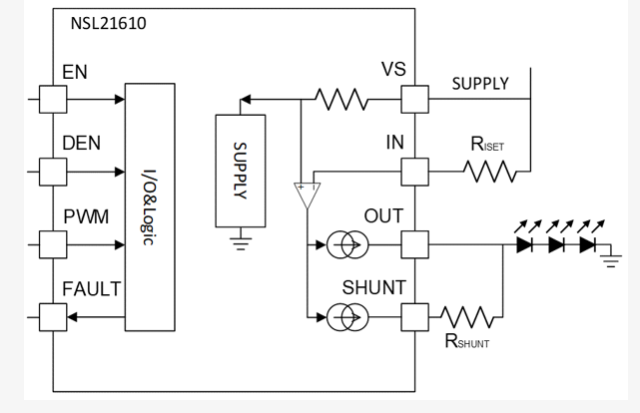

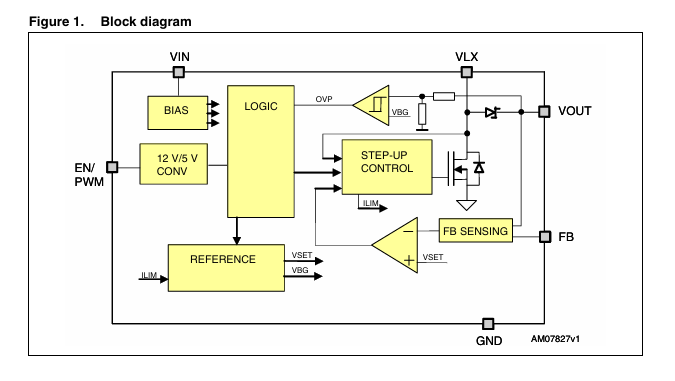

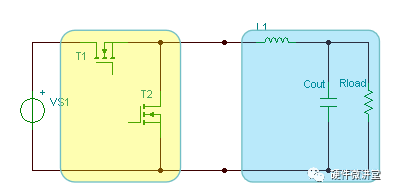

上图即为Buck电路模型,各位很熟悉了。为了更有利于分析SW振铃,我们需要对该电路模型进行简化。

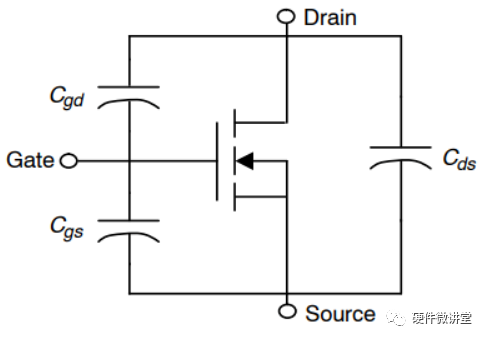

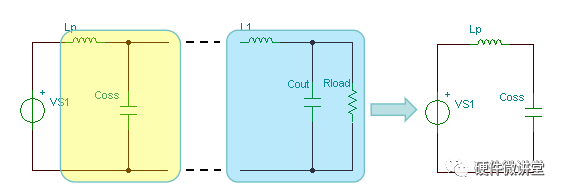

①黄色部分:SW是在上管MOS导通后出现振铃的,所以此时T1已导通,T2已关断。那我们可以认为T1是短路状态,T2是开路状态。看过米勒效应系列文章的同学,应该清楚MOS管有输出电容Coss(=Cds+Cgd),在T1导通时Coss会被短路,在T2关断时Coss是需要考虑的,特别是在高频条件下。

②蓝色部分:由于MOS管的开关过程很短(ns级),而Buck电路中的储能电感L1取值相对较大(uH级)。在如此短的时间内,开关管完成开关动作,而电感L1上的电流根本来不及变化,因为电感上的电流不能突变。所以,我们可以认为电感L1没有参与振铃活动。

③寄生电感:器件会有杂散电感,PCB走线会有寄生电感,在高频条件下,这些已需要考虑。由于电感L1没有参与振铃,那么我们可以大胆认为电感L1和其右侧器件及PCB的寄生电感没有振铃活动。但是电感L1左侧部分的寄生电感和杂散电感参与了振铃,需要考虑,我们可以统一记作Lp。

基于上述分析,我们可以把Buck电路中有关SW振铃的模型做进一步简化,如下图。

简化后最终模型如上右图,这不就是妥妥的LC电路么?再配合阶跃的信号源,富含各种高频分量,这能不谐振么???

如果此时我们把Snubber电路的C1和R1去加上去,会怎么样?