一前言

在日益数字化的时代,电子设备的设计已成为现代生活中不可或缺的一部分。但随之而来的是电磁兼容性(EMC)问题的日益凸显。EMC设计准则的制定和遵循对于确保设备在各种环境中稳定运行并且不会干扰其他设备至关重要。在本文中,我们将探讨一系列关键的EMC设计准则,帮助工程师们更好地理解并应用这些准则,以提高其设计的可靠性和稳定性。

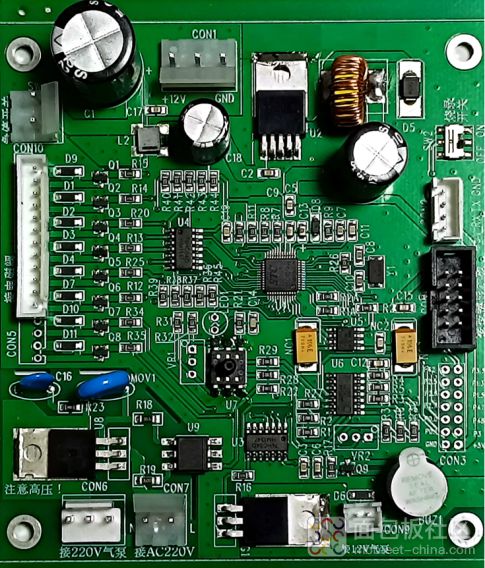

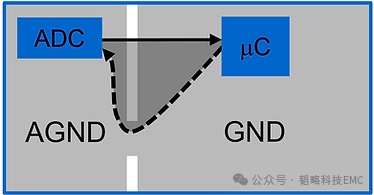

二EMC准则 #1—保持参考平面的完整性,避免切割

在设计电路板时,务必确保保持返回信号参考平面(如GND、电源平面)的完整性,避免与信号路径进行切割。这样的切割可能导致不必要的大电流环路,因为电流无法直接在正向电流下方流动,从而可能引发高辐射发射值。参考平面的完整性对于EMC性能至关重要。下图展示了完整参考平面的电流回路(实线)和参考平面分割后的电流回路(虚线)。

三EMC准则 #2—注意电流返回路径

在PCB设计的画板阶段,始终要密切关注关键信号的电流返回路径。要尽量减少大电流电路和敏感电路的电流返回路径面积,以减少不必要的噪声耦合。此外,尽量减小高频信号正向和回流之间的环路面积可以有效减少EMI和EMS问题的发生。

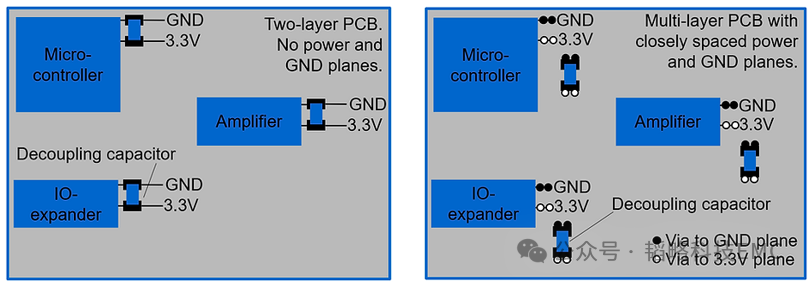

四EMC准则 #3——去耦电的寄生电感尽量小

去耦电容是设计中的关键因素之一。根据PCB的层数和堆叠方式,可以分为局部去耦(如下图左)和全局解耦(如下图右)两种情况。

去耦的好坏取决于PCB的层数和堆叠方式。

【双层和单层PCB】:对于单层或双层PCB设计,请将去耦电容尽可能靠近PCB每个芯片的每个电源引脚。

【多层PCB】:对于紧密相邻的GND和电源平面(<0.25mm,<10mils)的多层PCB设计,去耦电容的位置不像单层或双层设计那么关键,因为紧密相邻平面对高频(>1MHz)起到了有效的去耦作用。然而,比去耦电容的位置更重要的是减少过孔寄生电感,简单处理方式是多打过孔。

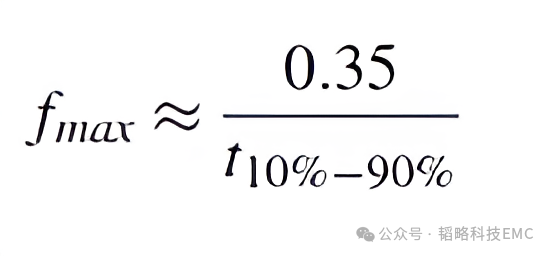

五EMC准则 #4—控制数字信号上升和下降时间

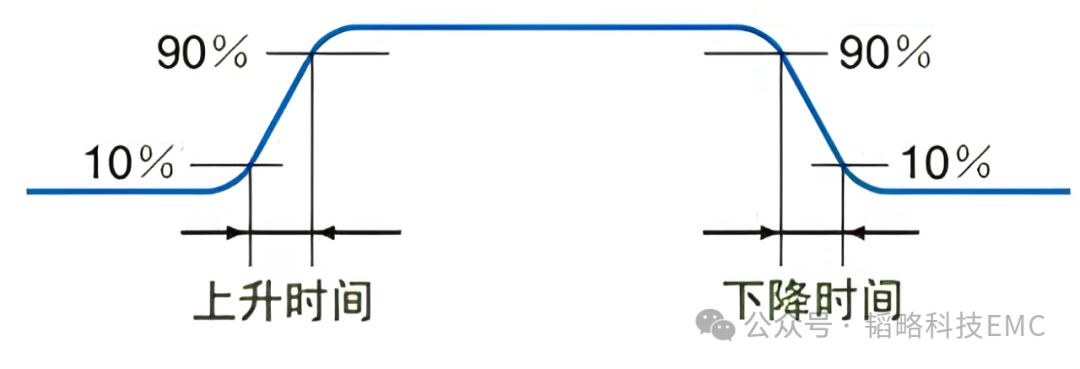

尽量增加数字信号(尤其是时钟信号)的上升和下降时间。较短的上升和下降时间意味着较大的信号带宽,因此在数字信号中可能产生更多的高频分量,这可能导致在传输线上产生辐射发射或反射问题。

【经验法则1】:在数字信号输出附近添加一个串联电阻(通常为33Ω)以减小上升和下降时间。

【经验法则2】:数字信号中的最高有效频率fmax [Hz]不取决于基频。而它取决于上升和下降时间: 其中,t10%-90% [秒] 是数字信号斜率从10%到90%的上升或下降时间。

【经验法则3】:长度超过λ/10 [米]的每个PCB走线都应被视为噪声有效的传输线。这意味着应该使用控制阻抗Z0 [Ω]设计这样的走线。换句话说:避免沿着PCB走线引起阻抗变化或不连续,因为这些变化或不连续可能导致反射或振铃。反射和振铃影响信号完整性,并导致电磁辐射增加。