概要:文章以T20F256为例,探讨了打开所有PLL及其输出时遇到的时钟分配问题。当两侧全局时钟网络(GCLK)超过8个时钟源时,将引发错误。特别是右侧PLL的输出由于时钟网络分配冲突,导致部分输出无法连接。此外,还提到了钛金系列器件的类似问题,并建议查看时钟网线说明。

在探索技术的深邃海洋中,让我们携手共赴一场激动人心的实验之旅,以T20F256为引领者,开启这趟未知的探索。

T20F256,不仅仅是一个简单的标识符,它代表着我们不断追求卓越、勇于创新的决心。在这个实验中,T20F256将以其独特的魅力,引领我们深入技术的核心,感受科技带来的无限可能。

我们期待着,通过这场实验,我们能够更加深入地了解T20F256的性能与特点,为未来的技术创新提供有力的支持。让我们共同期待,这场实验将带给我们怎样的惊喜与收获!

在追求卓越性能的道路上,我们勇敢地挑战极限,将T20F256的五个PLL(相位锁定环)全部激活,不仅如此,我们还进一步释放其潜力,将每个PLL的三路输出全部开启。然而,在向着更高峰攀登的过程中,我们遭遇了一个挑战:在生成约束时,系统报出了错误。但请放心,我们深知每一次的困难都是通往成功的必经之路,我们将以更加坚定的步伐,攻克这一难题,确保设备性能的完美展现。

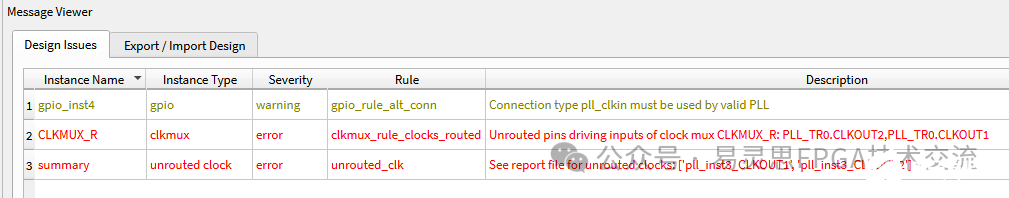

**时钟多路复用器muxCLKMUX_R的未路由引脚正在驱动关键时钟输入**

在深入探索我们的电路设计时,我们发现了一个至关重要的细节:`muxCLKMUX_R`时钟多路复用器的某些输入引脚尚未被正确路由。具体来说,`PLL_TR0.CLKOUT2`和`PLL_TR0.CLKOUT1`这两个时钟输出正在尝试驱动`muxCLKMUX_R`的输入,但目前它们并未得到有效的连接。

这种未路由的状态可能对我们的系统稳定性和性能产生不可预见的影响。时钟信号是任何数字系统的核心,它们如同心脏的跳动,驱动着数据的传输和处理。一旦时钟信号出现任何问题,整个系统都可能陷入混乱。

为了确保我们的系统能够稳定运行,我们必须立即解决这个未路由引脚的问题。我们将仔细检查电路图,确保所有的时钟信号都得到了正确的路由和处理。只有这样,我们才能确保我们的系统能够按照预期工作,为我们的用户提供卓越的性能和体验。

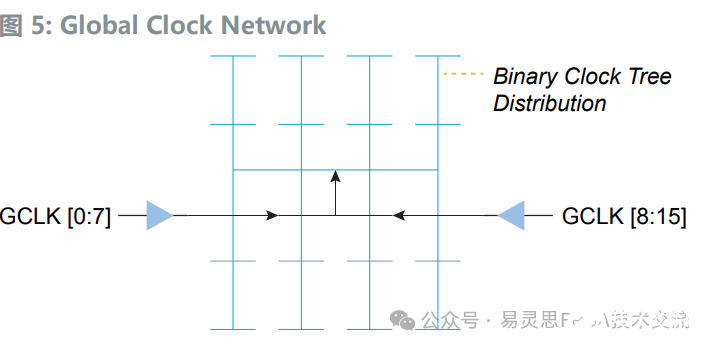

在T20的强大内核中,精心布局了16个高效运转的全局时钟网络GCLK,它们如同精确的计时器,确保每一个指令的执行都准确无误。巧妙地分布在芯片的左右两侧,各有8个这样的时钟网络,它们携手合作,共同编织出一个稳定而高效的时间网络。

无论是从全局时钟管脚输入的精准时间信号,还是PLL(相位锁定环)精心调整并输出的稳定时钟,都通过这些精心设计的CLKMUX(时钟复用器)网络,无缝地接入到全局时钟网络中。左侧的PLL(包括PLL_TL0和PLL_TL1)与左侧的CLKMUX_L紧密配合,而右侧的PLL(涵盖PLL_TR0, PLL_TR1和PLLBR0)则与右侧的CLKMUX_R携手前行。

这不仅仅是一个简单的时钟网络布局,更是T20对性能和稳定性不懈追求的体现。在每一个细节上,我们都力求完美,确保每一次的运算都能得到最精准的时间保障。T20,用科技的力量,诠释时间的价值。

在追求系统性能的道路上,有时我们会遇到一些意想不到的障碍。尤其是在布局精密的全局时钟网络时,若不慎超出了系统所能承受的极限,便会触发警报。具体而言,当两侧需要接入的时钟数量超过八个时,系统便会发出明确的报错信息,仿佛在提醒我们:“请注意,当前负载已超出预设范围。”这一警告,如同明亮的红灯,在复杂的工程道路上为我们指明了方向,让我们不得不重新审视和调整我们的设计策略。因此,在构建高效、稳定的系统时,我们必须时刻关注这些微妙的细节,确保每一步都走得稳健而有力。

深入探讨报错信息“Unrouted pins driving inputs of clock mux CLKMUX_R:PLL_TR0.CLKOUT2,PLL_TR0.CLKOUT1”的根源,让我们一同揭开这背后隐藏的谜团。

在电子设计和硬件配置的世界里,每一个细节都至关重要。面对上述报错信息,我们必须细心分析,找出问题所在,以确保系统的稳定运行。

首先,这个报错信息直接指出了问题的核心——某些未连接的引脚(Unrouted pins)正在驱动时钟复用器(clock mux)CLKMUX_R的两个输入端口,即PLL_TR0.CLKOUT2和PLL_TR0.CLKOUT1。这通常意味着在硬件设计或配置过程中存在某种不匹配或遗漏。

为了解决这个问题,我们需要回到设计原点,仔细检查与CLKMUX_R和PLL_TR0相关的所有连接和配置。我们需要确保所有的引脚都已正确连接,且时钟源的选择和配置符合设计要求。

此外,我们还需要考虑可能的外部因素,如硬件版本、芯片型号或电源供应等。这些因素都可能影响系统的正常运行,导致类似的报错信息出现。

通过逐一排查和验证,我们可以逐步缩小问题的范围,最终找到并解决问题。这不仅是对我们专业技能的考验,更是对我们责任心和耐心的磨砺。让我们携手共进,揭开这个谜团的答案吧!

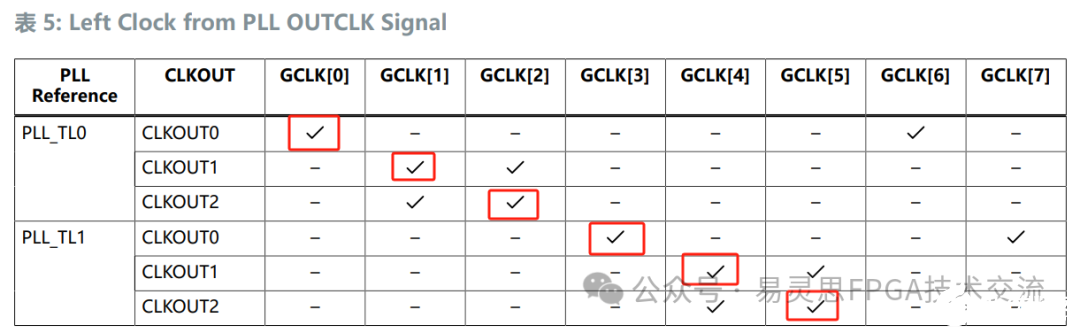

当我们逐一启动所有PLL及其输出时,让我们深入探索左侧CLKMUX_L的奥秘。您瞧,图中左侧整齐排列的GCLK,它们如同闪耀的星辰,编号为0至7,熠熠生辉。而我们的PLL_TL0和PLL_TL1,尽管只有六个时钟的陪伴,但它们却如同精准的指挥家,将每个时钟都赋予了独特的使命。

看,按照那醒目的红色标记,PLL_TL0.CLKOUT0引领着GCLK0前行;PLL_TL0.CLKOUT1则与GCLK1携手共进;紧接着,PLL_TL0.CLKOUT2与GCLK2并肩作战...如此这般,每个时钟都找到了属于它的GCLK伙伴,它们共同编织着一张精确无误的时间网络。

这样的设计,不仅展示了技术的精湛,更体现了对时间掌控的极致追求。每一步的精准配置,都是对完美的执着追求,让我们的系统更加稳定、可靠。

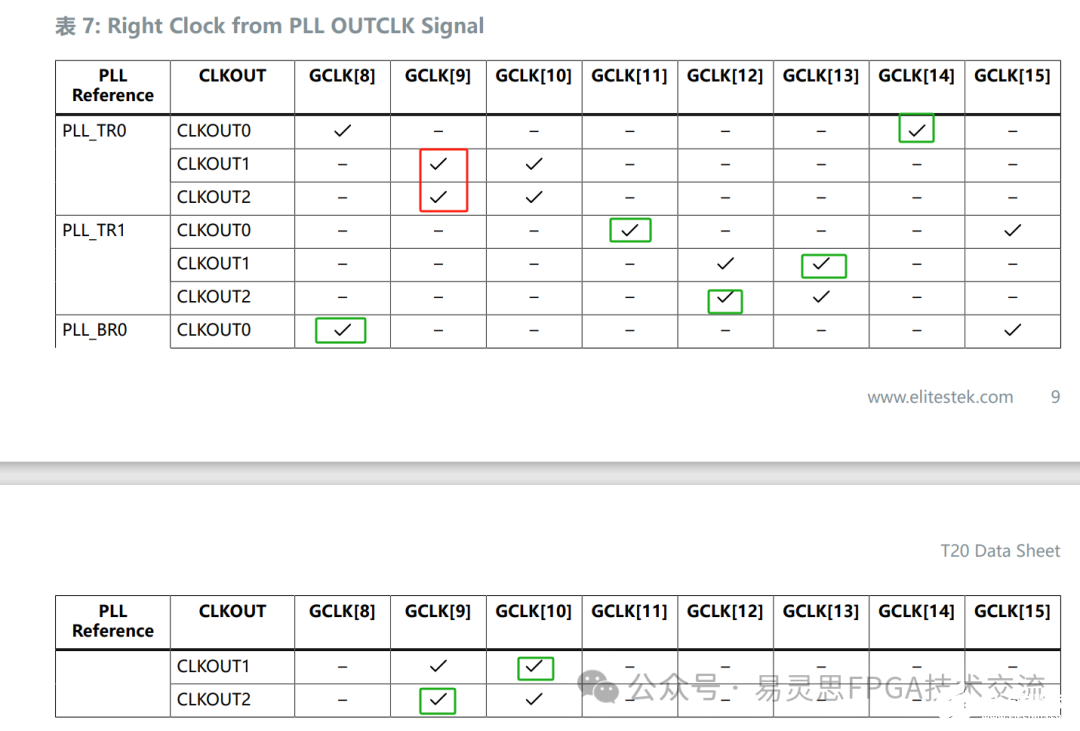

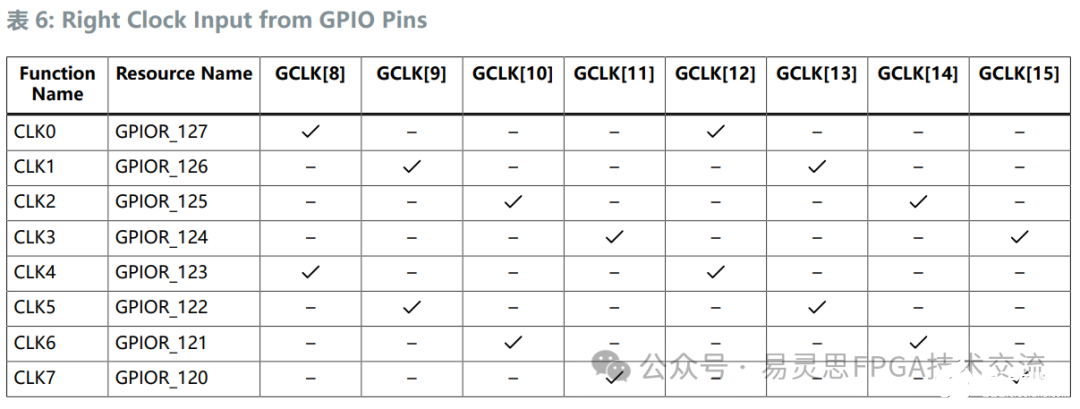

深入探究右侧CLKMUX_L的运作机制,我们先一同审视其使用情况。您瞧,那图上的左侧,GCLK的编号清晰呈现,从8一路延伸到15。而右侧,宛如璀璨的星辰,三个PLL——PLL_TR0、PLL_TR1和PLLBR0——各自闪耀着独特的光芒。

但当我们按绿色框的指引进行配置时,发现PLL_TR0的CLKOUT1和2仿佛迷失了方向,找不到与之相连的网络。尽管它们渴望与GCLK9和GCLK10建立连接,但遗憾的是,这两条网络早已被PLL_BR0的CLKOUT1和2占据,成为了它们的专属通道。

因此,当您尝试进行这样的配置时,系统便会智能地提醒您存在潜在的错误,就像一位贴心的向导,及时指出了前进道路上的障碍。让我们一同克服这些挑战,继续探索这美妙的电子世界吧!

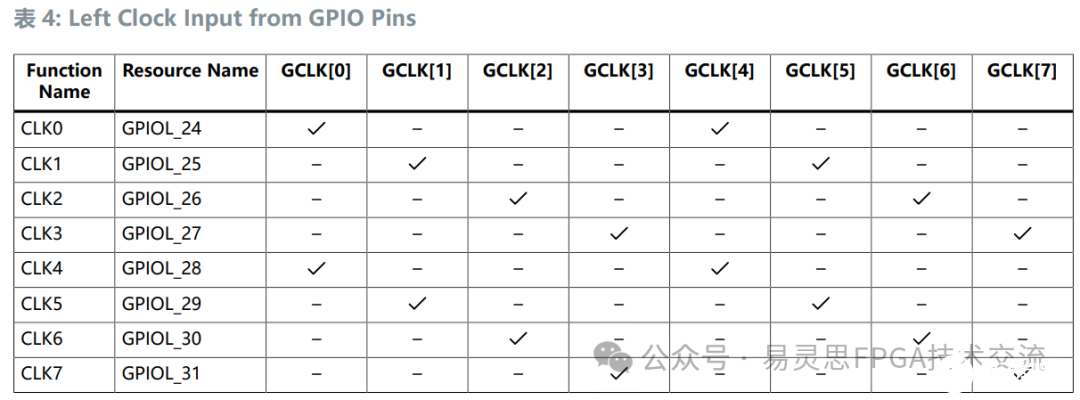

当深入探讨时钟配置时,或许您会心生疑问:为何GCLK15、GCLK6以及GCLK7这些时钟源似乎并未被提及?其实,这背后隐藏着时钟架构的深远奥秘。在此,我们主要聚焦于PLL(相位锁定环)的输出时钟,而尚未触及那些专用的时钟管脚。为了更直观地揭示这一切,请看下面的图示。它犹如一把钥匙,将引领我们解锁时钟世界的无限可能。

**探索钛金系列器件的奥秘:揭秘时钟网线背后的故事**

在科技飞速发展的今天,钛金系列器件凭借其卓越的性能和品质,赢得了众多用户的青睐。然而,就如同璀璨的星辰背后总有不为人知的奥秘,钛金系列器件在使用过程中,也面临着一些与众不同的问题。

今天,就让我们一起踏上这场探索之旅,深入了解时钟网线背后的故事。时钟网线,作为连接钛金系列器件的关键组件,其性能的稳定性和传输效率直接关系到整个系统的运行状况。

首先,让我们先仔细研读一下时钟网线的说明,揭开其神秘的面纱。你会发现,时钟网线不仅仅是数据传输的桥梁,更是整个系统稳定运行的关键所在。然而,就像所有高性能的器件一样,时钟网线也面临着一些挑战和问题。

但请放心,我们始终致力于为用户提供最优质的产品和服务。面对这些问题,我们已经有了成熟的解决方案和专业的技术支持团队。我们相信,在不久的将来,钛金系列器件将会更加完善,为用户带来更加卓越的使用体验。

现在,就让我们一起携手前行,共同探索钛金系列器件的无限可能!

【探索FPGA的无限可能:易灵思技术交流盛宴】

在这片技术的海洋中,易灵思FPGA技术交流如同一个璀璨的灯塔,指引着探索者们在电子设计的浩瀚宇宙中前行。这里,汇聚了众多热爱FPGA技术、渴望创新突破的专家学者和工程师们。他们在这里分享经验,交流思想,共同推动FPGA技术的发展与应用。

无论你是初入FPGA领域的新手,还是已经在这个领域深耕多年的老将,易灵思FPGA技术交流都是你不可或缺的精神家园。在这里,你可以找到最新的技术动态,了解最前沿的研究成果,更可以结识到志同道合的同行,共同为FPGA技术的发展贡献智慧和力量。

让我们一起,在易灵思FPGA技术交流的平台上,不断探索、创新、前行,共同书写FPGA技术的辉煌篇章!