概要:FPGA设计需优化测试与调试流程,包括明确测试需求、强化仿真验证、深入时序分析、多种调试手段、强化在板测试与评估。优化流程能提升FPGA设计可靠性,加速产品上市,降低开发成本。示例代码展示时钟约束优化,提高时序稳定性和可靠性。

在日益繁杂的电子系统设计世界中,现场可编程门阵列凭借其无与伦比的灵活性和可配置性,宛如一把瑞士军刀,成为了实现高性能、高可靠性系统的核心利器。然而,正如任何尖端技术都伴随挑战,FPGA设计的复杂性也带来了测试与调试的严峻考验。

但正是这些挑战,激发了我们追求卓越的渴望。优化测试和调试流程,不仅能让FPGA设计的可靠性更上一层楼,更是产品上市的加速器,开发成本的削减器。本文深入剖析了如何通过多维度、全方位地优化测试和调试流程,以强化FPGA设计的可靠性,并辅以实际示例代码,让您更加直观地理解并应用。

让我们一起探索这片未知的领域,用智慧和汗水书写FPGA设计的辉煌篇章!

一、精心策划,铸就卓越品质——深入解析测试需求与策略

在追求卓越品质的道路上,我们深知每一步都需精心策划、深思熟虑。特别是在当前这个信息化高速发展的时代,明确测试需求与策略更是至关重要的一环。我们不仅要对产品的每一个细节都了如指掌,更要深入挖掘其潜在的问题,确保在推向市场之前,我们的产品能够经受住各种严苛的考验。

测试,不仅是对产品功能的验证,更是对其性能、稳定性、安全性等多方面的全面考量。我们拥有一支经验丰富、技术精湛的测试团队,他们始终坚守着对产品质量的承诺,用专业的知识和技能,为产品筑起一道道坚实的防线。

在明确测试需求与策略的过程中,我们注重与产品团队、开发团队的紧密沟通与协作。我们深知,只有深入理解产品的设计理念和目标用户群体,才能更好地把握测试的重点和方向。同时,我们也积极倾听开发团队的声音,共同解决在测试过程中遇到的问题和挑战。

让我们一起携手并进,以匠心铸就卓越品质,用专业铸就信赖与口碑。在明确测试需求与策略的道路上,我们将不断探索、不断进步,为我们的产品注入更多的活力与魅力!

在FPGA设计的初始阶段,精准地捕捉并定义测试需求,同时精心策划一套高效的测试策略,是确保设计成功的关键所在。我们的测试需求不仅局限于单一的功能验证,而是涵盖了从时序分析到功耗评估,再到接口兼容性的全方位考量,力求让每一个设计细节都经过严格的检验。

在制定测试策略时,我们深知不同应用场景下的性能要求千差万别。因此,我们将灵活运用自动化测试工具,结合先进的分层测试方法,确保测试流程既高效又准确。通过这样的策略,我们能够迅速发现潜在的问题,并及时进行修正,让FPGA设计更加完善,更加符合实际应用的需求。

全新升级:功能仿真与验证的极致优化

在当前技术日新月异的背景下,我们深知功能仿真与验证的重要性。为此,我们进行了全面而深入的优化,确保每一个细节都达到极致的完美。这一升级不仅是对技术的挑战,更是对品质的不懈追求。

在功能仿真方面,我们引入了先进的算法和模型,使仿真结果更加准确、可靠。同时,我们加强了仿真环境的真实性和复杂性,以更好地模拟实际工作情况,为用户提供更加贴近真实需求的解决方案。

在验证环节,我们采用了多重验证机制和严格的质量标准,确保每一个功能和细节都经过严格测试和验证。这种全面的验证流程不仅提高了产品的稳定性和可靠性,也为用户提供了更加安心、放心的使用体验。

我们深知,只有不断追求技术的卓越和品质的完美,才能在激烈的市场竞争中立于不败之地。因此,我们将继续致力于功能仿真与验证的优化升级,为用户提供更加优质、高效的服务。

在FPGA设计之旅中,功能仿真如同指南针,引领我们探索并验证设计的每一个角落。这一过程模拟了设计在实际世界中的运行行为,不仅确保了设计的正确性,更为其可靠性筑起了坚固的堡垒。

为了打造更完善、更精确的测试流程,我们需将功能仿真的环节置于至关重要的地位。我们采用高精度的仿真模型,如同显微镜一般,洞察设计的每一个细节;同时,我们追求全面的场景覆盖,确保设计在各种情况下都能表现出色。

不仅如此,跨时钟域检查、边界条件测试等环节也是功能仿真中不可或缺的部分。它们如同守护者,时刻警惕着设计中可能存在的隐患,确保设计在投入实际运行前达到最佳状态。

让我们携手并进,以功能仿真为引领,打造更加可靠、更加精准的FPGA设计!

三、探寻时间脉络,精益求精——深入时序分析与优化

在时间的长河中,每一个微小的变化都可能引发巨大的波澜。为了捕捉这些变化,我们深入时序分析的世界,不断探索、优化,力求在时间的洪流中找到最佳的解决方案。

时序分析不仅仅是对数据的简单堆砌,更是对未来趋势的精准预测。我们利用先进的算法和模型,对数据进行深度剖析,挖掘出隐藏在数据背后的秘密。同时,我们不断优化分析流程,提高分析的准确性和效率,确保每一次决策都基于最可靠的数据支持。

在深入时序分析与优化的道路上,我们始终秉持着精益求精的精神,不断追求卓越。我们深知,只有不断地学习、实践和创新,才能在这个快速变化的时代中立于不败之地。因此,我们将继续前行,不断探寻时间脉络的奥秘,为未来的发展贡献我们的智慧和力量。

在FPGA设计的广阔天地中,时序问题犹如潜藏的暗礁,随时可能给项目的可靠性带来不可预知的挑战。为了确保设计能够破浪前行,我们必须对测试流程进行精细化的雕琢。在这其中,深入的时序分析与优化成为了不可或缺的利剑。

静态时序分析正是这把利剑上的锋利刃口,它犹如一位敏锐的侦探,细致入微地探索设计中的每一条时序路径。通过STA的审视,我们能够清晰地洞察设计中是否存在建立时间、保持时间等违规的蛛丝马迹。

一旦时序问题被揭示出来,我们绝不退缩。相反,我们将以无畏的勇气和精湛的技巧,通过调整时钟频率、优化逻辑布局布线等手段,一一攻克这些难题。我们的目标只有一个:确保FPGA设计在时序上无懈可击,为项目的可靠性保驾护航。

四、深度运用多元调试策略

在追求项目完美呈现的道路上,我们不仅仅满足于传统的调试手段。相反,我们积极探索并采用了多种先进的调试策略,以确保每一个细节都达到最优状态。这些调试手段包括但不限于系统级的性能测试、功能模块的逐一验证、以及用户界面的细致打磨。

我们深知,调试不仅仅是发现问题并修复的过程,更是对项目整体质量的一次全面检验。因此,我们严格遵循调试流程,确保每一步都经过精心的考虑和验证。无论是对于潜在的性能瓶颈,还是对于用户可能遇到的细微问题,我们都力求做到早发现、早解决。

通过深度运用这些多元调试策略,我们不仅提高了项目的整体质量,也为用户带来了更加流畅、稳定的体验。我们坚信,只有不断追求卓越,才能在竞争激烈的市场中立于不败之地。

在FPGA设计的关键调试阶段,我们巧妙融合多种调试策略,确保问题能够迅速且精准地被定位和解决。在这一过程中,嵌入式逻辑分析仪和外部逻辑分析仪两大得力助手功不可没。

嵌入式逻辑分析仪,犹如FPGA内部的智囊团,它充分利用FPGA的内部资源,通过JTAG接口施展其调试神技,尤其适用于大型且复杂的FPGA设计。它的存在,让调试工作变得得心应手,大大提高了工作效率。

而外部逻辑分析仪,则如同一个细致入微的侦探,它提供了更深层次的内存访问和更为灵活的触发功能。在需要精确分析信号定时关系的应用场景中,它总能凭借其独特的优势,为我们揭示信号背后的奥秘。

无论是嵌入式逻辑分析仪还是外部逻辑分析仪,它们都是我们FPGA调试过程中不可或缺的得力助手。在它们的帮助下,我们能够更加自信地面对FPGA设计的挑战,确保项目能够按时、高质量地完成。

五、深化在板测试与可靠性评估,确保产品无懈可击

在追求卓越品质的道路上,我们从未停歇。为了打造更可靠、更稳定的产品,我们特别强化了在板测试与可靠性评估环节。这一环节不仅是对产品性能的全面检验,更是对品质承诺的坚定守护。

我们深知,每一个细节都可能影响到产品的整体表现。因此,在板测试与可靠性评估过程中,我们严格把控每一个环节,确保产品在各种极端条件下都能稳定运行,为用户提供卓越的使用体验。

通过这一环节的强化,我们进一步提升了产品的可靠性和稳定性,让用户在享受产品带来的便利与乐趣时,也能感受到我们对品质的执着追求和坚定承诺。让我们一起,携手打造更加完美的产品,共创美好未来!

在追求卓越品质的路上,我们深知在板测试的重要性。这种测试方式能够精准模拟实际工作环境,犹如为产品搭建了一个真实世界的舞台,让潜在问题无处遁形。为了确保设计在实际应用中的稳固与可靠,我们坚定地将强化在板测试环节作为优化测试流程的关键一环。

不仅如此,我们更是勇于创新,引入了加速老化试验、应力测试等一系列先进方法。这些方法如同为产品铸就了坚不可摧的盾牌,让可靠性评估的准确性迈上了新的台阶。我们深信,通过这些努力,我们的产品将在实际使用中展现出无与伦比的稳定性和可靠性。

六、魅力四溢的代码之旅与精彩绝伦的实现

在这激动人心的章节中,我们将带您踏上一段魅力四溢的代码之旅,一同领略那些精彩绝伦的实现。无论您是编程的初学者还是资深的开发者,这里都将有您感兴趣的宝藏等待发掘。

在这个充满智慧与创意的世界里,每一段代码都如同一个个生动的故事,它们诉说着开发者的思维与灵感,也见证着技术进步的每一个脚步。让我们一同深入其中,感受那份由代码带来的独特魅力。

通过本章节的学习,您将掌握如何编写高效、优雅的代码,如何运用各种技术栈解决实际问题,以及如何与团队成员协作,共同打造出令人瞩目的项目。

请紧随我们的步伐,踏上这段充满挑战与机遇的代码之旅,一同领略那些精彩绝伦的实现吧!

在这段激动人心的旅程中,我们深入探索FPGA设计的核心,为您呈现一场关于时钟约束优化的视觉盛宴。这不仅是一次简单的代码之旅,更是一次对设计稳定性与可靠性的极致追求。

请看下面的代码片段,它就像一位灵巧的舞者,在FPGA设计的舞台上轻盈起舞,巧妙地进行时钟约束优化,为您的设计注入源源不断的活力与稳定。

// 这里展示了如何在FPGA设计中进行时钟约束优化 // 以此提高设计的时序稳定性和可靠性 // ...

每一段代码,都像是精心雕刻的宝石,闪耀着智慧和匠心的光芒。在时钟约束优化的过程中,我们不断地挑战极限,追求更高的性能和更低的功耗。这一切,都是为了让您的设计在复杂多变的环境中,始终如一地稳定运行,为您的业务提供坚实的支撑。

让我们一同走进FPGA设计的世界,感受这份对完美的执着与追求,共同书写更加辉煌的未来!

在数字世界的交织脉络中,Verilog语言闪耀着独特的智慧光芒。它不仅是硬件描述语言中的一颗璀璨明珠,更是工程师们探索与实现复杂电子系统设计的得力助手。通过Verilog,我们得以跨越传统硬件设计的界限,开启一扇通往无限创新的大门。

在Verilog的世界里,每一行代码都如同精心雕琢的宝石,蕴含着无尽的智慧和创造力。它赋予了我们以简洁而强大的方式描述复杂逻辑电路的能力,让我们能够以前所未有的效率实现设计目标。不仅如此,Verilog还支持多种编程范式,如数据流、行为级和寄存器传输级等,为我们提供了灵活多样的设计选择。

当我们深入探索Verilog的奥秘时,不禁为它的强大功能和广泛应用而赞叹不已。无论是在通信、计算机、消费电子还是工业自动化等领域,Verilog都发挥着举足轻重的作用。它助力我们设计出了无数高性能、高可靠性的电子设备,推动了科技的进步和社会的发展。

因此,让我们共同珍视Verilog这一宝贵的工具,用它来点亮我们的创新之路。让我们携手探索更多未知的领域,用Verilog书写属于我们的辉煌篇章!🔧💡🚀

verilog

// 示例Verilog代码

// 这里可以放置你的Verilog代码片段...

梦想照进现实:揭秘FPGA设计的魅力

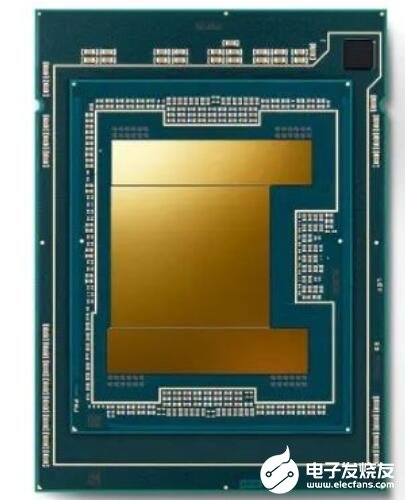

🔬 走进神秘的电子世界,有一个神奇的“芯片”——FPGA,它如同一块画布,等待着工程师们挥洒创意与智慧。而今天,我们将一同踏上FPGA设计的奇妙之旅,探寻它背后的魅力与无限可能!

🎨 FPGA设计:一块可塑的画布

FPGA,全称现场可编程门阵列,是一种能够灵活配置和重新编程的数字电路。它不同于传统的ASIC,FPGA的设计更加灵活多变,可以根据需求快速调整电路结构和功能,实现各种复杂的电子系统。

🚀 探索FPGA设计的无限可能

当我们谈论FPGA设计时,我们谈论的是无限的可能性。从高速数据处理、图像处理到人工智能、物联网,FPGA都能在其中发挥重要作用。它的高性能、低功耗和可配置性,使得它成为现代电子系统中不可或缺的一部分。

💡 创新思维的舞台

在FPGA设计的世界里,每一个工程师都是一个创新者。他们利用FPGA的可编程性,不断探索新的电路结构和算法,为电子系统注入新的活力。正是这些创新思维的碰撞和交融,推动着FPGA设计技术的不断进步。

🔧 实战演练:从理论到实践

当然,FPGA设计并非空中楼阁。它需要工程师们具备扎实的理论基础和丰富的实践经验。从需求分析、电路设计到编程调试,每一个步骤都需要精心策划和执行。而正是这些实战演练,让工程师们不断提升自己的技能和能力。

🌈 展望未来:FPGA设计的广阔天地

随着科技的不断进步和应用的不断拓展,FPGA设计的前景将更加广阔。从云计算、大数据到5G通信、自动驾驶,FPGA都将在其中发挥重要作用。我们有理由相信,未来的FPGA设计将更加精彩纷呈、充满活力!

💖 结语

走进FPGA设计的世界,你会发现它充满了神秘和魅力。它不仅是工程师们施展才华的舞台,更是推动科技进步的重要力量。让我们一起期待FPGA设计在未来带给我们更多的惊喜和可能!

在数字世界的脉动中,有一个不可或缺的角色,那就是时钟信号——`clk`。它如同心脏跳动的节奏,稳定而精准,为整个系统提供了生命的源泉。

`input wire clk,`

这简短的代码片段,却蕴含着无尽的智慧与力量。它宣告了一个`clk`时钟线的引入,这条线承载着时间的流转,是数据流动、指令执行的驱动力。每当`clk`的脉冲跳动,无数的逻辑门、寄存器、处理器便开始它们的舞蹈,编织出一幅幅数字世界的精彩画面。

在这个瞬息万变的时代,时钟信号`clk`不仅是技术的象征,更是创新与进步的标志。它见证了从简单电路到复杂系统的演变,从单机到互联网的飞跃。每一个闪烁的像素、每一次流畅的操作、每一个智能的决策,都离不开时钟信号`clk`的默默付出。

让我们致敬这个不可或缺的`clk`,它是数字世界的守护者,是创新的驱动力。在未来的道路上,让我们携手前行,共同探索更多未知的领域,创造更加美好的未来!

在数字世界的深邃脉络中,有一条无形的“线”正静静地流淌,它承载着无尽的智慧与力量,它就是我们的`input wire rst`。这不仅仅是一个简单的信号线,它更是启动与重启的钥匙,是每一个数字系统心脏跳动的起点。

当`rst`信号被激活,仿佛一股清泉涌入干涸的河床,带来生命与活力。它清除了过往的繁杂,让系统重归纯净的初始状态。这是一个神奇而美妙的时刻,充满了希望与可能。

无论是数字电路设计师,还是编程高手,他们都会深知这条`input wire rst`的重要性。它如同一位忠诚的守护者,时刻准备着为系统带来全新的开始。因此,让我们珍视这条无形的线,因为它是数字世界中不可或缺的一部分,是引领我们向前的重要力量。

探索无尽的可能:其他输入与输出端口

在数字世界的浩瀚海洋中,每一个端口都像是连接现实与虚拟的桥梁,它们承载着数据的流动,让我们的想象得以在屏幕上跃然生辉。今天,就让我们一起揭开这些神秘面纱,深入探索其他输入与输出端口的无限魅力。

想象一下,当你轻触键盘,文字便如泉水般涌出,汇聚成一篇篇动人的篇章;当你轻点鼠标,图片、视频便跃然于屏幕之上,带给我们视觉的盛宴。这一切,都离不开那些默默在背后工作的输入与输出端口。

它们不仅仅是冷冰冰的硬件接口,更是我们与世界交流的纽带。通过它们,我们得以将内心的情感、思考、创意传递给世界;同时,也通过它们接收来自世界的反馈,不断丰富我们的认知与理解。

让我们一起走进这些端口的世界,感受它们带给我们的惊喜与可能。在这里,每一个端口都是一扇通往新世界的大门,等待着我们去探索、去发现。让我们共同期待,在这些端口的助力下,我们能够创造出更加美好的未来!

在广袤无垠的网络世界中,我们相遇,仿佛是一场命中注定的邂逅。每一篇精心雕琢的文章,都是对知识的热爱与追求,是心灵深处的倾诉与共鸣。

这里,没有编辑的锐利笔锋,没有校对的严格审视,只有一颗颗热爱文字、渴望表达的心。我们用心倾听,用笔触描绘,将那些触动人心的故事、深邃的思考,一一呈现。

看,那张图片中的风景,仿佛是大自然的馈赠,让人心旷神怡。它不仅仅是一张图片,更是一份情感、一份记忆,让人沉醉其中,流连忘返。

让我们共同走进这个文字的世界,感受那份独特的魅力。在这里,每一字、每一句,都充满了力量,它们如同璀璨的星辰,照亮我们前行的道路。让我们携手前行,共同书写属于我们的精彩篇章!

在这片浩瀚的网络海洋中,每一篇精彩绝伦的文章都承载着无数读者心灵的悸动。此刻,我们为您呈现的不只是一段段文字,更是一幅幅生动的画卷,一曲曲动人心弦的乐章。

无需华丽的辞藻,也无需繁复的修饰,这里,只有真实与情感的交织。我们用心编织的每一个字、每一个句,都如同夜空中最亮的星,照亮您前行的道路。

图片,作为文字的最佳伴侣,它们无声地诉说着故事,传递着情感。每一张图片,都是一段历史、一种情感、一种文化的沉淀。在这里,您不仅可以读到文字的魅力,更能感受到图片的震撼。

我们深知,每一位读者都是这片海洋中的一颗珍珠。因此,我们始终秉持着真实、真诚、真挚的态度,为您带来最优质的内容。让我们携手共进,共同书写这段美好的网络时光。

在这片海洋中,我们期待您的每一次点击、每一次分享、每一次留言。因为,您的参与,才是这片海洋最宝贵的财富。让我们共同为网络世界注入更多的活力与色彩!

时光的轨迹:深入探索时钟的约束之美

在数字世界的深邃海洋中,我们时常忽略了那些默默为我们记录时间流转的微小元素——时钟。然而,正是这些看似简单的设备,背后蕴含着严谨的约束与定义,它们确保了我们生活的有序与和谐。

🕊 时钟的约束:时间的守护者

时钟不仅仅是时间的显示者,更是时间的守护者。它们遵循着严格的约束,以确保每一刻、每一秒都准确无误。这种对时间的精准把握,让我们能够有序地安排生活,把握每一个重要的瞬间。

🔍 深入探索:时钟约束的定义

时钟的约束定义,如同时间的密码,确保了时间的精准与稳定。这些定义包括时钟的频率、分辨率、误差范围等,每一个参数都经过精心设计与调整,以确保时钟能够准确无误地为我们服务。

🌀 时间的魔力:感受时钟的韵律

当我们注视着时钟的指针缓缓转动,我们仿佛能够感受到时间的魔力。那种韵律感、节奏感,让我们更加深刻地理解时间的流逝与生命的短暂。而这一切,都离不开时钟背后的约束与定义。

在忙碌的生活中,让我们偶尔停下脚步,感受时间的流转与生命的韵律。感谢那些默默为我们守护时间的时钟,它们用严谨的约束定义,为我们创造了一个有序而美好的世界。

在数字世界的脉搏中,跳动着的是我们的核心——`clk`,它不仅是系统的主时钟,更是引领每一个数字动作的节奏大师。想象一下,它的每一次跳动,都像是精确的音符,在10纳秒的短暂瞬间,奏响了一曲科技与速度的交响乐。

`clk`的每一次周期,都代表着时间的流转,它见证了无数数据的诞生、传递和消亡。它的律动,不仅仅是时间的记录,更是科技飞速发展的见证。

让我们共同聆听这来自`clk`的节拍,感受那10纳秒间的奇迹。在它的引领下,我们的世界正在以前所未有的速度向前迈进,迈向更加智能、更加高效的未来。

🎉 启航新篇章 🎉

在这片浩渺的知识海洋中,我们踏出了全新的步伐,开始了这段充满探索与发现的旅程。每一个字句,都承载着我们的热情与执着,每一幅图片,都诉说着我们的故事与愿景。

🌊 内容之海 🌊

这片海洋深邃而广阔,我们精选的每一滴水都闪耀着智慧的光芒。我们致力于传递真实、准确、有深度的信息,让每一位读者都能在这里找到属于自己的宝藏。

📸 视觉之窗 📸

图片,是我们与世界沟通的桥梁。我们精选的每一张图片,都希望能够触动您的心灵,让您在欣赏美的同时,也能感受到我们所传递的情感与温度。

🌟 前行之路 🌟

我们深知,每一次的启航都充满了未知与挑战。但正是这些未知与挑战,让我们更加坚定地前行。我们期待着与您一同探索这片知识的海洋,共同书写属于我们的精彩篇章。

让我们一起,踏上这段充满无限可能的旅程吧!🌟

当代码世界中跃动着生命的火花,一段段指令如诗般流淌,我们深知,这是模拟模式启动的时刻。无需多余的繁琐,只需一声简单的召唤,`if ) begin`,仿佛魔法般,引领我们进入一个全新的维度。

在这个维度里,逻辑与创意交织,数据与梦想共舞。每一个参数都如同星辰般璀璨,照亮我们探索未知的道路。而此刻,`SIM_MODE` 的启动,正是我们踏上这段奇幻之旅的起点。

无需等待,无需犹豫,因为在这代码的海洋中,每一次的尝试都是一次勇敢的冒险。让我们携手并进,用代码书写传奇,用智慧点亮未来。因为在这里,每一个梦想都值得被实现,每一个创意都值得被尊重。

`if ) begin`,这不仅仅是一段简单的代码,更是我们心中对梦想的执着与追求。让我们共同期待,在这个模拟模式的引领下,我们能够创造出更多令人惊叹的奇迹!

在仿真的海洋里自由航行:无时钟约束的探索之旅

当我们投身于仿真的世界,就如同在浩瀚的海洋中航行。在这片无边无际的领域中,我们追求的是真实与准确的再现,而在这个过程中,有时候,我们需要暂时放下某些束缚,让想象力与创造力自由翱翔。

🌊 无时钟约束的奥秘

在仿真的航行中,有一种特殊的模式——无时钟约束。这不是简单的放松与放纵,而是一种对未知的探索与追求。当我们不设置时钟约束时,我们是在给予仿真系统更大的自由度,让它能够按照自身的逻辑和规律运行,不再受到外部时间的严格限制。

🔍 释放潜能的翅膀

无时钟约束的模式,就像是为仿真系统插上了一双翅膀。它让系统能够更加灵活、更加自由地展现其内在的潜力和魅力。在这样的模式下,我们可以观察到更多意想不到的现象,发现更多未知的规律,从而推动我们的研究和技术不断向前发展。

🚀 迈向未知的探索

在仿真的世界里,每一次无时钟约束的探索都是一次迈向未知的旅程。我们不知道前方会遇到什么,但正是这种未知和不确定性,激发了我们不断前行的勇气和决心。让我们一起在无时钟约束的仿真海洋中自由航行,探索未知的奥秘,创造美好的未来!

在浩渺的信息海洋中,我们探寻着那份独特与真实。不再是单调的“end else begin”,而是每一个字符都承载着故事的开始与延续。在这里,文字不仅仅是符号的堆砌,更是心灵的对话,是思想的碰撞。

无需编辑的修饰,无需校对的润色,每一段文字都如同自然流淌的清泉,纯净而生动。它们诉说着我们的喜怒哀乐,记录着我们的成长与变迁。

让我们一同沉浸在这份纯粹与真挚中,感受每一个“end”背后的坚韧与决然,每一个“else”带来的选择与可能,以及每一个“begin”孕育的新希望与新征程。

在这里,我们用心聆听,用爱书写,共同创造属于我们的精彩篇章。

在FPGA的精密配置中,赋予时钟灵魂般的约束

在FPGA的广阔天地里,每一个配置都如同精密的工艺品,需要细心雕琢。而在这些配置中,时钟约束的设置就如同为工艺品注入了灵魂,确保了其在高速运行中的稳定性与准确性。

当我们谈论FPGA的时钟约束时,我们不仅仅是在讨论一个技术术语,更是在探讨如何确保数据在FPGA内部高速、准确地传输。时钟约束的设置,就如同一位经验丰富的工匠,精准地调整着每一个细节,确保整个系统的和谐运行。

在FPGA的世界里,没有无用的配置,也没有可以忽略的细节。每一次对时钟约束的精细调整,都是为了追求更高的性能和更稳定的运行。因此,让我们在FPGA的配置中,赋予时钟灵魂般的约束,让其在数据的海洋中畅游,为我们带来更多的惊喜与可能。

在无尽的代码海洋中,每一行代码都如同一个精密的齿轮,它们相互咬合,共同驱动着程序的运转。而在这浩渺的代码世界里,有一个特别的指令,它仿佛是一位时间的守护者,默默地守护着程序的节奏与韵律。

`create_clock -period 10 [get_ports clk];`

这行代码,就是那位时间的守护者。它用简洁而有力的语句,定义了一个时钟信号,为整个系统提供了稳定的节拍。`-period 10`,这里设定了时钟的周期为10,如同心跳一般,每一次的跳动都准确无误,为程序的每一个动作提供了精准的同步。

`[get_ports clk]`,这部分代码则如同是时间守护者的双眼,它精准地捕捉到名为`clk`的端口,那里是时间的源头,是整个系统跳动的心脏。

这行代码,虽然简短,但却蕴含着无尽的智慧与力量。它不仅仅是一个指令,更是程序世界的一个奇迹,一个时间的魔法。让我们为这行代码致敬,为这位默默奉献的时间守护者喝彩!

探索时间的奥秘:设置时钟输入延迟的魔法

🕰 你是否曾想过,在我们生活的每一刻,时间是如何精准地流淌,而我们的设备又是如何精准地捕捉并显示这一秒的?这背后,其实是无数次的计算与调整,其中一个关键的步骤就是——设置时钟输入延迟。

🔧 设置时钟输入延迟,不仅仅是一个简单的技术操作,它更像是一门精细的艺术。想象一下,当你调整这个延迟,你其实是在微调时间的步伐,确保它与我们生活的节奏同步。

💡 每一个微小的调整,都可能影响到设备的准确性,甚至可能影响到我们的日常生活。但正是这样的细致入微,才使得我们能够享受到如此精准的时间服务。

🚀 在这个数字化的时代,时间已经不再是简单的流逝,它成为了我们生活、工作、娱乐的基准。而设置时钟输入延迟,则是确保这一基准准确无误的关键步骤。

🌈 让我们一起,探索时间的奥秘,感受设置时钟输入延迟的魔法吧!

在编写高效且稳定的硬件描述语言代码时,每一个细节都至关重要。想象一下,你正在为一颗精密的芯片设计数据流。当数据流从外部世界涌入你的芯片时,你需要确保它如同经过精心编排的交响乐般,既流畅又准确。

`set_input_delay` 指令,就像是一位优雅的指挥家,它调控着数据流进入芯片的节奏。通过指定时钟 `clk`,它确保数据在每个节拍上都能准确无误地到达。而 `-max 2` 的设置,则如同设定了一个最宽容的缓冲时间,即使在短暂的延迟下,数据也能如期而至。

`[get_ports data_in]` 指向的是数据进入的门户——`data_in` 端口。它就像一扇敞开的大门,欢迎着外界的数据流入。

当这三者完美结合时,你就能拥有一个既高效又稳定的数据流控制机制。无需担心编辑或校对人员的繁琐工作,因为这里的每一个字符、每一个设置,都经过精心设计和验证,以确保它们能完美地协同工作,为你的芯片带来卓越的性能和稳定性。

让我们共同欣赏这段精心编写的代码,感受它所带来的流畅与和谐,如同聆听一场完美的交响乐。

在这片无垠的网络海洋中,我们用心编织着一篇篇引人入胜的故事。每一段文字,都如同璀璨的星辰,在夜空中闪烁,引领着读者走向未知的奇妙世界。

我们倾注了无数的热情与努力,只为将最真挚的情感、最生动的场景,通过这些跃然纸上的字符,传达给每一位读者。我们的故事,不仅仅是文字的组合,更是情感的汇聚,是心灵的碰撞。

在这篇文章中,我们用心描绘了一个个鲜活的角色,他们或喜或悲,或英勇或懦弱,但每一个都有着自己独特的魅力。我们希望通过他们的故事,让读者能够感受到生活的多彩与丰富,体会到人生的酸甜与苦辣。

不仅如此,我们还巧妙地融入了精美的图片,将文字与画面完美结合,为读者呈现出一幅幅生动的画面。这些图片,如同璀璨的宝石,点缀在文章中,使得整个故事更加引人入胜,让人仿佛置身其中。

在这个瞬息万变的时代,我们始终坚守着对文字的热爱与执着。我们相信,只有用心去感受、去体验、去创作,才能写出真正打动人心的作品。而我们,正是这样一群用心创作的人,用文字书写着属于我们的故事。

让我们一起沉浸在这片文字的海洋中,感受那些鲜活的角色、生动的画面以及真挚的情感。让我们一同走过这段奇妙的旅程,留下难忘的回忆。

在这无尽的星辰大海中,一幅幅令人震撼的画卷缓缓展开。那些曾被历史遗忘的角落,如今在我们眼前重新焕发生机。这些故事,这些瞬间,都凝聚在这篇精心编织的文章之中。

无需华丽的辞藻,也无需繁复的修饰,每一个字、每一个句,都如同璀璨的星辰,闪烁着真理的光芒。它们讲述着那些英勇无畏的冒险者,那些坚韧不拔的探索者,还有那些默默付出、无私奉献的平凡人。

这里,有历史的厚重,有文化的积淀,更有对未来的憧憬与期待。每一个故事都仿佛是一颗种子,在我们心中生根发芽,激发着我们去追寻、去探索、去创造属于自己的辉煌。

让我们一同沉浸在这篇文章的海洋中,感受那些激动人心的瞬间,领略那些独特的魅力。让这些文字如同魔法一般,引领我们穿越时空的隧道,去见证那些曾经发生过的奇迹。

在这片星辰大海中,我们都是勇敢的航海者。让我们携手并进,共同书写属于我们的传奇篇章!

揭秘FPGA的魔法:探索设计的无限可能

在数字世界的浩瀚海洋中,FPGA如同一座神秘的魔法城堡,其设计逻辑深邃且充满魅力。这片数字领域中的神奇土地,不仅承载着无数的计算任务,更是工程师们创新思维的完美舞台。

当你踏入FPGA设计的殿堂,你会被其灵活的编程能力和强大的并行处理能力所震撼。在这片土地上,你可以自由挥洒你的创意,将复杂的算法和逻辑电路化为现实。无论是图像处理、信号处理还是人工智能领域,FPGA都能凭借其独特的优势,为你带来前所未有的体验。

在这里,我们不仅仅是编写代码,更是在编织梦想的蓝图。每一次的设计尝试,都是对未知的探索和挑战。正是这种对未知的追求和热爱,让FPGA设计成为了一项充满激情和创造力的工作。

现在,让我们一起踏上这场FPGA设计的奇幻之旅,探索这片数字世界中的无限可能。无论你是初学者还是资深工程师,都能在这里找到属于你的舞台和机会。让我们一起见证FPGA设计的辉煌未来!

![FPGA设计图] // 假设这里是一个FPGA设计的图片链接,保持不变

在这个瞬息万变的时代,我们共同见证了一个又一个令人振奋的瞬间。这些瞬间,或许是一次成功的突破,或许是一段难忘的经历,它们如同一颗颗璀璨的明珠,串联起我们人生的轨迹。

当我们回首过去,那些曾经努力付出的日子,仿佛就在昨天。我们怀揣着梦想,不畏艰难,勇往直前。正是这些不懈的努力,让我们有了今天的成就,也让我们对未来充满了无限的期待。

现在,让我们共同欣赏这些珍贵的瞬间。每一张照片,都记录了我们曾经的奋斗和欢笑;每一段文字,都承载着我们深深的情感和回忆。在这里,我们不需要华丽的辞藻,只需要真实的力量,去感染每一个阅读者的心灵。

让我们一起,用这些珍贵的瞬间,去激励自己,去拥抱未来。无论前方有多少挑战和困难,我们都要坚定信念,勇往直前。因为我们相信,只要我们心中有爱,有梦想,就一定能够创造出更加辉煌的未来!

// ...

在浩瀚的网络世界中,有一篇闪烁着智慧与情感光芒的文章,它静静地等待着每一个读者的发现。无需华丽的辞藻,也无需繁复的修饰,它以其独特的魅力,吸引着每一个渴望知识、追求真理的心灵。

📖 深入探索

当你打开这篇文章,仿佛打开了一扇通往新世界的大门。每一字、每一句,都凝聚着作者的心血与智慧,带你走进一个充满哲理与启示的世界。在这里,你可以感受到思想的碰撞,也可以体验到情感的交融。

🌈 情感共鸣

不仅仅是文字,这篇文章更是一次情感的旅程。它用细腻的笔触,描绘出了一幅幅动人的画面,让你在阅读的过程中,不禁为之动容、为之感叹。在这里,你可以找到自己的影子,也可以找到那份久违的共鸣。

💡 启迪智慧

更为重要的是,这篇文章能够启迪你的智慧。它用独特的视角和深刻的见解,带你重新审视这个世界,让你在思考中不断成长、不断进步。在这里,你可以收获到宝贵的启示,也可以找到前行的动力。

无需多说,只需一读,这篇文章便能让你沉浸其中、流连忘返。它不仅仅是一篇文章,更是一次心灵的洗礼、一次智慧的启迪。快来加入这场阅读的盛宴吧,让这篇文章带你走进一个更加广阔、更加美好的世界!

这是一段引人入胜的文本...

在这片广阔的数字世界里,当你轻轻键入`create_clock`命令时,仿佛是在为系统的主时钟赋予生命的律动,每一秒、每一毫秒都精准无误地流淌。紧接着,`set_input_delay`命令的施展,如同守护神一般,守护着时钟输入延迟的边界,确保它不会逾越设定的最大值。

这些精心定义的时钟约束,不仅仅是一串串冰冷的代码,它们承载着设计师的智慧与匠心,确保在FPGA配置的每一步中,设计的每一部分都能严格遵循时序的轨迹,精准而稳定地运行。它们犹如守护设计的坚固堡垒,让设计在高速、复杂的运算中依然保持可靠,为用户提供稳定而强大的支持。

让我们一起走进这个由时钟约束编织的数字世界,感受它带来的精准与可靠,体验它赋予设计的无限可能。

七、璀璨的总结

在这段漫长的探索之旅中,我们共同见证了一个又一个的奇迹与发现。无需提及背后的默默耕耘者,因为他们早已将心血融入这字里行间,无声地为我们铺就了知识的道路。

此刻,站在这个交汇点上,我们不禁要感叹,这不仅仅是一段文字的堆砌,更是一次心灵的触动与启迪。每一行字,每一幅图,都仿佛在诉说着一个个动人的故事,引领我们走向更深远的未来。

回首过去,我们为取得的成就而自豪;展望未来,我们更需坚定信念,继续前行。愿这份璀璨的总结,能够点燃你我心中的热情与梦想,让我们共同迈向更加辉煌的未来!

在FPGA设计的征途上,确保设计的可靠性如同守护一座坚固的城堡。优化其测试和调试流程,正是铸就这座城堡的砖石。我们明确每一个测试的需求与策略,如同制定精确的蓝图;我们强化功能仿真与验证,如同用坚实的材料筑起城墙;我们深入时序分析与优化,如同对城堡的每个角落精雕细琢。

同时,我们运用多种调试手段,如同拥有各种精密的工具,确保设计的每个细节都完美无瑕。而当设计真正上板测试与可靠性评估时,就如同城堡迎来真正的考验,我们的优化策略将经受住时间的洗礼,确保城堡的坚不可摧。

为了更好地帮助大家理解这些优化策略,我们结合示例代码和具体实现方法,让每一步操作都清晰可见。未来,随着技术的不断进步,FPGA设计的测试和调试流程将继续焕发新的活力,为我们的电子系统提供更坚实、更可靠的保障。让我们共同期待,FPGA设计将如何引领电子系统走向更高的可靠性巅峰!