来源:C Lighting

线边缘粗糙度(LER)

线边缘粗糙度(LER)指的是栅极图案边缘的随机变化,即印刷图案边缘的粗糙度。当最小特征尺寸减小到几十纳米以下时,LER对MOSFET性能的影响就无法忽视了。LER会在沟道长度方向上产生一些幸运(lucky)通道(即局部短沟道),从而导致器件之间的不匹配。例如,在Intel的65纳米器件中,当LER的标准偏差三倍值(3σ)大于标称栅极关键尺寸(critical dimension)的10%时,实验观察到了导通驱动电流(on-state drive current)下降了2%。

由于LER引起的变异与短沟道效应(SCE:short channel effect)高度相关,因此具有较强短沟道效应抵抗力的器件结构在给定的LER轮廓下受到的性能变异影响较小。例如,由FinFET和三栅MOSFET组成的六晶体管(6-T)静态随机存取存储器(SRAM)单元,或者超薄体器件,如全耗尽硅绝缘体MOSFET(FDSOI MOSFET),由于它们改进了栅极到沟道的电容耦合(与传统平面体MOSFET相比),因此对LER引起的工艺变异有更好的免疫力。

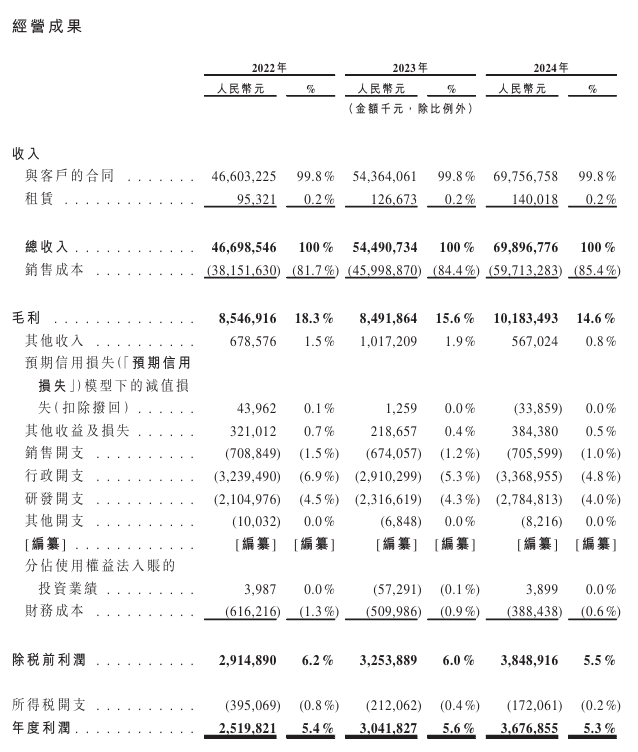

此外,如表1所示,通过利用双重图案技术(DP),28纳米三栅体(tri-gate)MOSFET中的LER引起的阈值电压(VTH)变异可以减少大约20%。值得注意的是,尽管LER引起的VTH变异减少了,总的随机变异量只略有减少。这表明在三栅体MOSFET中,随机掺杂波动(RDF:random dopant fluctuation)或工作函数变异(WFV:work function variation)等其他随机变异源要比LER更为显著。然而,尽管在 FinFET 器件中,由LER引起的VTH变化有所减小,但fin边缘粗糙度(即沿沟道长度方向的 LER)已与 WFV 一起成为最关键的随机变化源之一。

表1:三栅极 MOSFET 中 LER 引起的 VTH 变化(取决于光刻技术)

LER的物理来源

在光刻步骤中,掩膜上绘制的图案会转移到抗蚀层上,因为抗蚀层的溶解度会因抗蚀层是否受光照射而变化。为了提高对光的敏感度,通常会使用化学放大法。在这一过程中,化学放大的抗蚀剂暴露在光下以产生酸。在曝光后的烘烤步骤中,这些酸会催化聚合物的去保护作用。抗蚀剂的去保护部分很容易被显影剂溶解,从而产生抗蚀图案。最终的 LER 曲线包含了前面每个加工步骤的所有累积变化。

2.1 掩模图案的LER

在考虑LER(线边缘粗糙度)时,掩模图案本身的任何粗糙度似乎都是LER的根本原因。如果掩模图案本身就存在LER,并且光刻技术能够无失真地转移这种LER,那么投射到PR(Photo Resist)层上的图案就会具有与掩模图案完全相同的LER轮廓。实际上,掩模边缘的波动是不可避免的,掩模图案本身就有一定的粗糙度。然而,这种粗糙度相对于原始图案的尺寸来说足够小,以至于可以忽略不计。从技术上来讲,在当前193纳米光刻技术下,几乎不可能转移微小的图案(即掩模图案的粗糙度)。因此,掩模图案固有的LER不会对PR图案的LER造成贡献。

尽管如此,掩模图案的粗糙度仍然是一个值得关注的因素,尤其是在更高精度的需求下。随着技术的进步,更先进的光刻技术可能会使掩模图案的微小粗糙度成为问题。例如,在EUV光刻中,掩模图案的精确度变得更加关键,因为EUV光刻技术可以实现更精细的特征尺寸。在这些情况下,掩模图案的粗糙度可能会对最终的光阻图案产生影响。

总的来说,虽然掩模图案的粗糙度通常不足以直接导致光阻图案的LER,但在更先进的制造工艺中,它可能成为一个需要注意的问题。制造商通常会采取措施来最小化掩模图案的粗糙度,并确保光刻过程中其他因素得到控制,以减少LER的影响。

2.2 曝光剂量的变化

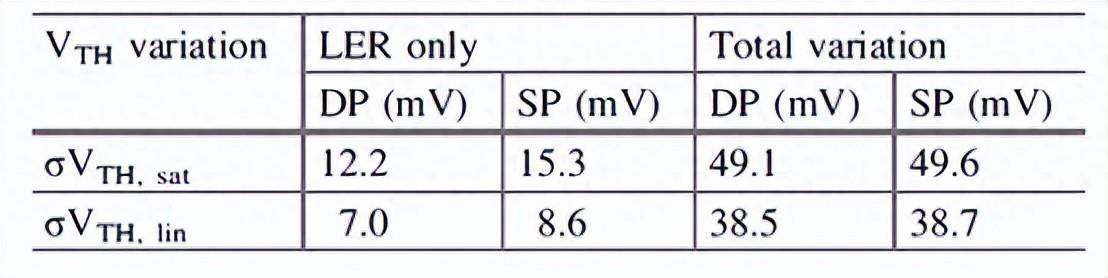

光刻技术所能达到的分辨率主要取决于所使用的投影透镜的尺寸,因为投影透镜的孔径(或直径)决定了衍射阶次。理论上,需要一个无限大的透镜来收集所有的衍射阶次;然而,实际上的透镜具有有限的尺寸。这一现实往往限制了光刻技术的分辨率。其结果是,到达光阻表面的曝光光线强度并不是阶跃函数的形状,而是sinc函数的形状(即,曝光光线的强度具有一定的梯度)。

图1:光刻步骤示意图。展示了光线强度对LER的影响,由于光强度的梯度,Pattern边缘与Mask边缘并不完全匹配。

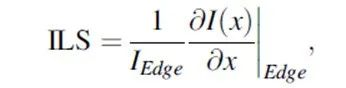

我们假设,如果曝光光线的强度等于或高于阈值强度,则光阻会被酸激活,从而可以容易地溶解出去。光阻图案的边缘是曝光光线强度等于阈值剂量的点。为了定量理解特征边缘处的空中图像对比度,引入了图像对数斜率(Image Log-Slope, ILS)的概念:

其中

是边缘处的光强和边缘处的光强斜率。ILS描述了曝光光线强度从完全暴露到未暴露区域过渡的陡峭程度。较高的ILS意味着边缘更加清晰,从而有助于减少LER。

在制造过程中,随着光刻工艺中每个步骤的完成,每个步骤中的曝光光强度往往会因激光输出功率的变化、光学系统的振动、晶片载物台的微小上下移动和/或光量化导致的总剂量波动等不良影响而波动。由于光刻胶图案的边缘是由光强决定的,因此曝光光强的波动是 LER 的根本原因之一。如果图案边缘的光强斜率较陡,边缘的波动就会减小。因此,要减轻 LER,明暗对比度必须很大(即光强梯度陡峭)。

曝光剂量的变化会对光刻结果产生显著影响。例如,即使是很小的剂量变化也可能导致光阻图案的边缘移动,进而影响LER。剂量控制的非准确性可能是由于光源强度的变化、透镜系统的不完美、掩模与光阻两者之间的距离变化等多种因素造成的。

剂量的变化可以通过多种方式来量化和控制。一种常用的方法是通过剂量扫描实验来确定最佳曝光剂量,以获得所需的图案尺寸和形状。此外,还可以使用剂量反馈控制系统来实时调整曝光剂量,以减少因剂量变化引起的LER。值得注意的是,即使图像对比度持续增加,LER 也会在5 nm处达到饱和。超过这一点,任何残余的LER都来自抗蚀剂固有的材料粗糙度。

总之,曝光剂量的变化是影响光刻技术中LER的重要因素之一。通过优化曝光条件、改善透镜设计以及采用先进的剂量控制技术,可以有效地减少这种影响,从而提高光刻图案的质量。

2.3 化学放大(CA:Chemically Amplified)光阻中的LER生成

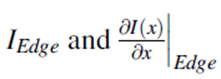

在CMOS制造过程中,化学放大被用来提高光阻的灵敏度。化学放大光阻包含图3所示的光酸化发生器(photoacid generator)。当化学放大光阻薄膜中的光酸化生成器吸收来自光的能量时,它们分解成酸阳离子和其他阴离子。这一分解过程被称为去保护反应。在曝光后的烘烤步骤中,生成的酸在光阻薄膜内扩散,并帮助催化去保护反应。酸是不会被消耗掉,而是在去保护反应中持续存在,因此能够反复催化这些反应。由于酸可以改变聚合物的溶解性,去保护的聚合物区域可以选择性地被显影剂去除,从而使掩模上的图案能够转移到光阻薄膜上。

然而,由于酸在光阻薄膜内随机扩散,这会导致LER的产生。在曝光后的烘烤步骤中,(i)烘烤温度,(ii)去保护反应的局部程度,以及(iii)反应副产品的浓度都会影响酸的扩散系数。Acid molecule的扩散距离通常是几十纳米。但是,很难完全控制扩散速率,因为在烘烤过程中温度、局部反应程度和副产品浓度都不是恒定的。因此,有可能某些酸会扩散到目标边缘之外。如果未曝光区域被这些酸充分的去保护,它们将被显影剂溶解,从而导致LER中的higher frequency成分增加。

图2:在化学放大的抗蚀剂中,LER是在曝光后的烘烤步骤中由于酸扩散而形成的。

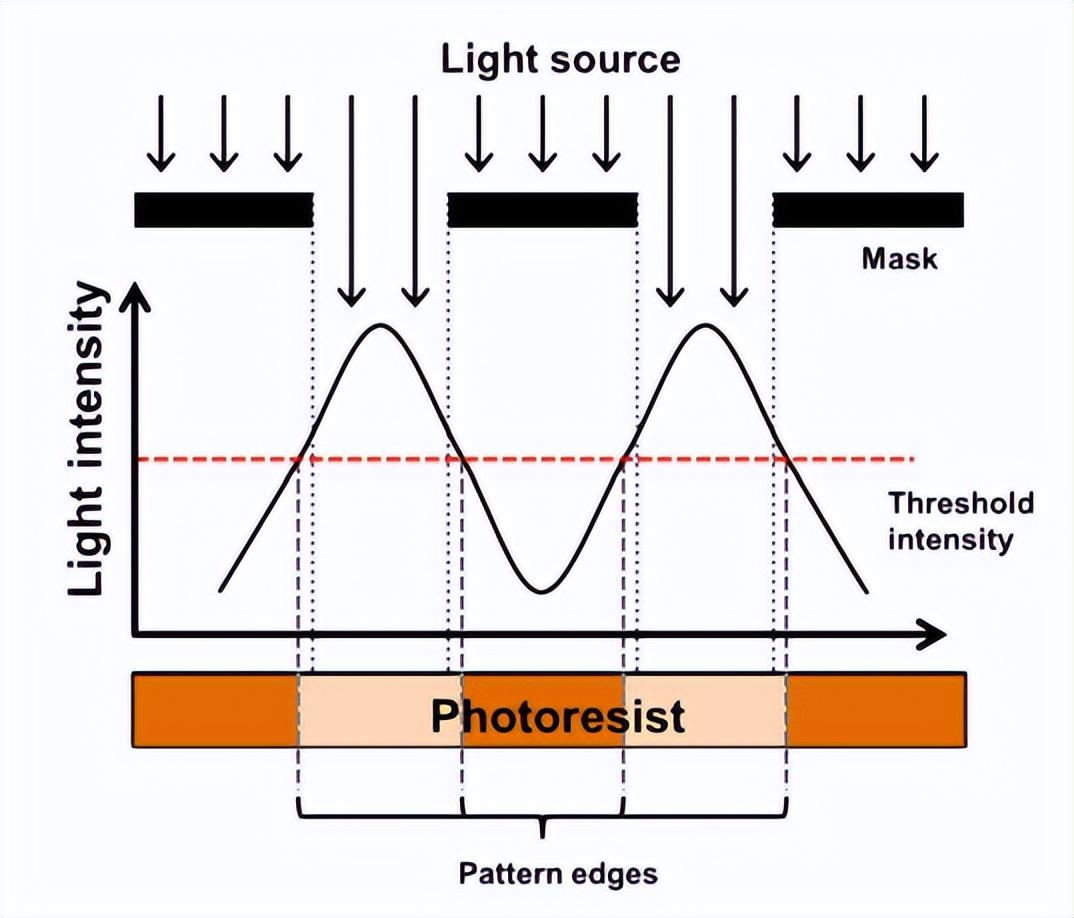

2.4 光阻的固有粗糙度

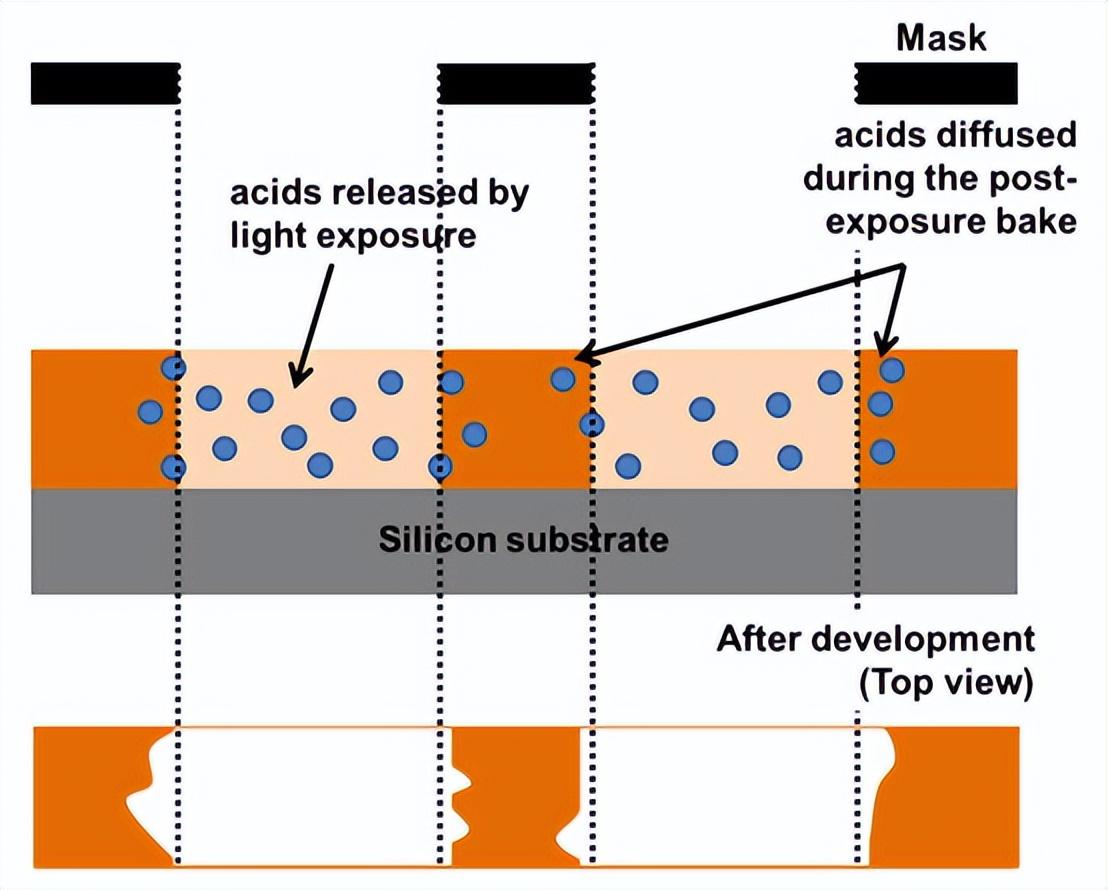

即使排除了其他LER(线边粗糙度)的来源,光阻本身的非均匀性也会沿侧边造成LER。例如,即使曝光光强度是没有变化的,光阻的光子吸收也会随物理位置的不同而有所变化。假定光子吸收均匀,光刻胶聚合物链中的随机溶解和不同尺寸会在图案边缘产生粗糙(见图 2.4)。此外,沿着曝光图案的边缘,一些聚合物分子会涂抹到显影液中,但仍固定在抗蚀剂薄膜的其他部分。在去离子水冲洗过程中,这些部分溶解的聚合物链将会重新沉积在抗蚀剂上,并重新确定图案的边缘。

固有粗糙度的来源:

光子吸收的非均匀性:即使光强均匀,光阻的内部的光子吸收也会因位置不同而有所差异,这会导致局部曝光量的变化。

聚合物链的尺寸差异:光阻聚合物链的长度和形状的不一致性也会导致溶解性的差异,进而影响图案边缘的平滑度。

溶解过程的随机性:在显影过程中,聚合物链的溶解是随机的,这会导致边缘粗糙度。

聚合物分子的溶胀和再沉积。溶胀:在显影过程中,聚合物分子可能会从曝光区域的部分溶解并溶入显影剂中。再沉积:在去离子水冲洗步骤中,这些部分溶解的聚合物链将可能会重新沉积在光阻表面,这会影响图案边缘的形状,增加粗糙度。

图3:光刻胶中不同尺寸的聚合物造成的LER

双重图案化对LER的影响

3.1 双重图案化与双重蚀刻

为了提高光阻图案的分辨率而不更换光源(例如,从193纳米到极紫外光刻 EUV),在小于32纳米节点的光刻过程中添加了双重图案化技术。双重图案化技术已在22/20纳米技术及以上广泛采用。请注意,双重图案化和双重蚀刻(2P2E:double patterning and double etching)是双重图案化技术的一个例子。2P2E是一种用于提高分辨率的技术,通过两次图案化和两次蚀刻的过程来实现更细的图案。这种技术能够使用相同的光源、光阻和节距尺寸实现更精细的图案。

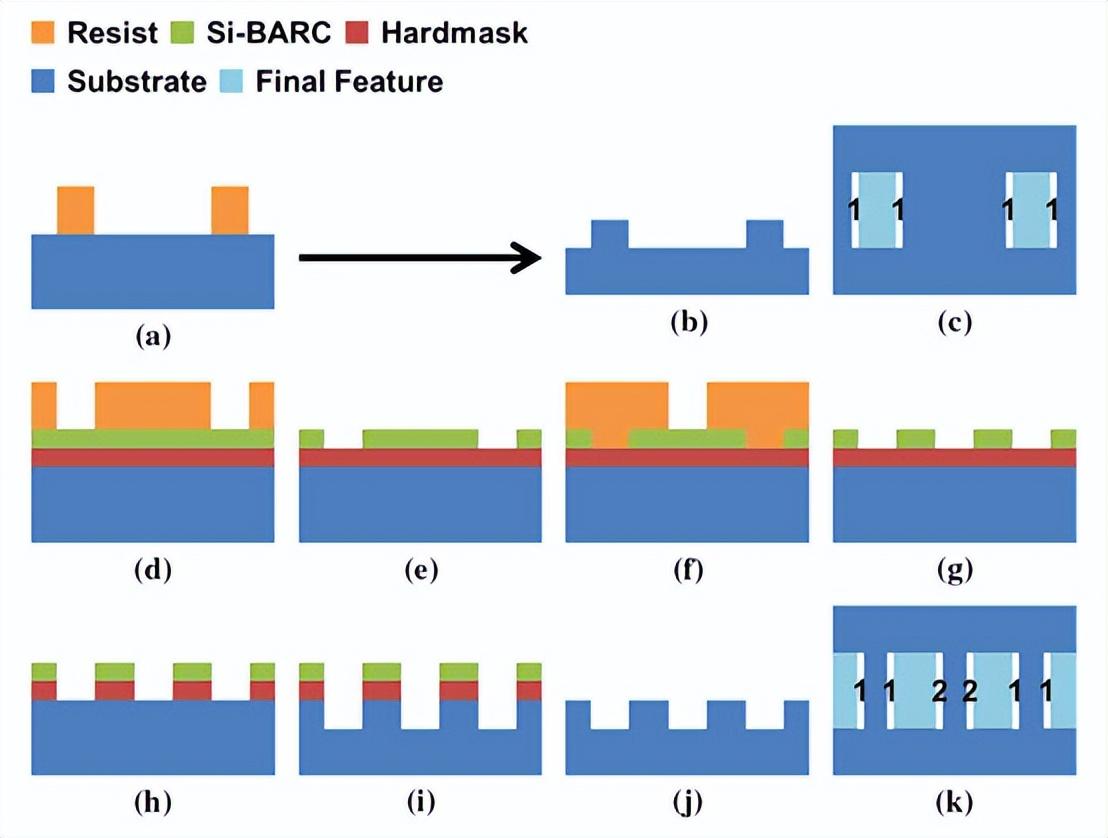

在双重图案化技术中,首先将硅基底抗反射层(Si-BARC)和旋涂氧化层(SOC)涂覆在衬底上。这些层在第一次和第二次光刻步骤中保留了原始图案,并在第二次蚀刻步骤中作为硬掩模发挥关键作用。在Si-BARC上旋涂一层光阻,然后通过第一次光刻步骤投射第一个图案(图4d)。通过随后的第一次蚀刻步骤,光阻上的图案转移到Si-BARC上,而在传统工艺中则是蚀刻底层衬底(图4e, b)。接下来,为了第二次光刻步骤,另一层进行光阻的旋涂以填充Si-BARC上的第一个图案,然后执行第二次光刻步骤(图4f)。较薄的Si-BARC膜可对与在版图上涂覆第二层光刻胶堆栈相关的涂层均匀性问题产生最小影响。第二次蚀刻步骤用于将光阻上的图案转移到Si-BARC层上(图4g)。最后,图案从Si-BARC转移到SOC,再从SOC转移到衬底(图4h-j)。因此,双重图案化和双重蚀刻技术能够在使用相同光源、光阻、节距大小和显影方法的情况下实现比传统光刻更精细的图案。

图4:a、b为1P1E技术和d-j为2P2E 技术的图案化工艺顺序。1P1E和2P2E的最终特征的顶视图分别显示在(c)和(k)中。请注意,每个线边缘都用“1”(“2”) 表示,以表明线边缘受到第一 (第二) 图案化步骤的影响。

由于线边粗糙度轮廓通过多次蚀刻过程传递,衬底上的LER轮廓与光阻、Si-BARC和SOC上的原始LER轮廓不同。随着蚀刻过程的完成,图案的边缘趋于平滑。通过统计和实验数据已经确认,基于双重图案化和双重蚀刻技术的LER轮廓的相关长度大于传统的LER轮廓的相关长度。因此,多次蚀刻过程会导致具有较低空间频率和平坦峰谷的更平滑线边,从而减少LER ,使线边更加平滑。此外,额外的热处理,比如在第一次和第二次光刻之间的后烘烤和曝光后烘烤,会进一步增加LER轮廓的相关长度,平滑线边轮廓。

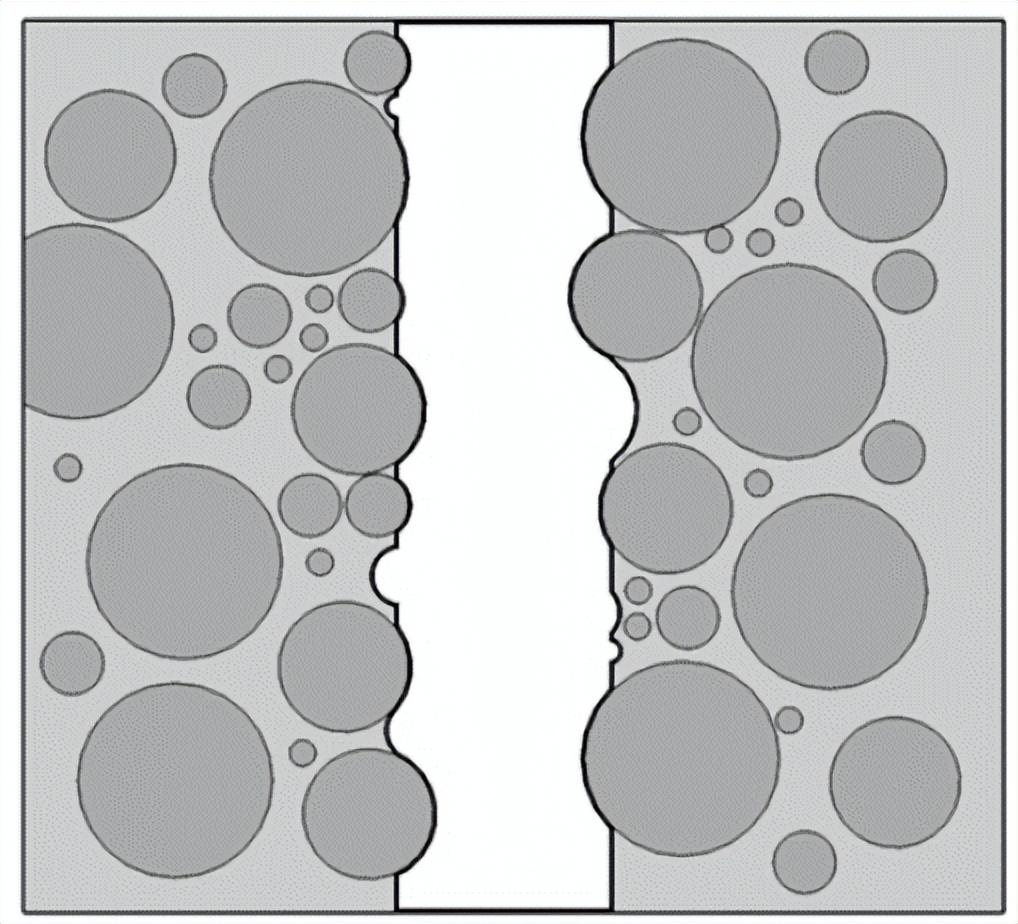

3.2 自对准双重图案化

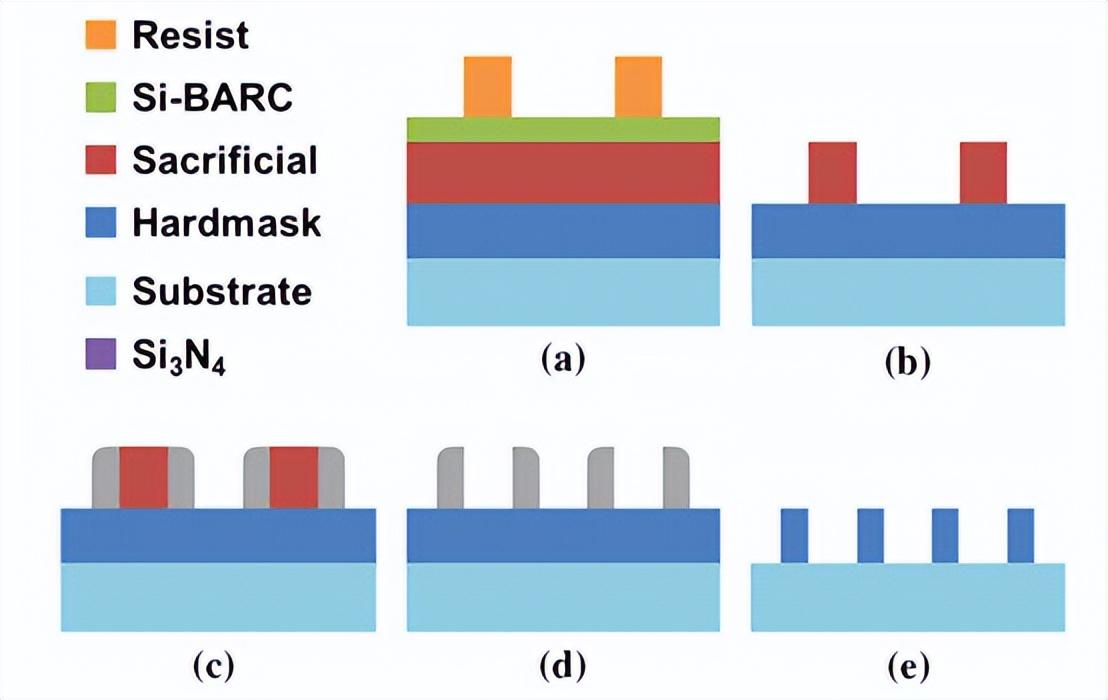

虽然使用双重图案化和双重蚀刻技术需要两次单独的光刻步骤以便使光阻图案的分辨率加倍,但有一种完全不同的方法称为自对准双重图案化,它只需要一次曝光。自对准双重图案化可以通过薄膜沉积、蚀刻和化学机械抛光(CMP)而不需额外的光刻步骤使光阻图案的分辨率加倍。自对准双重图案化的工艺流程参看图5。通过光刻和蚀刻步骤,按照特定的节距将涂覆的光阻图形化(注意,最终图案的节距将会减半)。接下来,光阻上的图案通过等离子蚀刻转移到牺牲层上。然后,牺牲层形成具有1:3的占空比(即:线/空间=1/3)的虚拟栅极。通过硅氮化物(Si₃N₄)的沉积和各向异性蚀刻,形成具有与虚拟Gate相同关键尺寸的间隔层(即,占空比为1:1)。通过各向同性蚀刻步骤消除虚拟栅,只留下堆叠薄膜上的间隔层(Spacer)图案。最后,使用Si₃N₄间隔层作为蚀刻掩模,将间隔层图案转移到硬掩模上。因此,使用自对准双重图案化,光阻的原始节距在最终图案中减少了50%。换句话说,一个光阻线条可以创造两个Spacer,从而将空间频率加倍。

图5:自对准双重图案化技术工艺流程

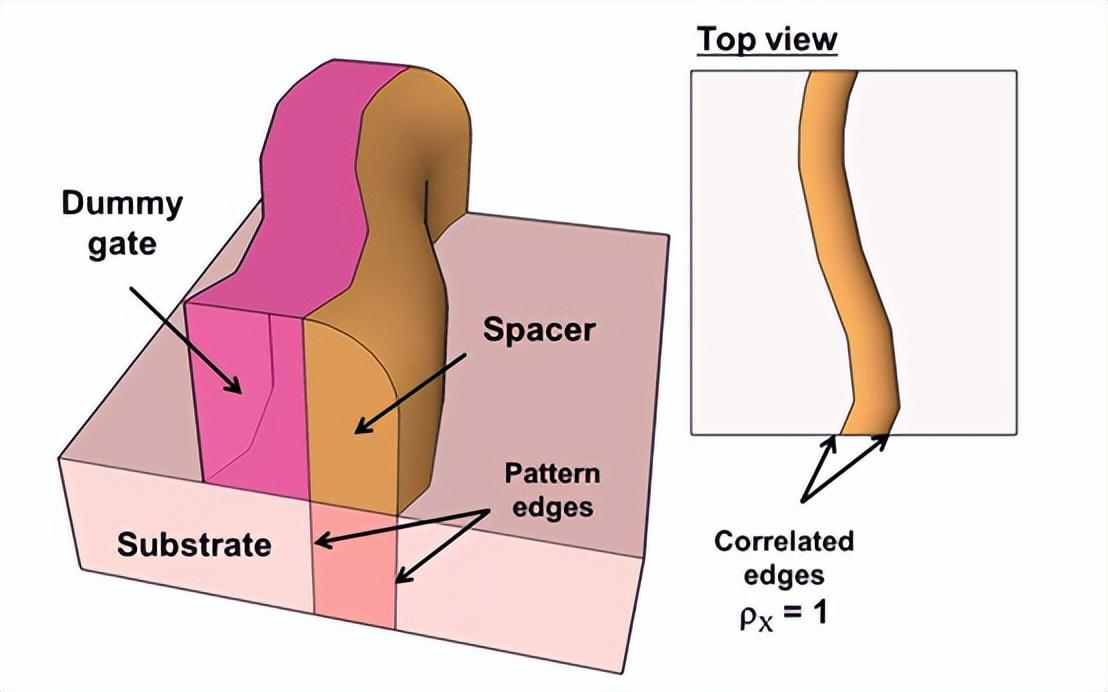

在FinFET的制造过程中,鳍状体可以通过两种方式之一进行图案化:(1) 使用光阻作为掩模(即:“光阻定义”),和 (2) 使用间隔层作为掩模(即:“间隔层定义”)。传统的光阻定义线条创建的边缘具有非关联的粗糙度,可以假设ρX=0。这是因为对于每个光阻的边缘来说,聚合物聚集物的侵蚀是随机进行的。另一方面,间隔层定义的线生成的边缘相当相关。这是由于先进行了保形薄膜沉积过程,接着是高度均匀的各向异性蚀刻过程。这些步骤导致沿虚拟光阻定义特征的侧壁形成了间隔层掩模(图6)。如果间隔层宽度(对应于沉积薄膜的厚度)可以忽略(与LWR空间频率的倒数值相比),间隔层定义的线将具有均匀的宽度。因此,可以假设ρX = 1。总之,如果在FinFET制造过程中使用自对准双重图案化技术,由LWR(而不是LER)引起的性能变化可以几乎消除。

图6:自对准双重图案化技术示意图。此方法可以几乎消除LWR量,实现完美相关的线边缘。

【近期会议】

10月30-31日,由宽禁带半导体国家工程研究中心主办的“化合物半导体先进技术及应用大会”将首次与大家在江苏·常州相见,邀您齐聚常州新城希尔顿酒店,解耦产业链市场布局!https://w.lwc.cn/s/uueAru

11月28-29日,“第二届半导体先进封测产业技术创新大会”将再次与各位相见于厦门,秉承“延续去年,创新今年”的思想,仍将由云天半导体与厦门大学联合主办,雅时国际商讯承办,邀您齐聚厦门·海沧融信华邑酒店共探行业发展!诚邀您报名参会:https://w.lwc.cn/s/n6FFne

声明:本网站部分文章转载自网络,转发仅为更大范围传播。 转载文章版权归原作者所有,如有异议,请联系我们修改或删除。联系邮箱:viviz@actintl.com.hk, 电话:0755-25988573

审核编辑 黄宇