在数字信号处理领域,插值滤波是一项至关重要的技术,广泛应用于图像缩放、音频信号处理、通信系统等多个方面。随着现场可编程门阵列(FPGA)技术的飞速发展,利用FPGA实现高效、实时的插值滤波已成为研究和实践的热点。本文将深入探讨FPGA进行多路并行插值滤波(多相滤波)的实现原理,解析其关键技术,并阐述其在硬件设计中的优势。

一、多相滤波的基本概念

多相滤波是一种将滤波器分割成多个较小单元,然后并行处理这些单元结果的技术。在插值滤波中,多相滤波能够显著提高处理速度和效率。其基本思想是将原始滤波器(如FIR滤波器)分割成多个子滤波器,每个子滤波器处理输入数据的一部分,并并行输出处理结果。这些结果随后在输出端进行合并,得到最终的插值滤波输出。

二、FPGA实现多路并行插值滤波的原理

FPGA以其并行处理能力著称,非常适合实现多路并行插值滤波。在FPGA中,多相滤波的实现通常涉及以下几个关键步骤:

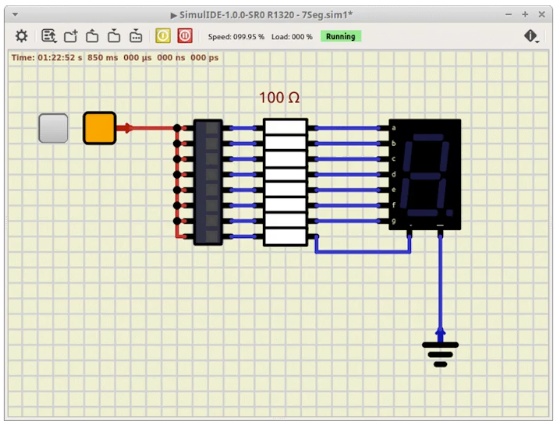

滤波器分割:将原始滤波器分割成多个子滤波器。例如,一个8抽头的FIR滤波器可以被分割成4个2抽头的子滤波器。

数据分配:输入数据流被分配到不同的子滤波器中。这通常通过一个旋转开关或类似的逻辑结构实现,确保每个子滤波器在不同的时钟周期内处理不同的数据样本。

并行处理:每个子滤波器并行处理其分配到的数据样本,执行乘法和加法运算。由于每个子滤波器只处理部分数据,因此可以显著降低单个时钟周期内的计算复杂度。

结果合并:所有子滤波器的输出在输出端进行合并,得到最终的插值滤波输出。这通常需要一个加法器来累加来自不同子滤波器的结果。

三、关键技术及优化

在实现多路并行插值滤波时,需要关注以下关键技术及优化策略:

时钟管理:由于不同子滤波器在不同的时钟周期内处理数据,因此需要精确管理时钟信号,确保数据在正确的时刻被分配到正确的子滤波器中。

资源优化:FPGA资源有限,因此需要通过优化算法和硬件设计来最大化资源利用率。例如,可以复用子滤波器的系数,减少乘法器和加法器的数量。

数据精度:插值滤波对数据精度要求较高,因此需要在硬件设计中考虑数据的表示和存储方式,以避免精度损失。

并行度选择:并行度越高,处理速度越快,但也会增加硬件资源的消耗。因此,需要根据具体应用场景选择合适的并行度。

四、硬件设计优势

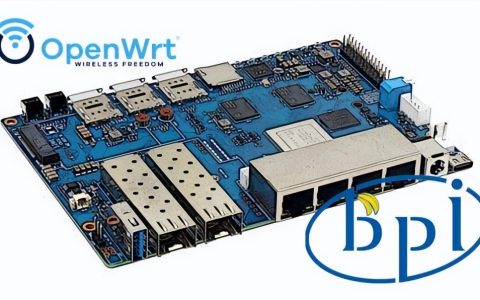

FPGA实现多路并行插值滤波具有以下显著优势:

高速处理:FPGA的并行处理能力使其能够实时处理大量数据,满足高速信号处理的需求。

灵活性:FPGA可以通过重新编程来改变滤波器的参数和结构,因此具有高度的灵活性。

低功耗:相比传统的数字信号处理芯片,FPGA在相同性能下通常具有更低的功耗。

易于集成:FPGA可以与其他硬件模块无缝集成,形成完整的信号处理系统。

结论

FPGA实现多路并行插值滤波(多相滤波)是一项具有挑战性和前景的技术。通过深入理解多相滤波的基本原理和关键技术,结合FPGA的并行处理能力,可以实现高效、实时的插值滤波。未来,随着FPGA技术的不断进步和应用领域的不断拓展,多路并行插值滤波在数字信号处理领域的应用将更加广泛和深入。