在FPGA(现场可编程门阵列)设计中,时序约束是确保设计满足时序要求、提高工作频率和获得正确时序分析报告的关键步骤。其中,主时钟与生成时钟作为时序约束的核心要素,对于设计的稳定性和性能具有至关重要的影响。本文将深入探讨主时钟与生成时钟的定义、作用、约束设置方法以及实际案例,为读者提供全面的理解和实践指导。

一、主时钟与生成时钟的定义

主时钟:

主时钟是FPGA器件外部的板级时钟,通常来源于晶振、数据传输的同步时钟等。在Vivado等FPGA设计工具中,主时钟通过时钟输入端口或高速收发器GT的输出引脚进入FPGA内部。主时钟是设计的基准时钟,其频率和稳定性直接影响整个系统的性能。

生成时钟:

生成时钟,又称衍生时钟,是由主时钟经过时钟管理单元(如PLL、MMCM等)进行分频、倍频、相移等操作后生成的时钟。生成时钟与主时钟紧密相关,其频率和相位可以根据设计需求进行调整。生成时钟的引入,使得设计能够灵活地处理不同频率和相位的信号,提高了设计的灵活性和性能。

二、主时钟与生成时钟的作用

主时钟的作用:

作为设计的基准时钟,为整个系统提供稳定的时钟信号。

驱动FPGA内部的逻辑电路,确保数据在正确的时钟周期内传输和处理。

影响设计的时序性能,如建立时间和保持时间等。

生成时钟的作用:

提供不同频率和相位的时钟信号,满足设计对时钟多样性的需求。

通过分频、倍频等操作,降低或提高时钟频率,以适应不同的应用场景。

实现时钟的相移,以满足特定时序要求,如数据对齐和同步等。

三、主时钟与生成时钟的约束设置方法

在Vivado中,主时钟和生成时钟的约束设置主要通过设计约束文件(.xdc文件)来实现。以下是一些关键的约束设置方法和代码示例:

主时钟的约束设置:

使用create_clock命令来定义主时钟。例如,定义一个周期为10ns的主时钟:

xdc

create_clock -period 10 [get_ports sysclk]

其中,sysclk是时钟输入端口的名称,10是时钟周期(单位为ns)。

生成时钟的约束设置:

使用create_generated_clock命令来定义生成时钟。例如,定义一个由主时钟经过PLL倍频后生成的时钟:

xdc

create_generated_clock -name gen_clk -source [get_ports clk1] -multiply_by 2 -master_clock [get_clocks create_clk1]

其中,gen_clk是生成时钟的名称,clk1是源时钟(可能是主时钟或其他生成时钟)的端口名称,2是倍频系数,create_clk1是主时钟的约束名称(在前面的create_clock命令中定义)。

四、实际案例

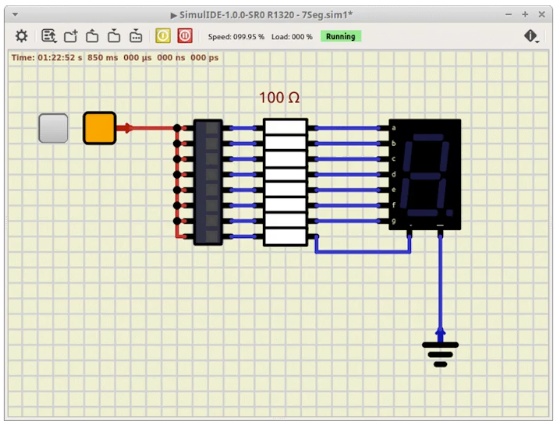

以下是一个简单的实际案例,展示了如何在Vivado中对主时钟和生成时钟进行约束设置。

案例背景:

设计一个FPGA系统,其中主时钟频率为100MHz(周期为10ns),通过PLL倍频后生成一个200MHz的时钟用于数据传输。

约束设置:

定义主时钟:

xdc

create_clock -period 10 [get_ports sysclk]

定义生成时钟:

xdc

create_generated_clock -name tx_clk -source [get_ports sysclk] -multiply_by 2 -master_clock [get_clocks sysclk_clk]

注意:在实际应用中,sysclk_clk可能是自动生成的约束名称,或者在create_clock命令中明确指定。此外,如果PLL的配置已经在Vivado中完成,并且基准时钟已经自动约束,则可能不需要手动添加生成时钟的约束。

五、结论

主时钟与生成时钟是FPGA设计中不可或缺的时序约束要素。通过合理的约束设置,可以确保设计满足时序要求,提高工作频率和稳定性。本文深入探讨了主时钟与生成时钟的定义、作用、约束设置方法以及实际案例,为读者提供了全面的理解和实践指导。希望读者能够从中受益,更好地应用于自己的FPGA设计实践中。