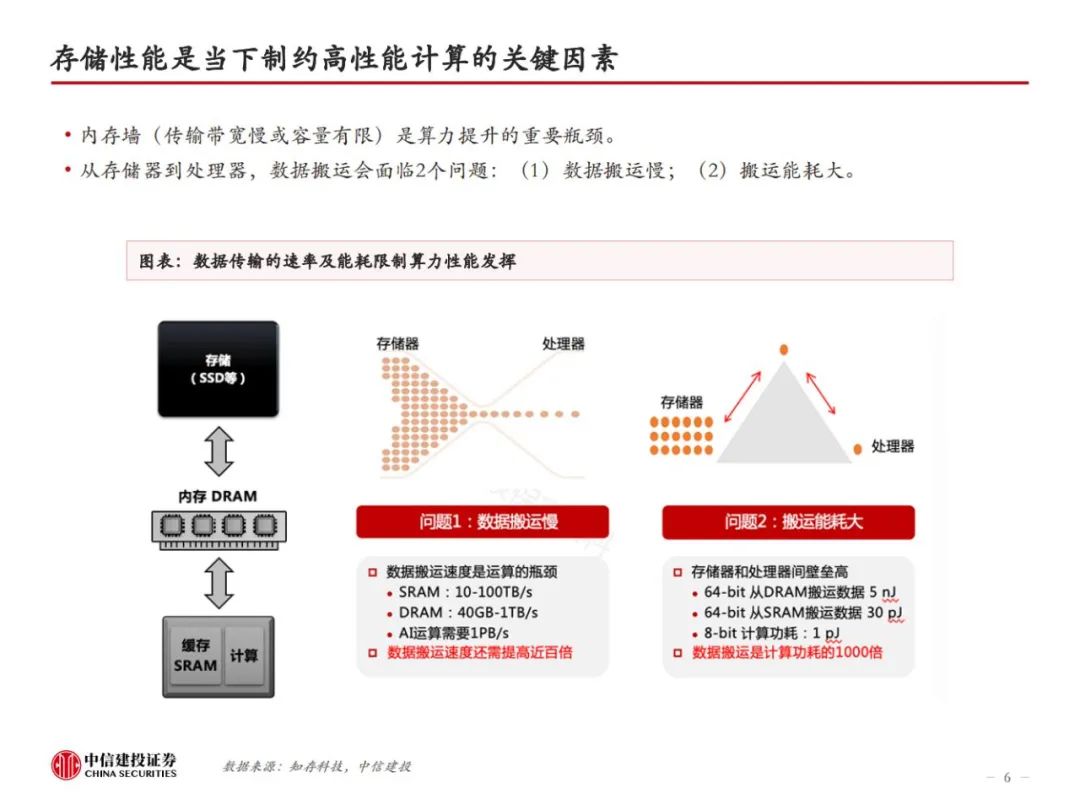

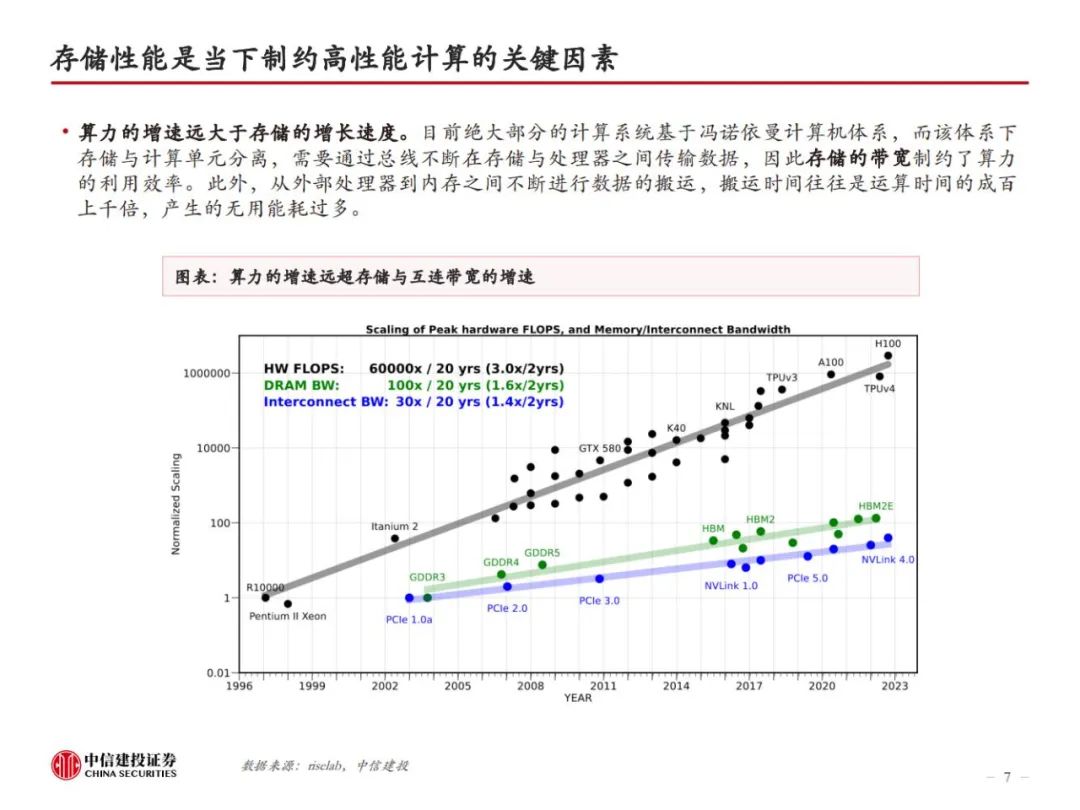

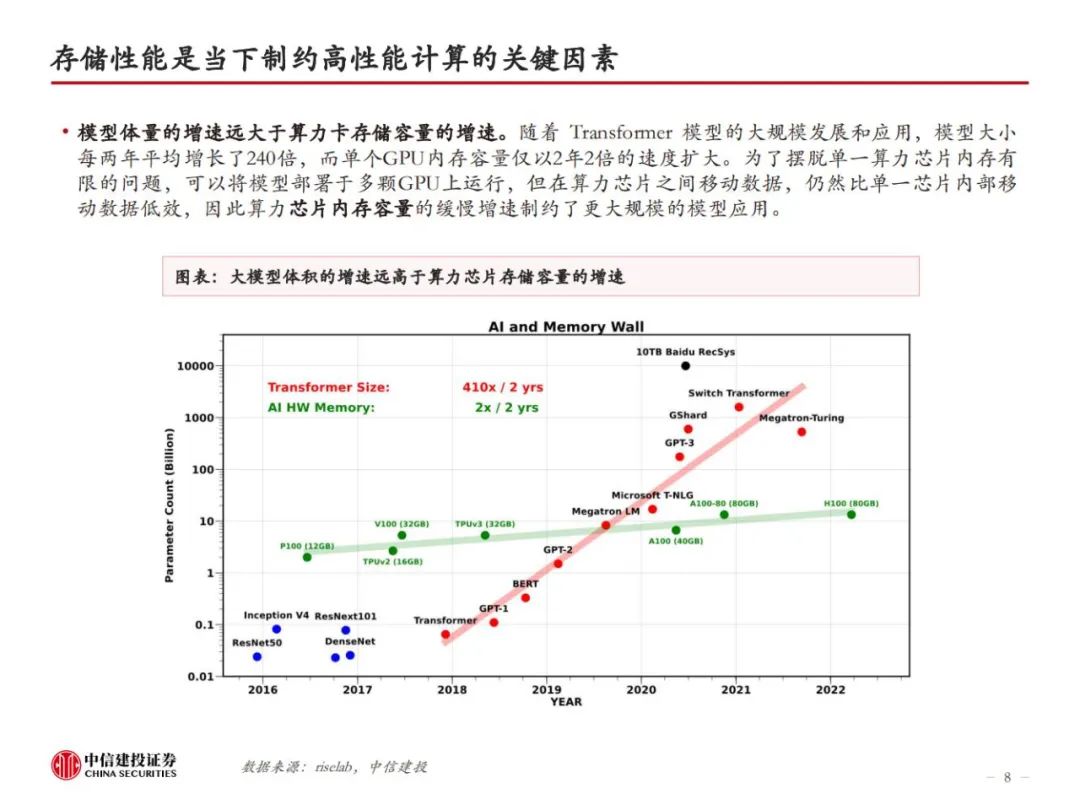

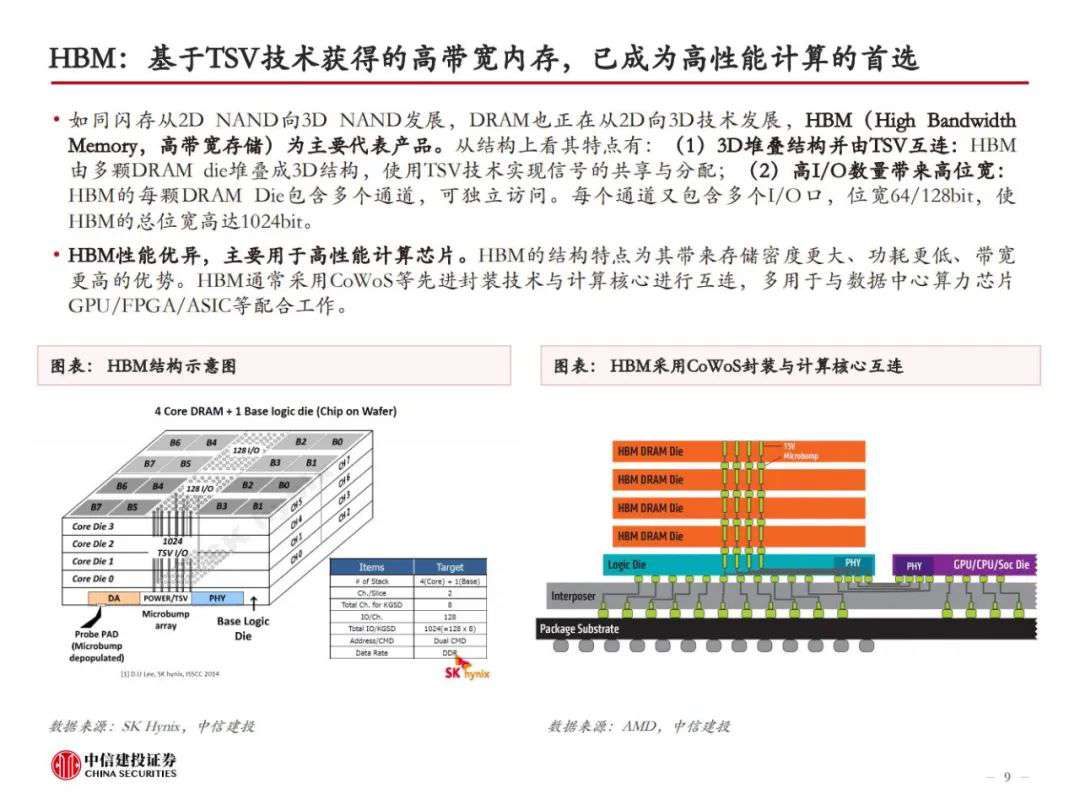

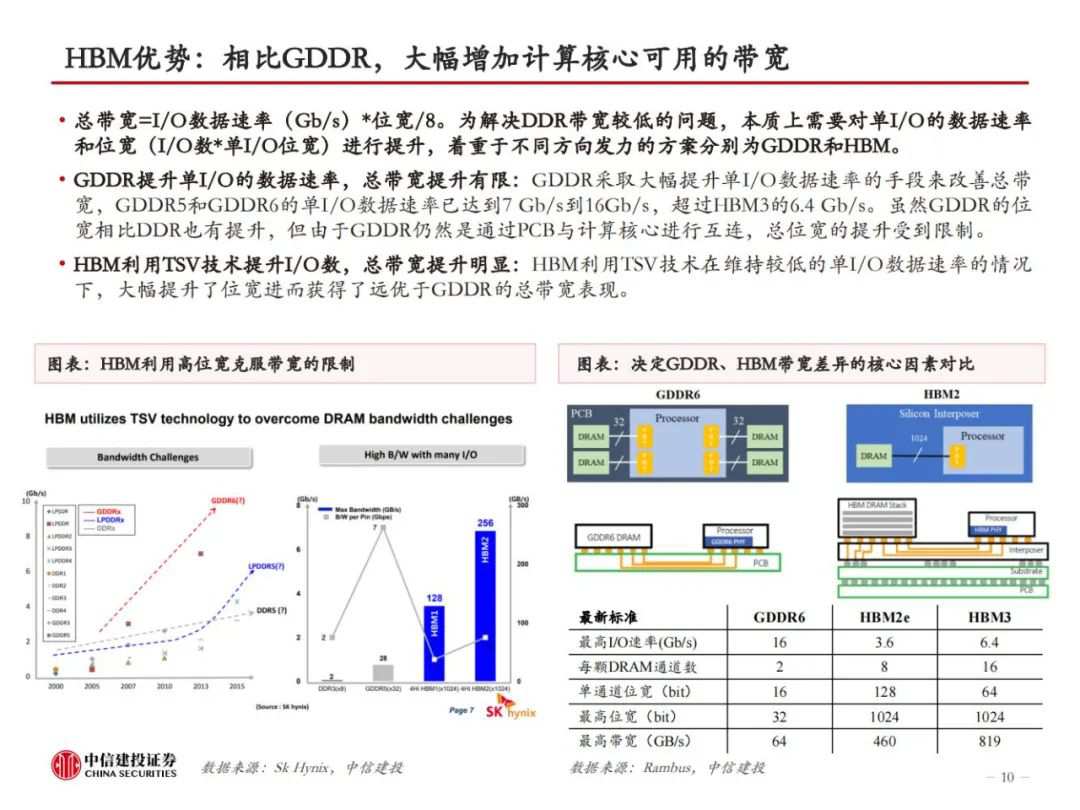

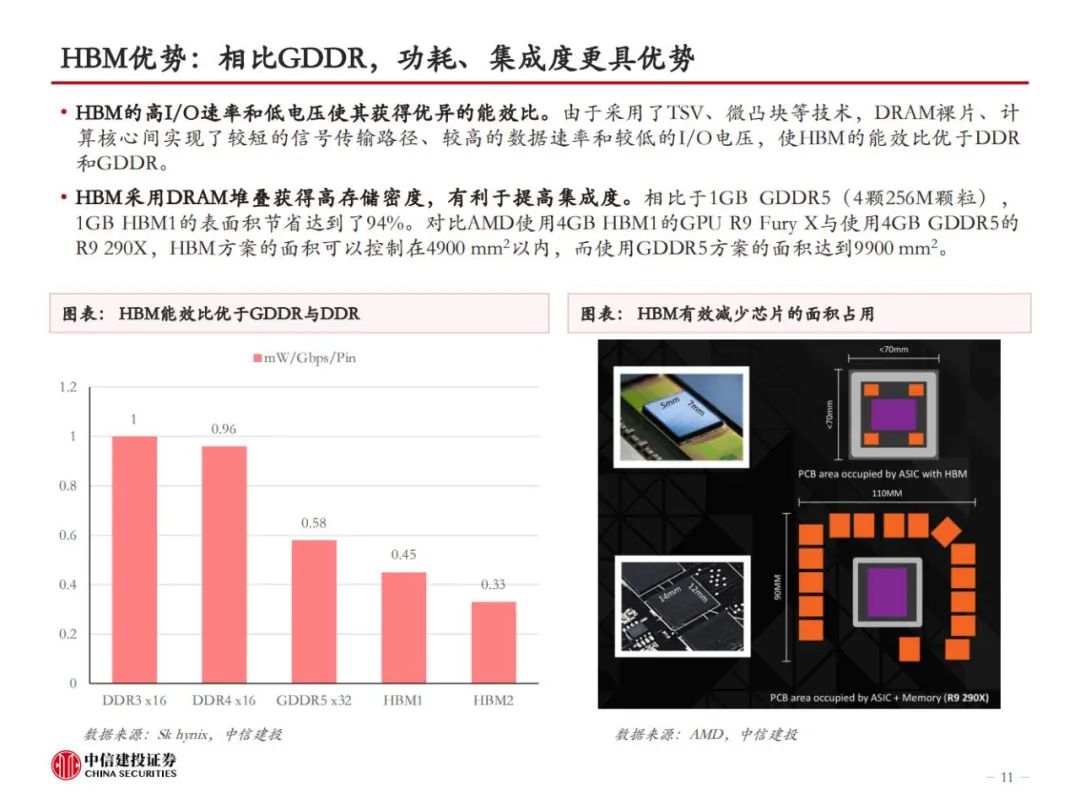

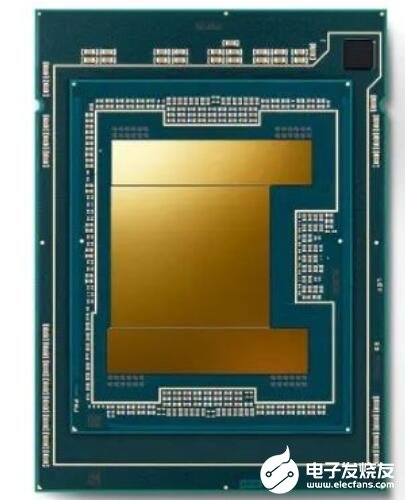

HBM是当前算力的内存瓶颈。存储性能是当下制约高性能计算的关键因素,从存储器到处理器,数据搬运会面临带宽和功耗的问题。为解决传统DRAM带宽较低的问题,本质上需要对单I/O数据速率和位宽进行提升。HBM由于采用了TSV、微凸块等技术,DRAM裸片、计算核心间实现了较短的信号传输路径、较高的I/O数据速率、高位宽和较低的I/O电压,因此具备高带宽、高存储密度、低功耗等优势。即便如此,当前HBM的性能仍然跟不上算力卡的需求。

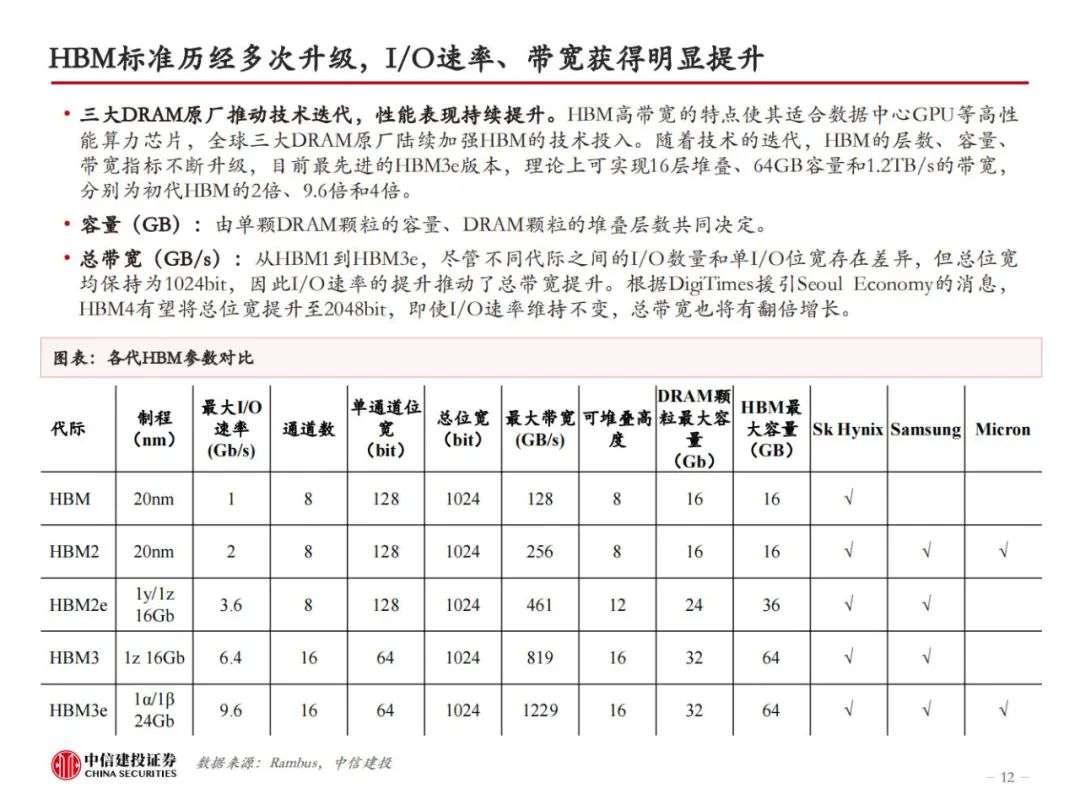

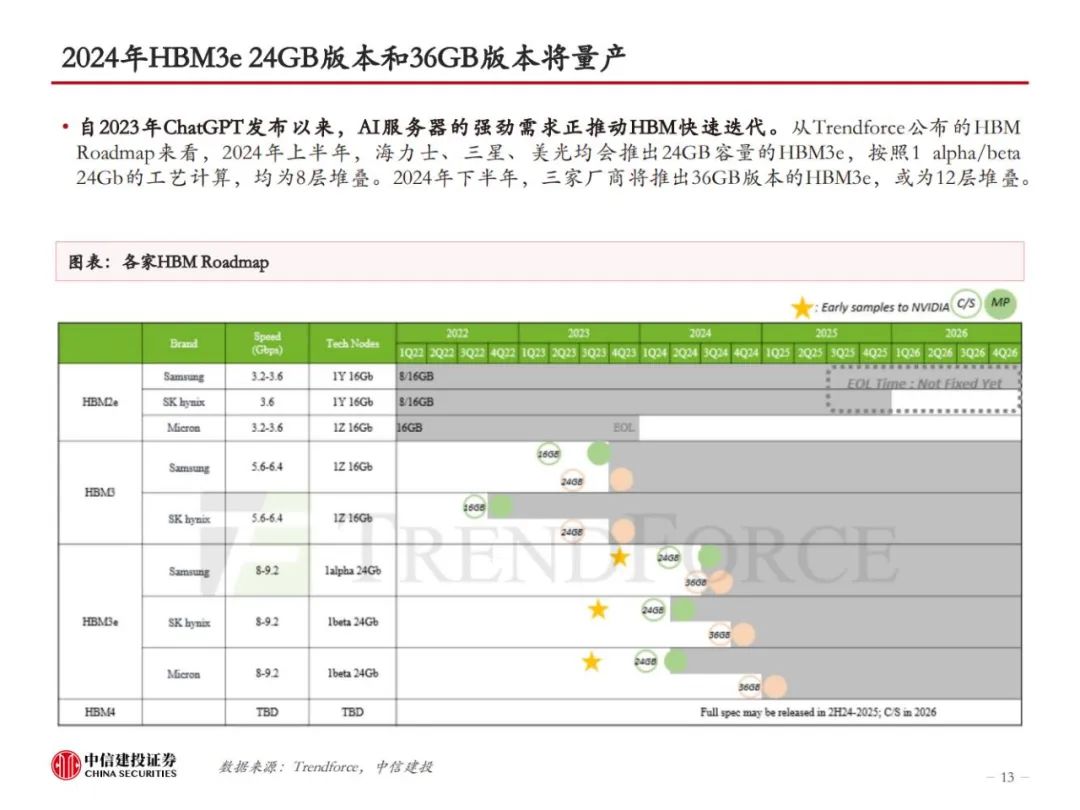

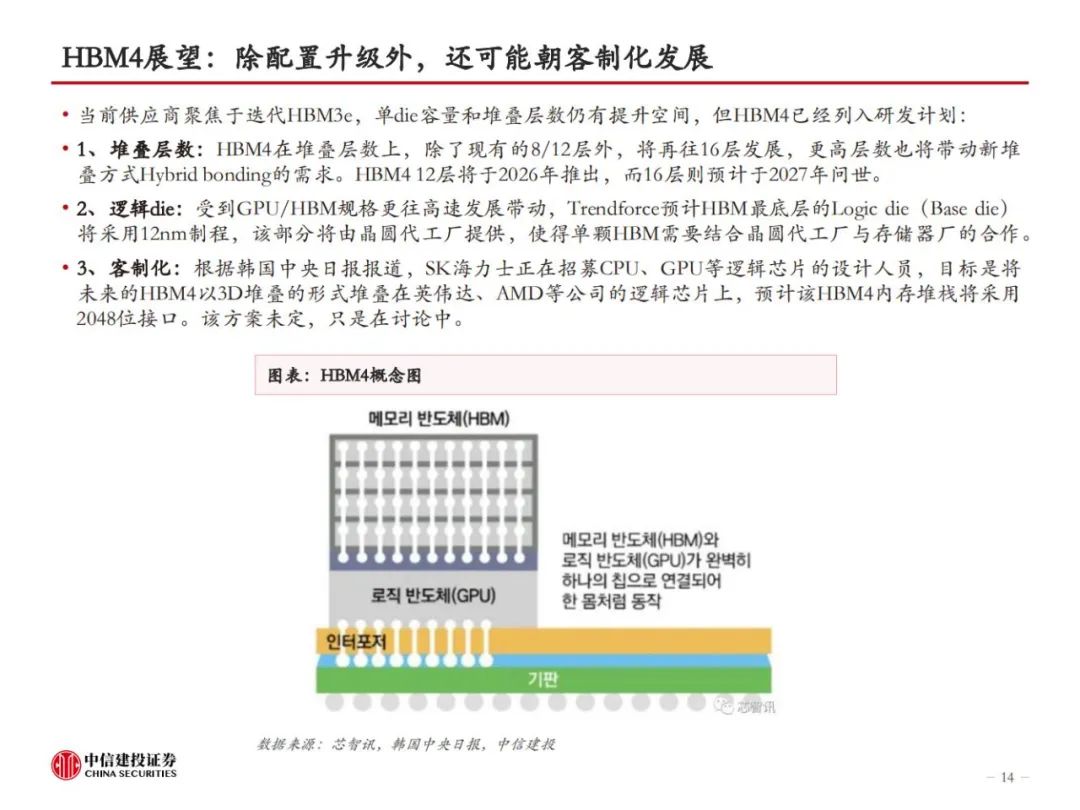

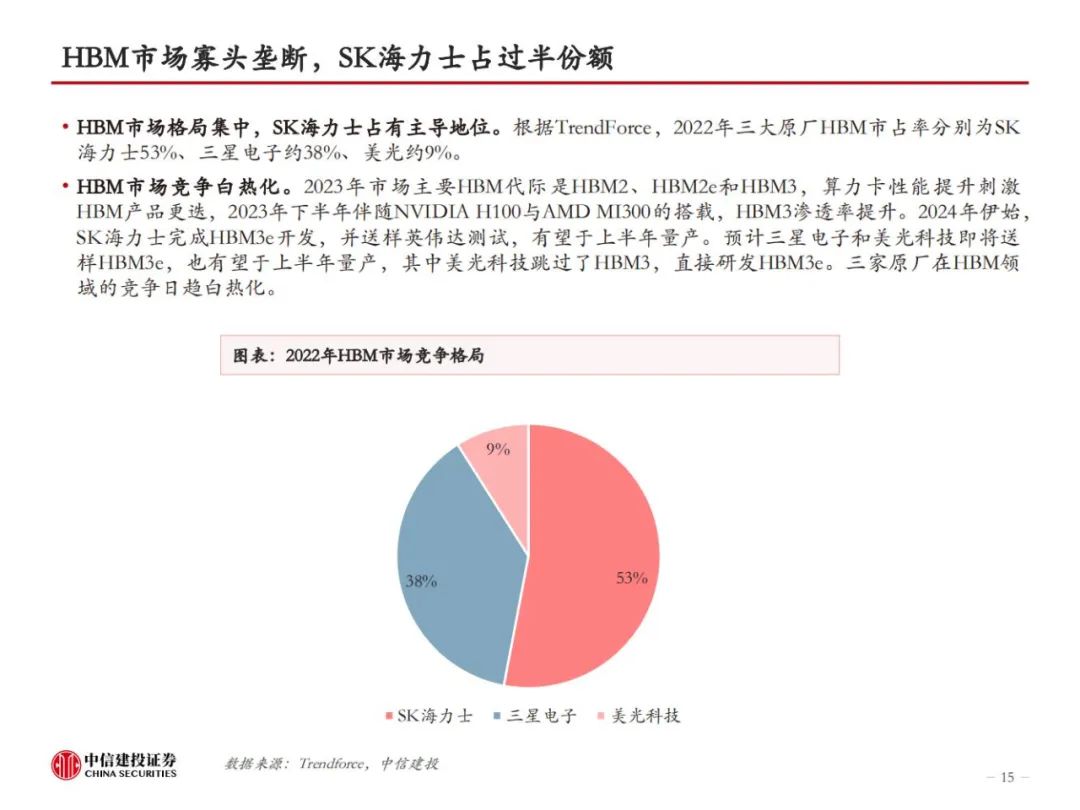

三大原厂持续加大研发投入,HBM性能倍数级提升。随着技术的迭代,HBM的层数、容量、带宽指标不断升级,目前最先进的HBM3e版本,理论上可实现16层堆叠、64GB容量和1.2TB/s的带宽,分别为初代HBM的2倍、9.6倍和4倍。从Trendforce公布的HBM Roadmap来看,2024年上半年,海力士、三星、美光均会推出24GB容量的HBM3e,均为8层堆叠。2024年下半年,三家厂商将推出36GB版本的HBM3e,或为12层堆叠。此外,HBM4有望于2026年推出。

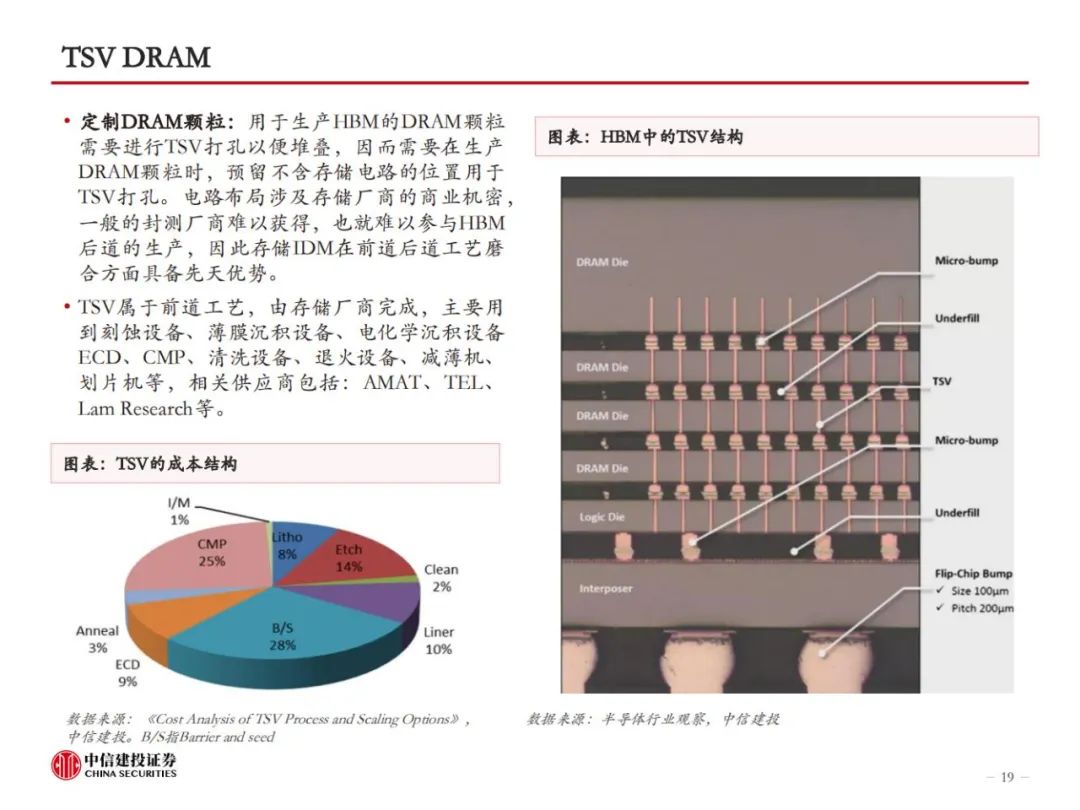

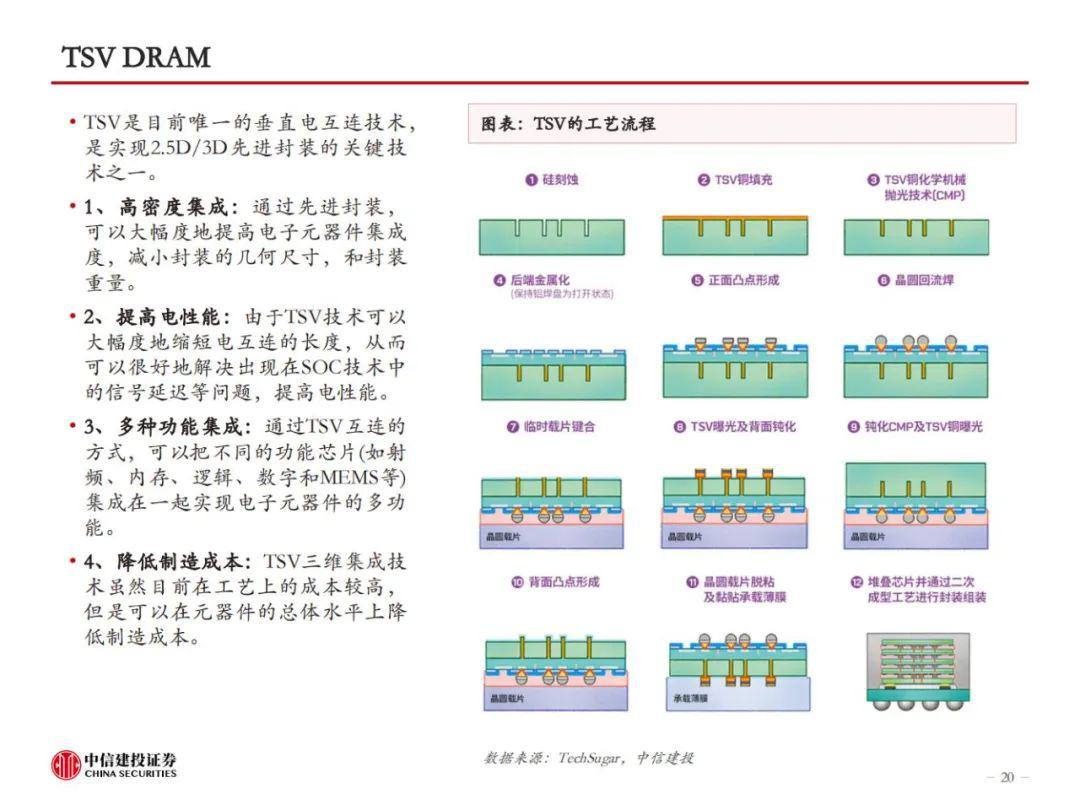

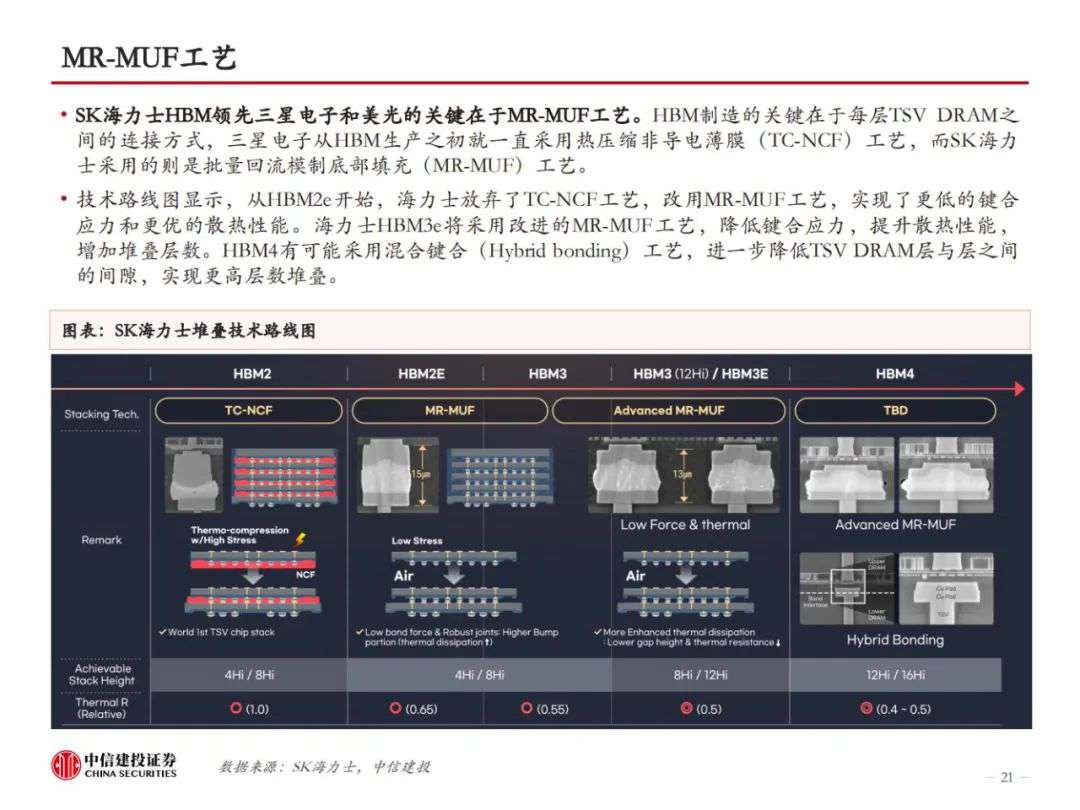

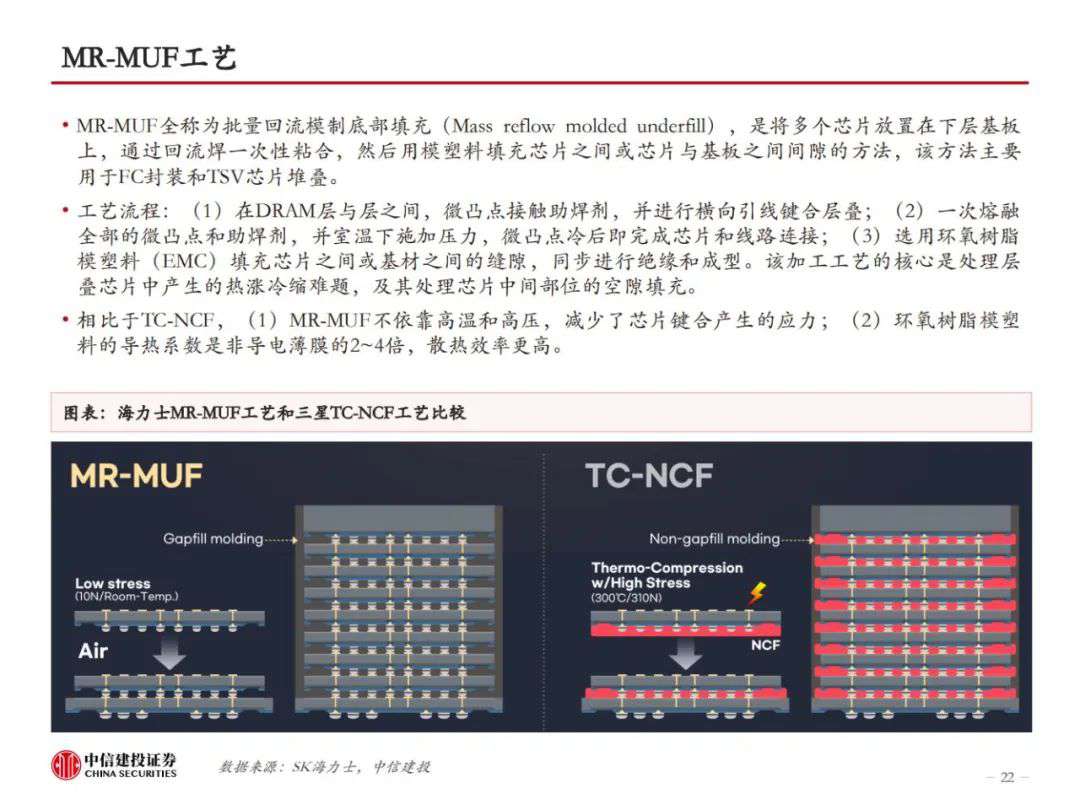

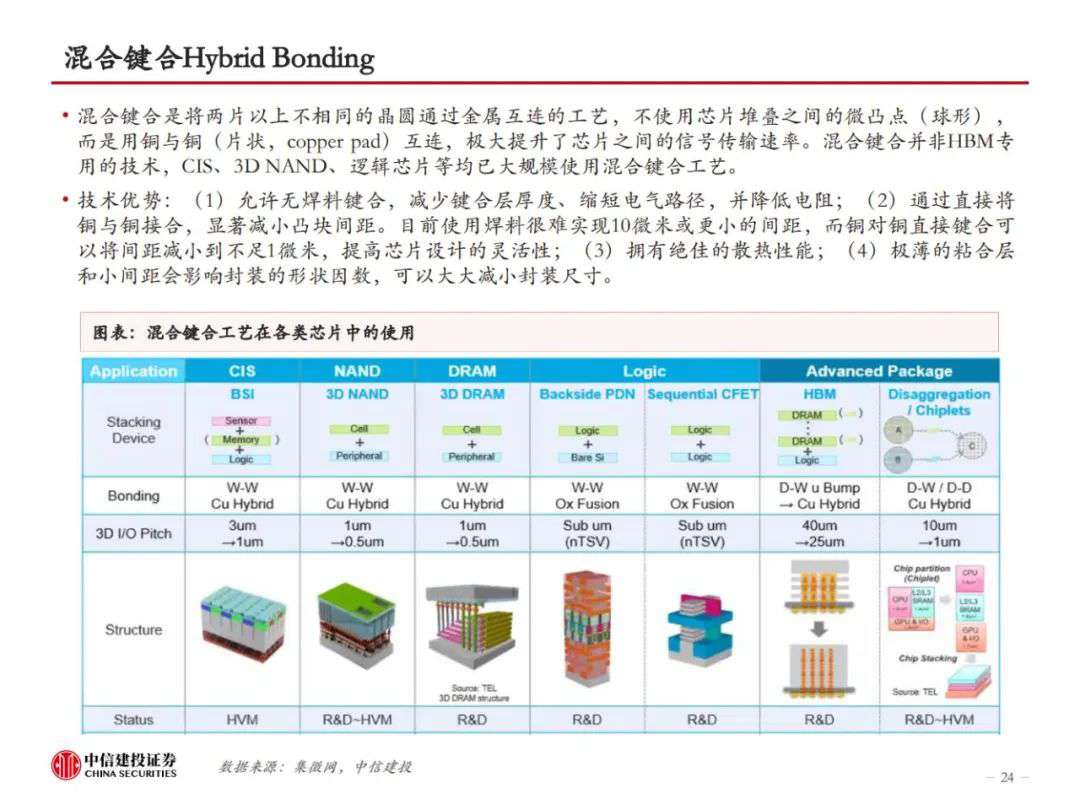

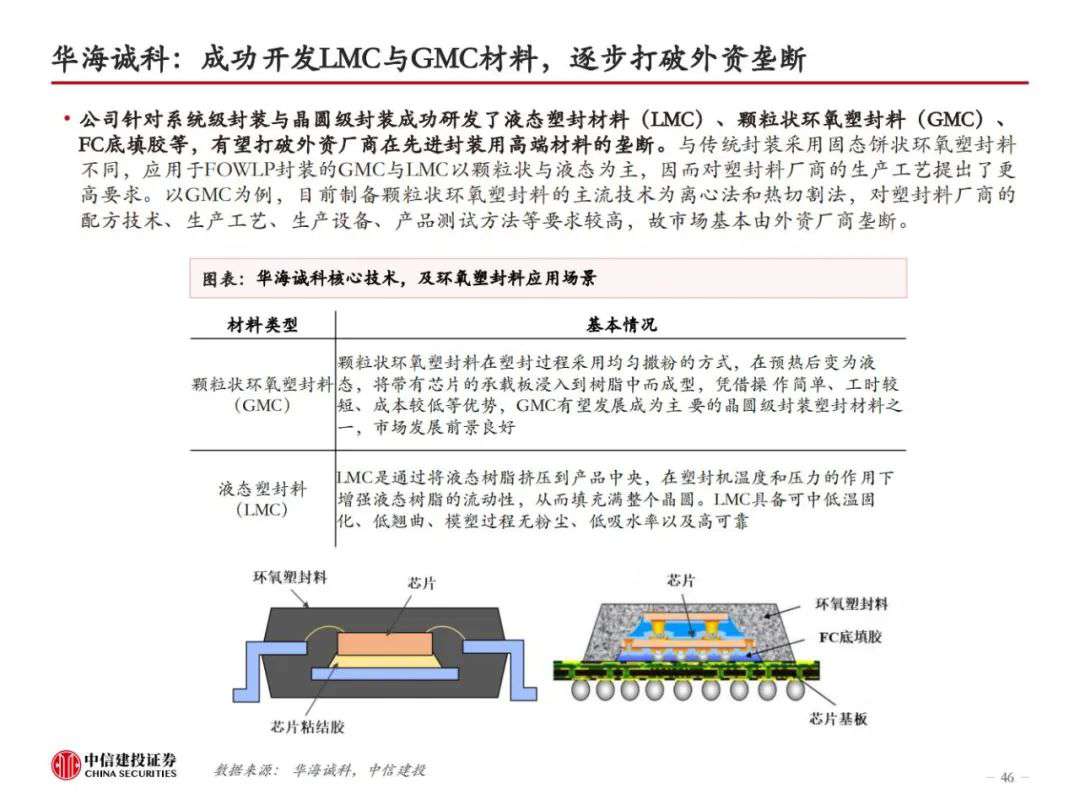

HBM制造集成前道工艺与先进封装,TSV、EMC、键合工艺是关键。HBM制造的关键在于TSV DRAM,以及每层TSV DRAM之间的连接方式。目前主流的HBM制造工艺是TSV+Micro bumping+TCB,例如三星的TC-NCF工艺,而SK海力士则采用改进的MR-MUF工艺,在键合应力、散热性能、堆叠层数方面更有优势。目前的TCB工艺可支撑最多16层的HBM生产,随着HBM堆叠层数增加,以及HBM对速率、散热等性能要求的提升,HBM4开始可能引入混合键合工艺,对应的,TSV、GMC/LMC的要求也将提高。

推荐

-

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

国民技术发布国内首款Arm® Cortex®M7+M4双核异构MCU 面向具身智能机器人

2025-04-19

-

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

黄仁勋中国行的背后,AI芯片暗战与英伟达生存博弈

2025-04-19

-

北京机器人传感器公司金钢科技数千万元Pre

北京机器人传感器公司金钢科技数千万元Pre

2025-04-19

-

光子 AI 处理器的核心原理及突破性进展

光子 AI 处理器的核心原理及突破性进展

2025-04-19

-

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

解决续航、网速痛点,Wi 7 PA杀入AI眼镜

2025-04-19

-

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

15万车型也能有车规SiC!2025年慕展6家厂商新品亮点大揭秘

2025-04-19

-

VCSEL芯片和光学解决方案提供商瑞识科技完成近亿元B1轮融资

VCSEL芯片和光学解决方案提供商瑞识科技完成近亿元B1轮融资

2023-07-03

-

算法进化论:从参数剪枝到意识解码的 AI 革命

算法进化论:从参数剪枝到意识解码的 AI 革命

2025-04-19

-

一文带你搞懂开关电源电路

一文带你搞懂开关电源电路

2024-11-02

-

基于脱硝系统改造的自动化优化分析

基于脱硝系统改造的自动化优化分析

2025-02-20

最近更新

-

研华AgentBuilder智能体平台推动智能制造发展

研华AgentBuilder智能体平台推动智能制造发展

2025-04-23

-

新能源汽车热管理系统,从电容、传感器到功率器件的全面创新

新能源汽车热管理系统,从电容、传感器到功率器件的全面创新

2025-04-23

-

奥托立夫助力长城魏牌全新高山重塑家庭出行安全范式

奥托立夫助力长城魏牌全新高山重塑家庭出行安全范式

2025-04-23

-

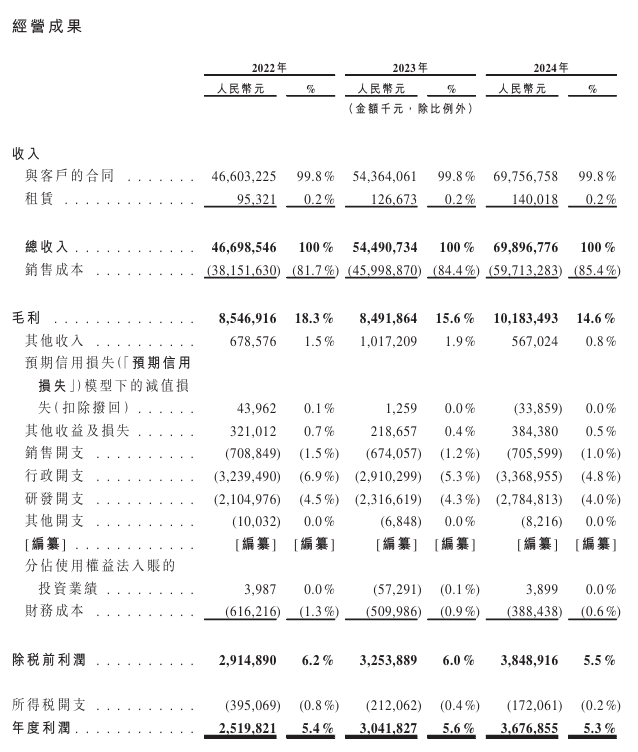

蓝思科技港股IPO破局:人形机器人+AI设备拓新赛道减"苹果依赖"

蓝思科技港股IPO破局:人形机器人+AI设备拓新赛道减"苹果依赖"

2025-04-23

-

上汽通用汽车别克品牌与Momenta达成战略合作

上汽通用汽车别克品牌与Momenta达成战略合作

2025-04-23

-

IBM发布2025年X

IBM发布2025年X

2025-04-23

-

比亚迪五款新能源车型登陆塞舌尔市场

比亚迪五款新能源车型登陆塞舌尔市场

2025-04-23

-

仰望汽车累计销量突破10000台

仰望汽车累计销量突破10000台

2025-04-23

-

中车时代电气出席2025年全路ATP车载设备技术交流会

中车时代电气出席2025年全路ATP车载设备技术交流会

2025-04-23

-

比亚迪海狮07EV荣获EURO NCAP和A

比亚迪海狮07EV荣获EURO NCAP和A

2025-04-23