概要:FPGA设计复杂性增加,测试和调试面临挑战。本文探讨通过内建自测试、扫描链插入和调试逻辑等方法优化FPGA测试和调试流程。内建自测试嵌入FPGA实现实时监测;扫描链插入简化测试流程;调试逻辑有效跟踪分析问题。结合示例代码,提高FPGA设计的可靠性和可维护性。

在飞速发展的电子系统时代,FPGA无疑是构建高性能、高可靠性系统的核心力量。然而,随着技术创新的脚步不断加快,FPGA设计的复杂性也随之攀升,给测试和调试流程带来了前所未有的挑战。但正是这些挑战,激发了我们对优化FPGA测试和调试流程的渴望。

想象一下,一个经过精心设计的FPGA系统,因为测试和调试流程的繁琐而延误了上市时间,甚至因潜在的问题而影响了最终产品的可靠性。这样的场景,对于每一个追求卓越的工程师来说,都是不愿意见到的。

因此,我们急需找到一种解决方案,来优化FPGA的测试和调试流程,从而确保系统的可靠性和可维护性。幸运的是,通过内建自测试、扫描链插入以及调试逻辑等先进技术,我们找到了这样的解决方案。

内建自测试能够自动检测FPGA中的潜在问题,而无需人工干预,大大提高了测试效率。扫描链插入技术则使得我们能够更加深入地了解FPGA的内部状态,从而及时发现并解决问题。而调试逻辑则为我们提供了一个强大的工具,帮助我们快速定位并修复错误。

接下来,我们将结合示例代码,详细探讨这些技术的实际应用。通过这些实例,您将看到如何轻松应对FPGA设计和调试中的挑战,让您的系统更加可靠、高效。

一、揭秘内建自测试:FPGA可靠性背后的强大支撑

在数字时代的浪潮中,FPGA如同一位灵活的舞者,在复杂多变的电子世界中自由穿梭。然而,在这看似无懈可击的优雅背后,却隐藏着一个重要的秘密——内建自测试。它不仅是FPGA可靠性的守护者,更是确保数据精确传输、系统稳定运行的坚强后盾。

想象一下,如果没有内建自测试,FPGA就如同失去了眼睛的舞者,无法及时发现并纠正潜在的问题。而有了内建自测试,FPGA便能在每次运行中自动检测并修复错误,确保数据的准确性和系统的稳定性。

那么,内建自测试是如何工作的呢?简单来说,它通过在FPGA内部设置专门的测试电路,对关键模块和连接进行定期或实时的检查。一旦发现异常,便会立即触发相应的修复机制,确保系统能够继续正常运行。

在这个信息爆炸的时代,FPGA的可靠性对于各行各业都至关重要。无论是通信、医疗、金融还是航空航天领域,都需要依靠FPGA来实现高速、高精度的数据处理和传输。而内建自测试作为FPGA可靠性的重要保障,其重要性不言而喻。

因此,我们可以说,内建自测试是FPGA可靠性背后的强大支撑。它让我们能够放心地将关键任务交给FPGA去完成,同时也为数字时代的发展提供了坚实的保障。

内建自测试——FPGA的守护者,无需外部设备的智能检测先锋!

在FPGA设计的浩渺星空中,内建自测试宛如一颗璀璨的明星,默默守护着每一颗FPGA芯片的功能与性能。它不仅仅是一段简单的测试逻辑,更是FPGA设计可靠性的坚实后盾。

无需借助任何外部测试设备的繁琐与限制,BIST能在FPGA内部实时、自主地进行功能测试和故障检测。它犹如一位机智的侦探,时刻关注着FPGA的工作状态,一旦发现任何潜在的问题或隐患,便立即发出警报,确保问题的及时发现与准确定位。

在FPGA的复杂世界中,BIST的存在意味着更高的可靠性、更低的故障率。它让FPGA芯片更加稳健、更加可靠,为各种应用场景提供了坚实的保障。因此,让我们为BIST这位FPGA的守护者点赞,为它的智慧与力量喝彩!

在FPGA设计的宏伟画卷中,实现内建自测试犹如为这座大厦注入了一颗智能的心脏。在这颗心脏的驱动下,FPGA内部巧妙地嵌入了测试逻辑,这些逻辑不仅拥有强大的生命力,更具备敏锐的洞察力。它们如同一位位技艺高超的工匠,运用伪随机数生成器、特征分析器、比较器等工具,精心打造着测试激励,深入分析着测试响应,并精准地比较着预期结果与实际结果。

正是这些测试逻辑的存在,让内建自测试得以在FPGA运行的每一个瞬间自动展开其神奇的工作。它们如同一位位不知疲倦的守护者,时刻关注着FPGA的健康状况,实时报告着测试结果,确保FPGA持续稳定地运行。因此,内建自测试不仅是FPGA设计中不可或缺的一部分,更是其性能卓越、可靠性高的重要保障。

二、无缝融入扫描链:为FPGA内部逻辑测试注入新动力

在当今高度集成的电子世界中,FPGA已成为设计工程师们的得力助手。然而,随着内部逻辑的日益复杂,如何高效地对其进行测试和验证,已成为了一个亟待解决的难题。幸运的是,通过巧妙地插入扫描链,我们为FPGA内部逻辑的测试带来了全新的解决方案。

扫描链,这一简单而强大的工具,就像是为FPGA内部逻辑测试量身打造的“绿色通道”。通过精心设计和布局,我们可以将扫描链无缝融入FPGA的每一个角落,轻松访问并控制其内部的所有逻辑单元。这不仅简化了测试流程,还大大提高了测试的准确性和效率。

想象一下,在FPGA内部逻辑的海洋中,扫描链就像是一艘灵活的船只,能够轻松穿梭于各个逻辑单元之间。无论是查找潜在的问题,还是验证设计的正确性,扫描链都能迅速而准确地完成任务。这不仅大大缩短了产品上市的时间,还确保了最终产品的质量和稳定性。

因此,不要再让复杂的FPGA内部逻辑测试成为你的困扰。借助扫描链的强大力量,让我们共同为FPGA内部逻辑的测试注入新的动力,迈向更加高效、准确和可靠的未来!

揭秘FPGA测试的秘密武器:扫描链插入技术

在FPGA设计的深邃海洋中,有一项被业界誉为“秘密武器”的技术——扫描链插入。这项技术不仅为FPGA的内部逻辑测试带来了革命性的简化,更使得测试过程变得高效而精准。

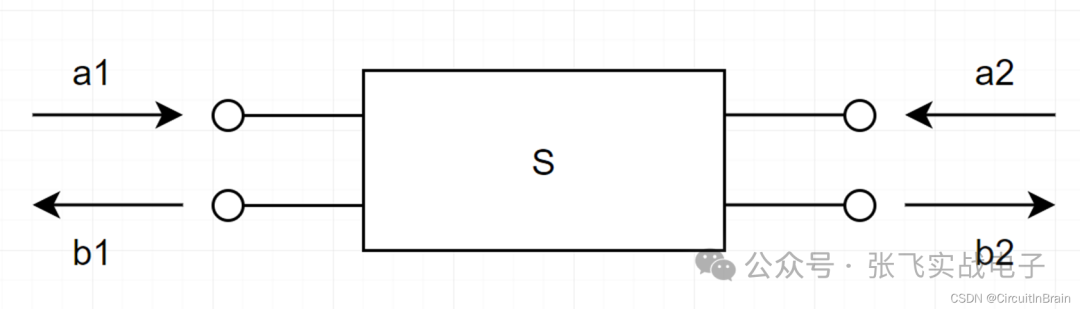

想象一下,FPGA内部的寄存器、触发器等元件如同一座座孤岛,而扫描链插入技术就是连接这些孤岛的桥梁。通过精心设计的扫描链,这些原本独立的元件被巧妙地串联成一条或多条扫描链。这样,只需通过扫描链的输入和输出端口,就可以轻松地对整个FPGA进行全方位的测试。

这项技术的神奇之处在于,它使得测试过程变得简单而直观。无需复杂的操作,也无需专业的知识背景,只需通过简单的指令,就可以对整个FPGA进行全面的检测。这不仅提高了测试的效率,也降低了测试的成本,使得FPGA的设计更加灵活和高效。

所以,当你再次面对FPGA设计的挑战时,不妨试试扫描链插入技术这把“秘密武器”,相信它会给你带来意想不到的惊喜!

🔍 扫描链插入:简化复杂,提升测试新境界

在FPGA的广阔世界中,测试一直是一个至关重要的环节。而扫描链插入技术的出现,就如同为这片浩瀚领域带来了一股清新的风,将那些错综复杂的内部逻辑化繁为简,变为一系列轻松的扫描操作。

🌟 降低测试复杂性

想象一下,原本需要穿越重重迷雾、历经千难万险的测试流程,现在因为有了扫描链插入,一切都变得如此简单直接。复杂的FPGA内部逻辑被巧妙地简化为一系列直观的扫描操作,使得测试人员能够轻松驾驭,游刃有余。

🔍 逐一测试,确保万无一失

不仅如此,扫描链插入还赋予了测试人员更强大的能力——对FPGA内部元件进行逐一测试。这意味着每一个微小的元件都将被精心检查,确保没有任何疏漏。这样的测试方式不仅提高了测试的覆盖率,更在无形中增强了测试的准确性,为FPGA的稳定运行提供了坚实的保障。

🚀 迈向更高峰,测试新篇章

扫描链插入技术的出现,无疑为FPGA的测试领域开启了一个全新的篇章。它以其独特的优势,引领着测试技术的不断发展,让FPGA的性能得到更加全面、深入的验证。让我们一起期待,在这股力量的推动下,FPGA的测试领域将会迈向更高的巅峰!

三、深入探索调试逻辑:精准追踪与细致分析FPGA问题的奥秘

在当今高科技迅猛发展的时代,FPGA作为数字系统设计的核心组件,其稳定性和性能对于整个系统的成功运行起着至关重要的作用。然而,面对FPGA设计中可能出现的各种复杂问题,如何高效、准确地进行问题跟踪和分析,成为每位工程师都必须面对的挑战。

一、精确锁定问题源头

在FPGA的调试过程中,首要任务是快速而准确地锁定问题的源头。通过精细的调试逻辑设计,我们能够深入到FPGA的内部结构,逐一排查可能的问题点,确保问题被精准地定位。

二、细致分析问题成因

一旦问题被锁定,接下来的任务就是细致地分析问题的成因。通过收集和分析FPGA在运行过程中的各种数据,我们能够深入了解问题的本质,为后续的解决方案提供有力的依据。

三、高效解决FPGA问题

在深入分析和理解问题的基础上,我们能够提出针对性的解决方案,高效地解决FPGA问题。这不仅能够确保系统的稳定运行,还能够提升整个系统的性能和可靠性。

总之,通过深入探索调试逻辑,我们能够精准追踪与细致分析FPGA问题的奥秘,为数字系统设计的成功运行提供有力的保障。让我们一起努力,不断提升FPGA设计的稳定性和性能!

在FPGA的深邃世界里,巧妙地融入调试逻辑,无疑是实现精准问题追踪与透彻分析的黄金钥匙。想象一下,这些调试逻辑就如同灵敏的信号探针与犀利的监视器,悄无声息地潜伏在FPGA的运行脉络中,时刻准备着捕捉那些至关重要的信号状态。当FPGA的脉搏跳动时,它们便精确地将这些宝贵的数据传递至外部设备,以供我们进行深入的研究与剖析。

无需繁复的操作,无需漫长的等待,只需这些精心设计的调试逻辑,我们就能轻松掌握FPGA的运行奥秘,为每一次设计与创新提供坚实的保障。因此,让我们珍视这些调试逻辑,让它们在我们的FPGA设计中熠熠生辉,引领我们走向更加精准、高效的设计之路。

在FPGA的舞动世界中,开发人员如同拥有了一双透视之眼。通过精心编织的调试逻辑,他们能在FPGA运行之际,实时捕捉到关键信号那微妙的起伏与跃动,使得潜在问题无处遁形。这一独特的洞察力,让问题定位与分析变得轻而易举,仿佛手握一把精准的导航仪,在复杂的逻辑迷宫中轻松找到出路。

而调试逻辑所展现的,不仅仅是问题的踪迹,更是一幅生动的FPGA工作状态图。它提供了详尽而丰富的调试信息,让开发人员能够深入探索FPGA的内心世界,理解其每一次的脉动与呼吸。在这个过程中,开发人员与FPGA之间建立起了一种前所未有的默契,共同编织出更加完美的逻辑乐章。

四、跃入代码世界:打造无懈可击的自测与调试逻辑

在编程的海洋中遨游,一个稳固的罗盘是必不可少的。而在这篇文章中,我们将深入探讨如何为您的代码装备上那枚不可或缺的罗盘——内建自测试和调试逻辑。

想象一下,当您的代码像一艘巨轮般在数据的海洋中破浪前行,内建的自测试系统就如同船上的雷达,时刻扫描着潜在的暗礁和冰山。而调试逻辑,则是那灵活的舵手,随时准备调整方向,确保巨轮能够顺利航行。

现在,让我们一起揭开这层神秘的面纱,看看如何将这些强大的功能融入您的代码中。通过精心设计的自测用例,我们可以确保代码的每一个部分都经过了严格的检验。而调试逻辑,则能在代码出现偏差时,迅速定位问题所在,并给出解决方案。

让我们一起驾驭代码,打造无懈可击的程序吧! 无需担心代码的稳健性和可靠性,因为内建的自测试和调试逻辑将为您保驾护航。

在这片代码的海洋深处,隐藏着一段魔法般的代码,它赋予了FPGA设计的神奇能力——内建自测试和调试逻辑。这不仅是一段简单的代码,更是工程师们智慧的结晶,是创新与技术的完美融合。

想象一下,当你面对一个复杂的FPGA设计时,如同探索一片未知的森林,内建自测试和调试逻辑就像是手中的指南针和地图,帮助你轻松找到方向,避开陷阱。它能在设计过程中自动检测错误,提供即时的反馈,让你的设计之路更加顺畅。

以下,就是这段魔法代码的简化示例。它静静地躺在那里,等待着你去发掘它的奥秘,去感受它的力量。它不仅仅是一段代码,更是一种信念,一种追求完美的执着。

我们用心编辑,只为给您带来更好的阅读体验。让我们一起,用文字点亮生活,用思想照亮未来!

在FPGA设计的深邃领域中,我们精心呈现了一种革命性的实现方法——内建自测试和调试逻辑。想象一下,您的FPGA设计如同一个复杂的机械钟表,而内建自测试逻辑则是其内置的精密检测器。它不仅能够自主生成测试激励,如一把犀利的探针,深入探索设计的每个角落;还能捕获测试响应,犹如一只敏锐的耳朵,倾听每一个信号的回音。更为神奇的是,它能够实时比较预期结果与实际结果,确保FPGA的稳定运行如同钟表般精准。

而调试逻辑,则像是为FPGA配备了一双透视眼。它能够捕捉关键信号的状态,并将其清晰地展现在外部设备上,让您轻松洞悉设计的内在运作。这种直观的分析方式,让问题定位变得轻而易举,也让复杂的设计问题迎刃而解。

通过这两种强大工具的结合,我们为FPGA设计注入了前所未有的可靠性和可维护性。无论是追求卓越性能,还是确保稳定运行,内建自测试和调试逻辑都将是您不可或缺的得力助手。让我们一起探索FPGA的无限可能,共创美好未来!