在现代计算领域,算法硬件加速已成为提升系统性能的关键技术之一。现场可编程门阵列(FPGA)作为高性能计算平台,凭借其并行处理能力和可重构性,在算法硬件加速方面展现出巨大潜力。本文将深入探讨FPGA实现算法硬件加速的方法与详细步骤,并结合示例代码进行说明,旨在为读者提供一套完整的实践指南。

FPGA算法硬件加速的基本原理

FPGA算法硬件加速的核心在于将算法映射到硬件电路上,通过并行处理和流水线技术等手段,实现计算效率的显著提升。相较于传统的CPU或GPU,FPGA能够更直接地控制数据流动和计算过程,从而避免不必要的指令开销和内存访问延迟。

实现方法与步骤

1. 算法分析与分解

首先,需要对目标算法进行深入分析,明确其计算流程和关键路径。在此基础上,将算法分解为可并行处理的子任务,为后续的硬件实现奠定基础。

2. 硬件架构设计

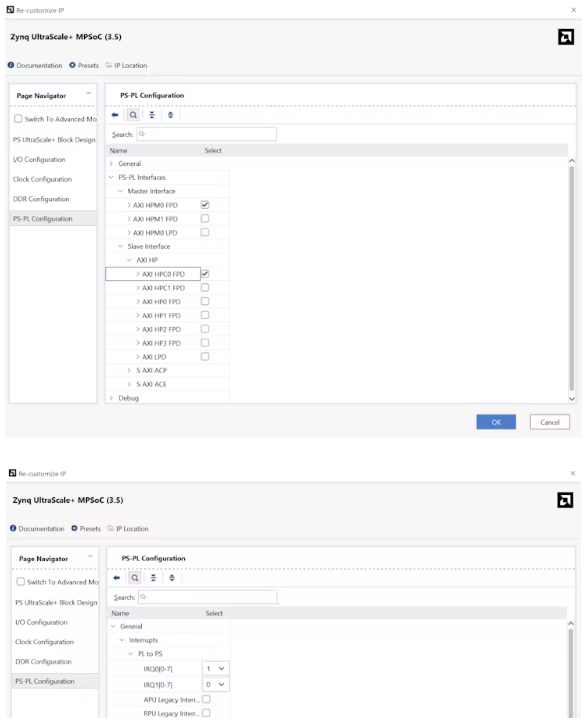

根据算法分解结果,设计FPGA的硬件架构。这包括确定所需的逻辑单元(如加法器、乘法器等)、数据存储器(如FIFO、RAM等)以及它们之间的连接方式。在设计过程中,需充分考虑资源的利用率和性能需求。

3. Verilog/VHDL编码

使用Verilog或VHDL等硬件描述语言,将设计好的硬件架构转化为可综合的代码。编码过程中,需注重代码的可读性和可维护性,同时确保逻辑功能的正确性。

示例代码(Verilog)

以下是一个简单的矩阵乘法算法的Verilog实现示例:

verilog

module MatrixMul(

input clk,

input rst,

input [31:0] A[0:3][0:3], // 输入矩阵A

input [31:0] B[0:3][0:3], // 输入矩阵B

output reg [31:0] C[0:3][0:3] // 输出矩阵C

);

// 初始化输出矩阵C

integer i, j, k;

always @(posedge clk or posedge rst) begin

if (rst) begin

for (i = 0; i < 4; i = i + 1) begin

for (j = 0; j < 4; j = j + 1) begin

C[i][j] <= 0;

end

end

end else begin

// 矩阵乘法计算

for (i = 0; i < 4; i = i + 1) begin

for (j = 0; j < 4; j = j + 1) begin

C[i][j] <= 0;

for (k = 0; k < 4; k = k + 1) begin

C[i][j] <= C[i][j] + A[i][k] * B[k][j];

end

end

end

end

end

endmodule

注意:上述代码为简化示例,未考虑流水线优化和性能瓶颈。在实际应用中,需根据具体算法和FPGA资源进行优化。

4. 综合与仿真

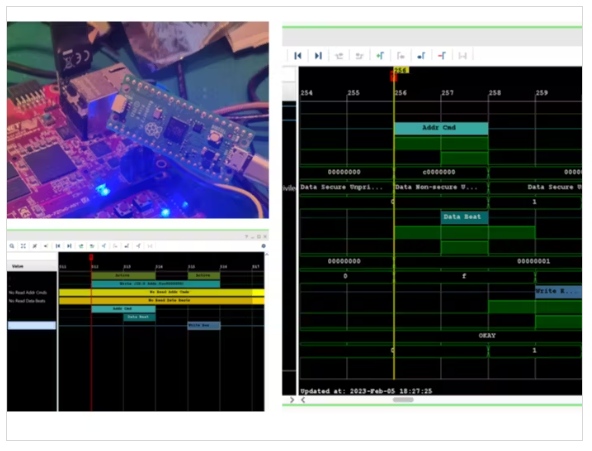

使用FPGA综合工具(如Xilinx Vivado、Altera Quartus等)对Verilog代码进行综合,生成相应的比特流文件。随后,通过仿真工具验证设计的正确性,确保硬件电路能够正确执行算法。

5. 硬件调试与优化

将比特流文件下载到FPGA开发板上,进行硬件调试。根据调试结果,对硬件架构和代码进行优化,以提高性能和资源利用率。优化策略可能包括增加流水线级数、调整数据宽度和存储结构等。

结论

FPGA算法硬件加速是一项复杂但极具挑战性的任务。通过深入分析算法、精心设计硬件架构、精确编码以及综合仿真与优化,可以实现高性能的硬件加速器。随着FPGA技术的不断进步和算法复杂度的日益增加,FPGA算法硬件加速将在更多领域展现出其独特的优势和广阔的应用前景。