在现代电子系统中,模数转换器(ADC)扮演着将模拟信号转换为数字信号的重要角色。而现场可编程门阵列(FPGA)则以其灵活性和高性能成为众多应用中不可或缺的一部分。本文将探讨如何通过FPGA驱动AD芯片,并实现与AD芯片的高效通信。

一、引言

AD芯片,如TLC549,是一种高性能、低成本的8位模数转换器。它通过逐次逼近的方法实现A/D转换,具有转换速度快、功耗低等特点。FPGA,作为可编程逻辑器件,能够在硬件层面实现复杂的时序控制和数据处理功能,是驱动AD芯片的理想选择。

二、硬件基础

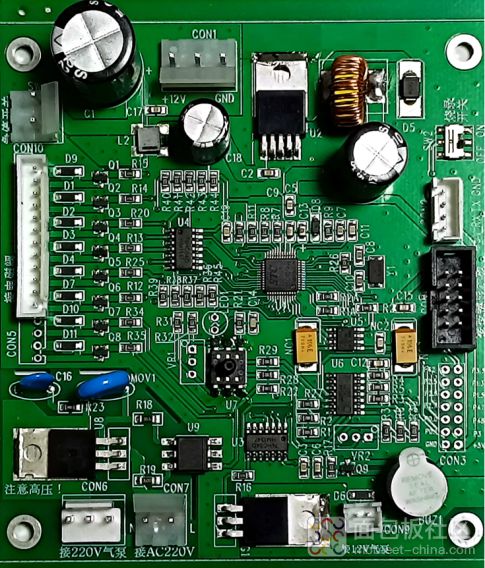

在FPGA驱动AD芯片的系统中,关键的硬件组件包括FPGA芯片、AD芯片以及必要的电源、时钟和接口电路。

FPGA芯片:本文示例中采用的是Altera的Cyclone IV E系列FPGA,具体型号为EP4CE10F17C8。该FPGA具有丰富的逻辑资源和高速的I/O接口,能够满足驱动AD芯片的需求。

AD芯片:本文选用的是TI公司生产的TLC549。这款AD芯片具有8位分辨率,最大转换时间为17微秒,转换速率为每秒40000次。它采用三线串行接口与微处理器连接,方便FPGA进行通信。

电源和时钟:FPGA和AD芯片都需要稳定的电源供应。同时,为了精确控制时序,需要提供合适的时钟信号。在本文的示例中,FPGA的时钟频率为50MHz,而AD芯片的I/O CLOCK频率被设置为1MHz。

三、实现步骤

时序分析与设计:

当AD芯片的片选信号CS为高时,数据输出端DATA OUT处于高阻态,此时I/O CLOCK不起作用。

当CS为低时,AD前一次转换的数据的最高位立即出现在DATA OUT上,其余7位数据在I/O CLOCK的下降沿依次输出。

读完8位数据后,AD开始转换下一帧数据。转换时CS必须置高电平,每次转换的时间不超过17微秒。

Verilog代码编写:

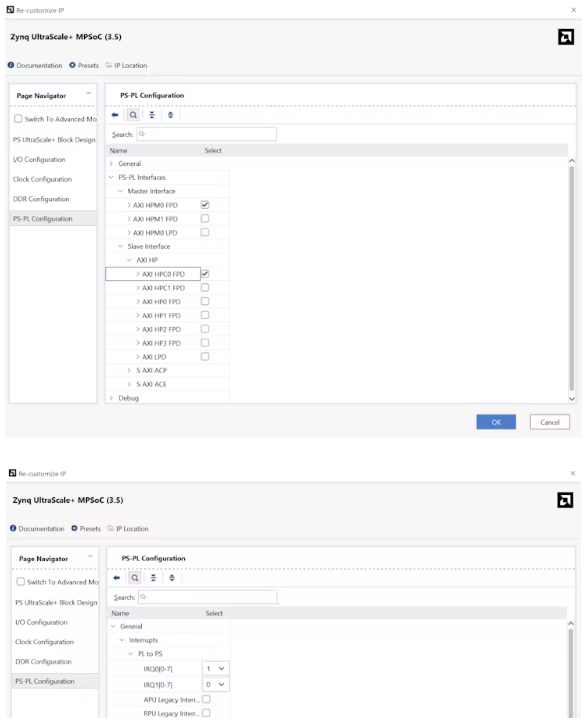

根据时序图,编写Verilog代码来实现FPGA对AD芯片的驱动和数据采集。代码需要包括状态机的设计,用于控制CS和I/O CLOCK信号的时序。

在状态机中,需要定义不同的状态,如等待CS信号变低、读取数据、等待AD转换完成等。在每个状态下,根据时钟信号和计数器来控制信号的输出。

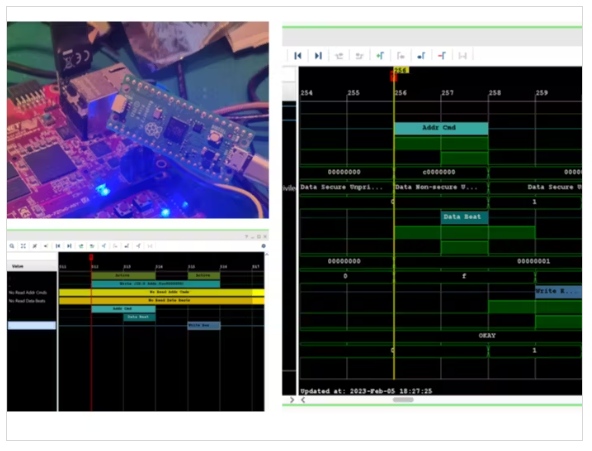

仿真与验证:

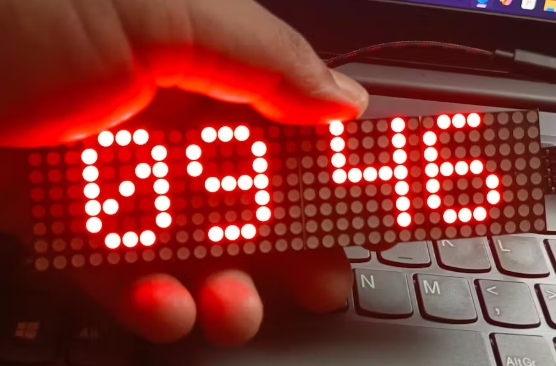

使用Quartus-Ⅱ等FPGA开发软件对编写的Verilog代码进行仿真。通过SignalTapⅡ等工具观察波形,验证时序和数据的正确性。

仿真结果应显示FPGA能够正确地驱动AD芯片,并在指定的时序下采集到数据。

硬件调试:

将编写好的FPGA程序下载到FPGA芯片中,进行硬件调试。

使用示波器、逻辑分析仪等工具监测FPGA和AD芯片之间的信号交互,确保通信的稳定性和数据的准确性。

四、应用与展望

FPGA驱动AD芯片的实现不仅限于本文所讨论的示例。在实际应用中,可以根据具体需求选择不同的FPGA和AD芯片型号,以及相应的接口和时序设计。

此外,随着技术的不断发展,FPGA和AD芯片的性能也在不断提升。未来,可以期待更高分辨率、更快转换速度的AD芯片与更强大的FPGA相结合,实现更复杂、更高效的信号处理系统。

五、结论

本文通过详细探讨FPGA驱动AD芯片的实现过程,展示了如何通过精确的时序控制和Verilog代码编写来实现与AD芯片的高效通信。这一技术在众多领域中具有广泛的应用前景,为电子系统的性能提升和成本降低提供了有力的支持。