自动饮料售卖机作为一种自助式零售设备,近年来在国内外得到了广泛应用。本文将详细介绍一款功能完善、操作简便的自动饮料售卖机的设计与实现过程,包括有限状态机(FSM)的设计、Verilog编程、以及设计工程中可使用的工具及大致过程。

一、有限状态机(FSM)设计

在设计自动饮料售卖机时,有限状态机(FSM)是一种非常有效的工具,用于描述具有逻辑顺序和时序顺序的事件。在本设计中,饮料的价格为10分钱,硬币有5分和10分两种,同时需要考虑找零功能。

我们定义两个状态:

S0:没有投钱

S1:投了5分

状态机的转移逻辑如下:

在S0状态,如果投入5分(a=1, b=0),则转移到S1状态。

在S0状态,如果投入10分(a=0, b=1),则直接出饮料并找零,保持S0状态。

在S1状态,如果再次投入5分(a=1, b=0),则总金额为10分,出饮料并找零,返回到S0状态。

在S1状态,如果投入10分(a=0, b=1),则总金额为15分,出饮料并找零,返回到S0状态。

FSM的状态转移图如下所示:

S0 ----(a=1, b=0)---- S1

| |

|(a=0, b=1) 出饮料,找零|

V V

S0 <-------------------

二、Verilog编程

基于上述FSM设计,我们使用Verilog编写自动饮料售卖机的控制逻辑。在FPGA设计中,Verilog是一种广泛使用的硬件描述语言,能够描述数字系统硬件的结构和行为。

verilog

module vending_machine(

input clk,

input rst_n,

input a, // 5分硬币输入

input b, // 10分硬币输入

output reg y, // 出饮料信号

output reg z // 找零信号

);

reg CS, NS; // 当前状态(CS)和下一状态(NS)

parameter S0 = 1'b0;

parameter S1 = 1'b1;

// 同步时序描述状态转移

always @(posedge clk or negedge rst_n) begin

if (!rst_n)

CS <= S0;

else

CS <= NS;

end

// 使用组合逻辑判断转移状态条件

always @(*) begin

NS = 1'bz; // 初始化不定态

case (CS)

S0: begin

if (a & ~b) // 投入5分

begin

{y, z} = 2'b00;

NS = S1;

end

else if (~a & b) // 投入10分

begin

{y, z} = 2'b10; // 出饮料,找零

NS = S0;

end

end

S1: begin

if (a & ~b) // 再次投入5分

begin

{y, z} = 2'b10; // 出饮料,找零

NS = S0;

end

else if (~a & b) // 投入10分

begin

{y, z} = 2'b11; // 出饮料,不找零(多投了5分)

NS = S0;

end

end

default: NS = S0;

endcase

end

endmodule

三、设计工程中可使用的工具及设计大致过程

在设计自动饮料售卖机的过程中,需要使用一系列工具和设计方法,以确保项目的顺利进行。以下是设计过程中可能使用的工具及大致流程:

功能定义与器件选型:

确定自动饮料售卖机的功能需求,如用户友好性、多样化商品支持、支付方式多样化等。

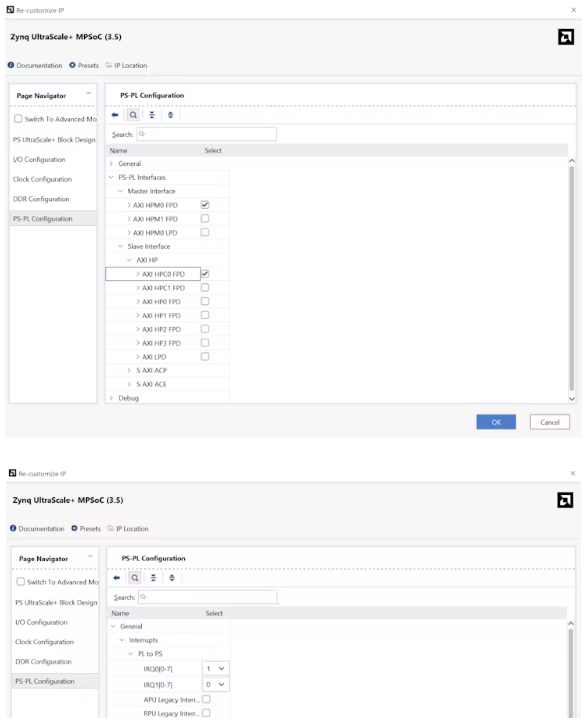

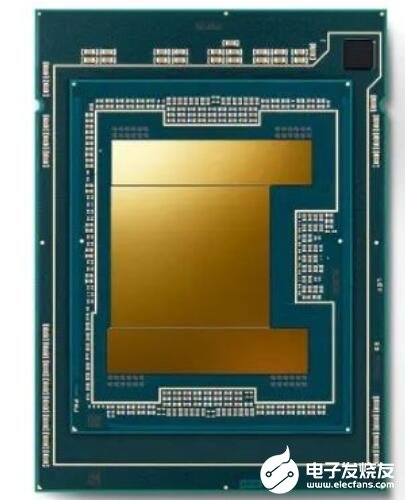

选择适当的硬件器件,如FPGA芯片、传感器、电机等。

设计输入:

使用EDA工具(如Ultra)进行原理图设计或HDL代码输入。

功能仿真:

使用ModelSim等工具进行功能仿真,验证设计逻辑的正确性。

逻辑综合:

使用Quartus II或ISE的逻辑综合器将HDL代码转换为门级网表。

实现布局布线:

使用Pin Planner等工具进行FPGA的布局布线设计。

时序仿真:

再次使用ModelSim等工具进行时序仿真,验证设计在实际硬件环境中的表现。

静态时序仿真:

使用TimeQuest等工具进行静态时序分析,确保设计满足时序要求。

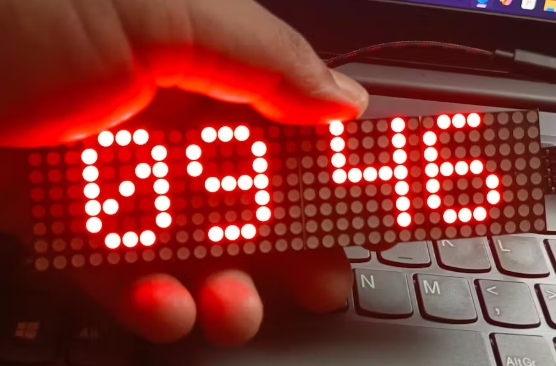

上板调试:

使用Quartus的SignalTap或ISE的ChipScope等工具进行硬件调试,确保设计在实际FPGA芯片上正确运行。

通过以上步骤,我们可以实现一款功能完善、操作简便的自动饮料售卖机。该设计不仅考虑了用户的使用习惯和需求,还充分利用了FPGA技术的灵活性和并行处理能力,为自动售货机市场的发展提供了有力的支持。